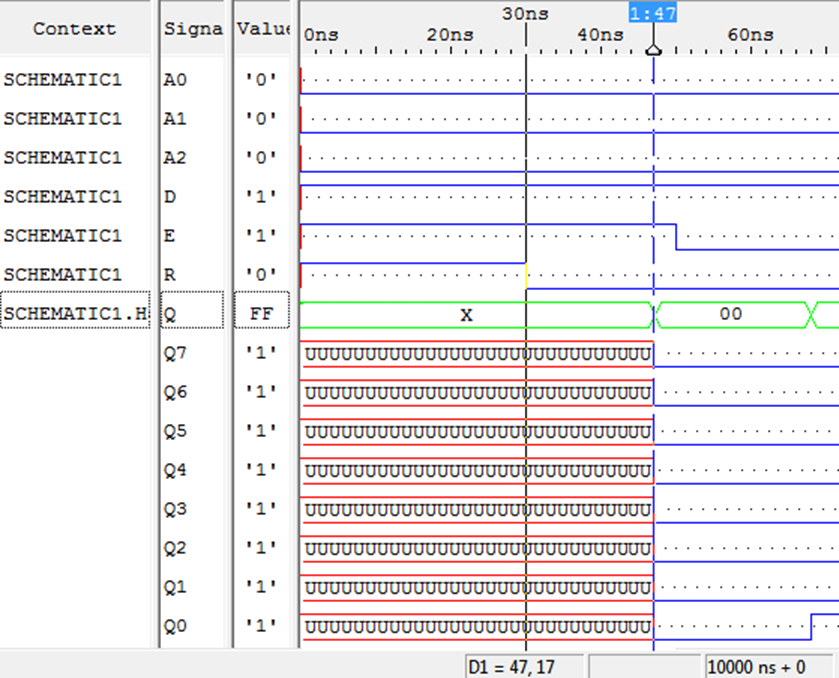

Рис.18. Задержка распространения сигнала от входа R до выхода Q при переключении его из 1 в 0 (17 нс).

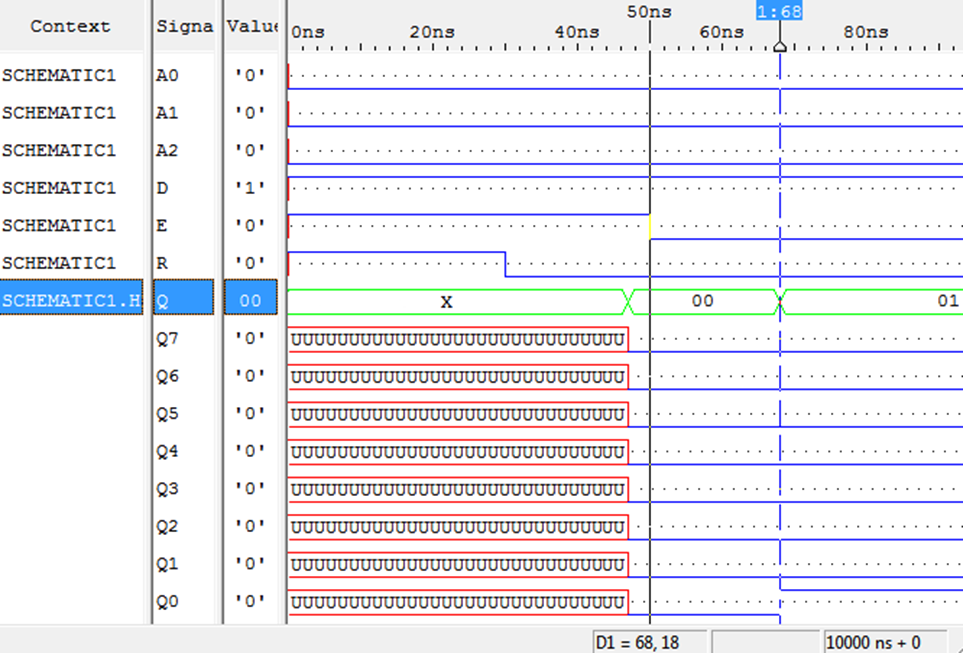

Рис.19. Задержка распространения сигнала от входа E до выхода Q при переключении его из 1 в 0 (18 нс).

Рис.20. Задержка распространения сигнала от входа E до выхода Q при переключении его из 0 в 1 (19 нс).

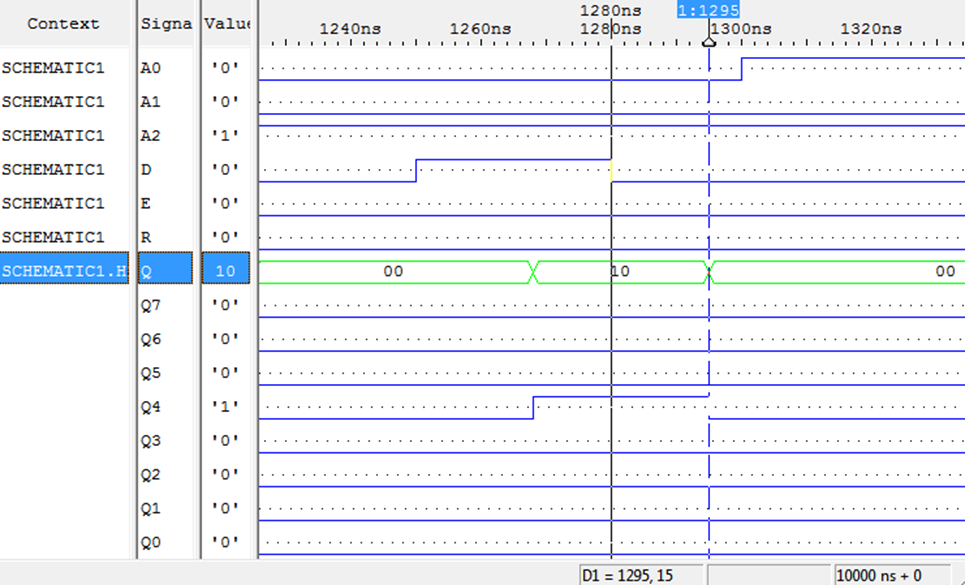

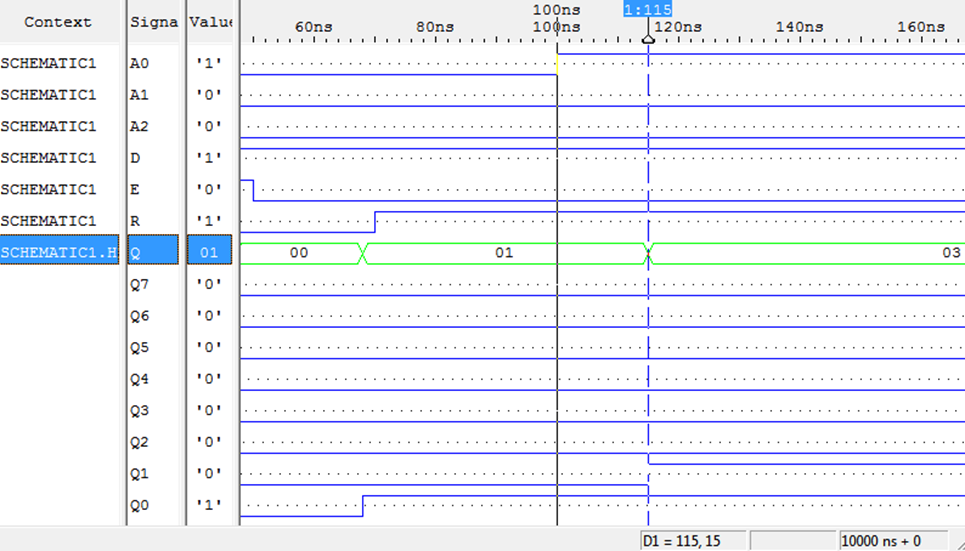

Рис.21. Задержка распространения сигнала от входа D до выхода Q при переключении его из 1 в 0 (15 нс).

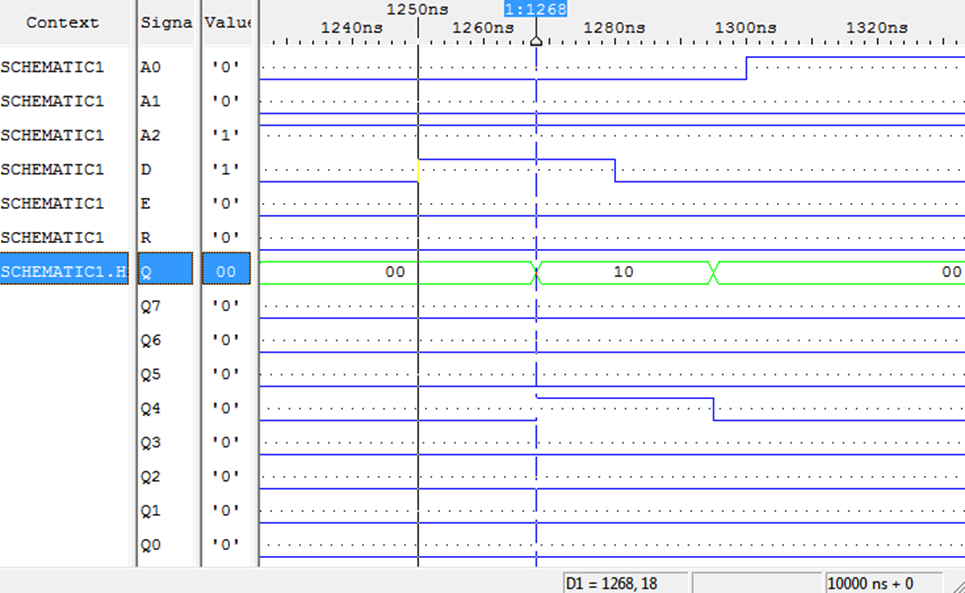

Рис.22. Задержка распространения сигнала от входа D до выхода Q при переключении его из 0 в 1 (18 нс).

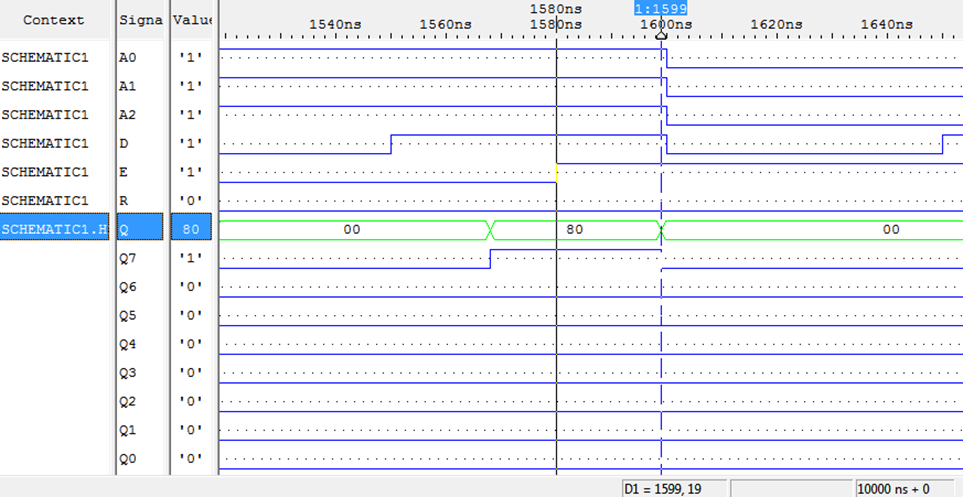

Рис.23. Задержка распространения сигнала от входа A до выхода Q при переключении его из 0 в 1 (15 нс).

Поведенческая модель описывает все режимы работы проектируемого узла. VHDL - код поведенческой модели представлен в листинге 3.

Листинг 3. Поведенческая модель проектируемого узла.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

entity K555IR30_VHDL is

port(

D,R,E,A0,A1,A2 : in STD_LOGIC;

Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7 : out STD_LOGIC);

end K555IR30_VHDL;

architecture K555IR30_VHDL of K555IR30_VHDL is

signal Qt : std_logic_vector(7 downto 0);

begin

PROCESS (D,R,E,A0,A1,A2,Qt)

variable A : std_logic_vector(2 downto 0);

BEGIN

A:=A2&A1&A0;

if E='1' then

if (R'event and R='0') then Qt<="00000000" after 17 ns;

elsif (E'event and R='0') then Qt<="00000000" after 19 ns;

end if;

else

if R='0' then --Режим дешифратора

if D='0' then Qt<="00000000" after 15 ns;

else

if A="000" then

Qt<="00000001" after 18 ns;

elsif A="001" then

Qt<="00000010" after 18 ns;

elsif A="010" then

Qt<="00000100" after 18 ns;

elsif A="011" then

Qt<="00001000" after 18 ns;

elsif A="100" then

Qt<="00010000" after 18 ns;

elsif A="101" then

Qt<="00100000" after 18 ns;

elsif A="110" then

Qt<="01000000" after 18 ns;

elsif A="111" then

Qt<="10000000" after 18 ns;

end if;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.