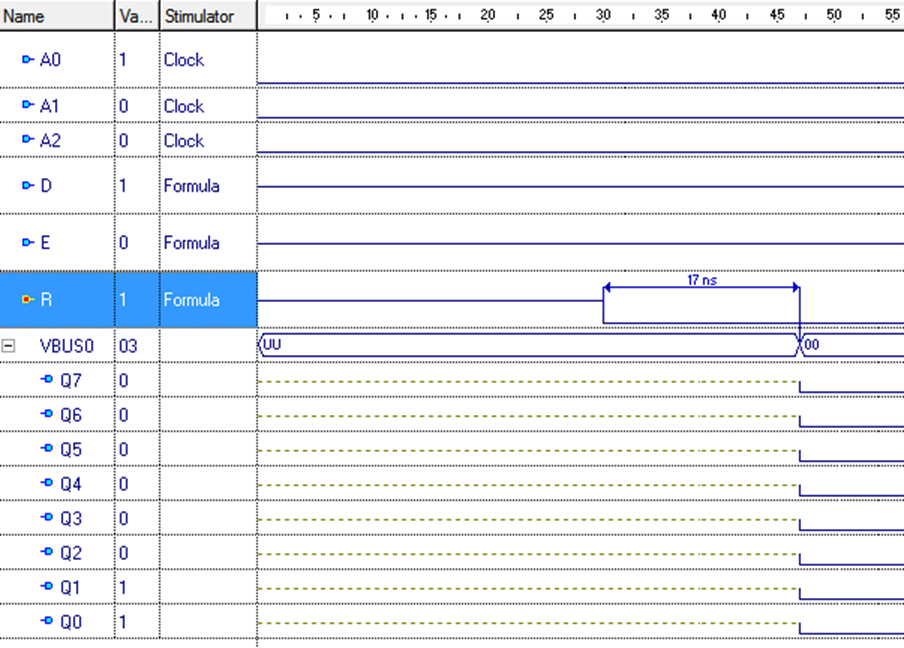

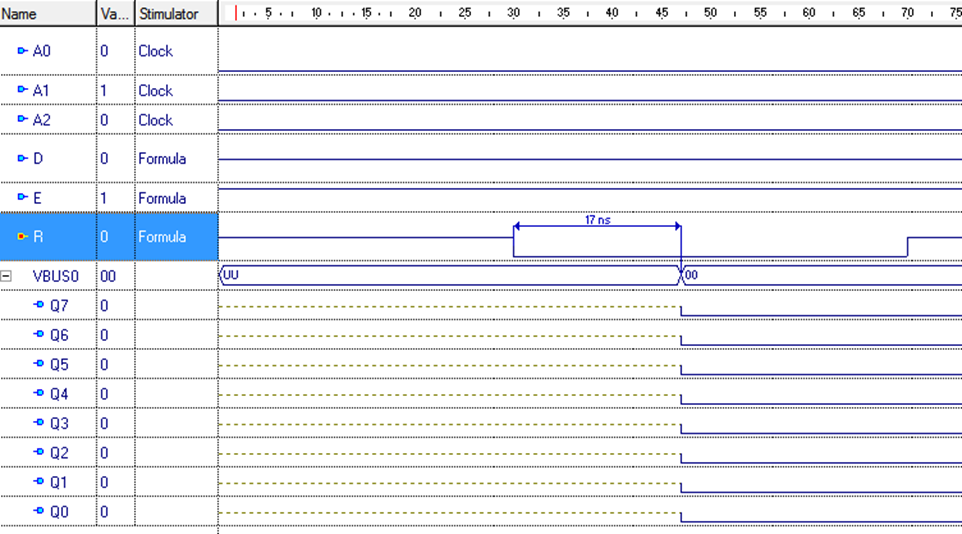

Рис.37. Задержка распространения сигнала от входа R до выхода Q при переключении его из 1 в 0 (17 нс).

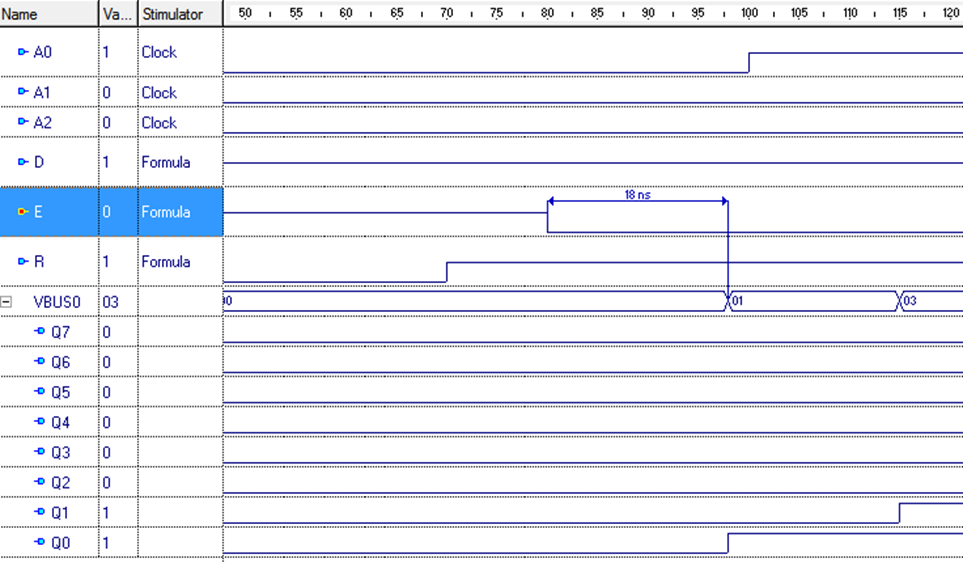

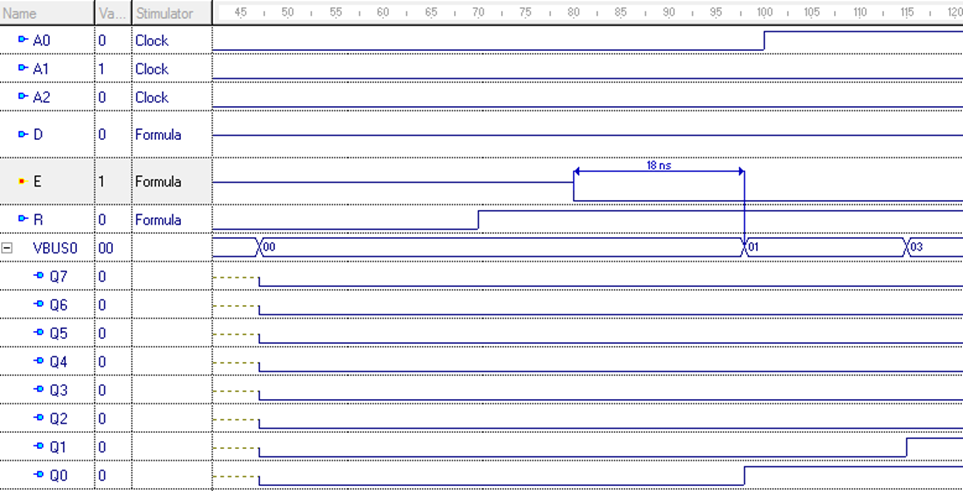

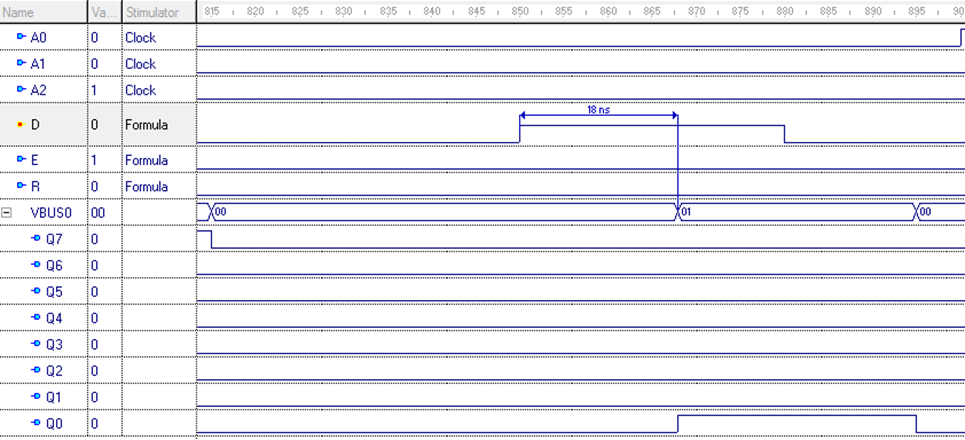

Рис.38. Задержка распространения сигнала от входа E до выхода Q при переключении его из 1 в 0 (18 нс).

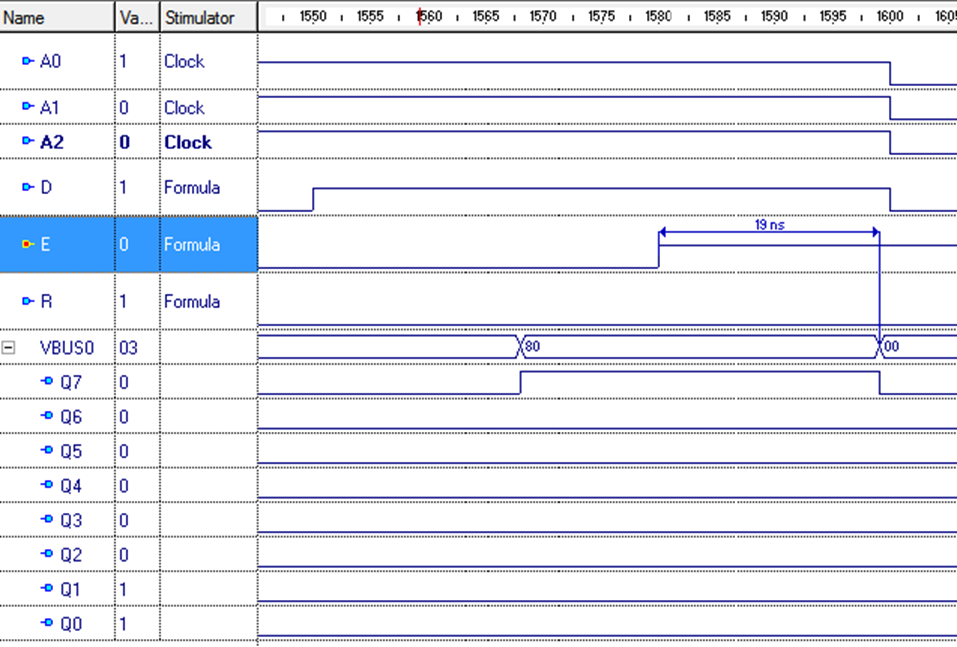

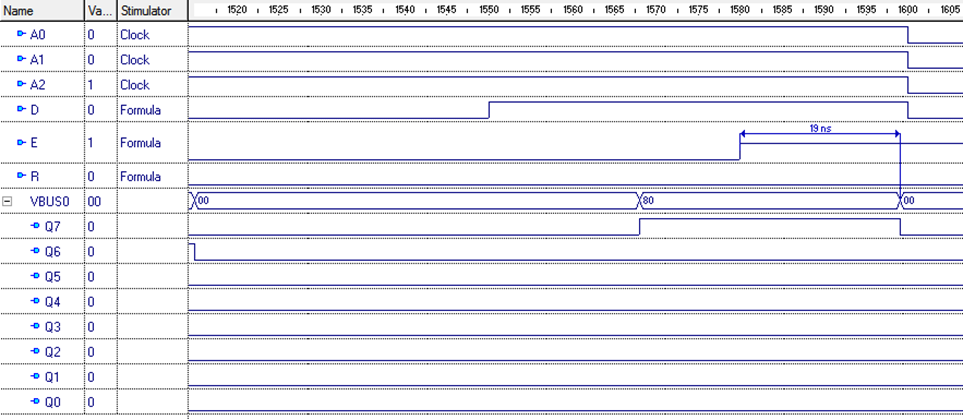

Рис.39. Задержка распространения сигнала от входа E до выхода Q при переключении его из 0 в 1 (19 нс).

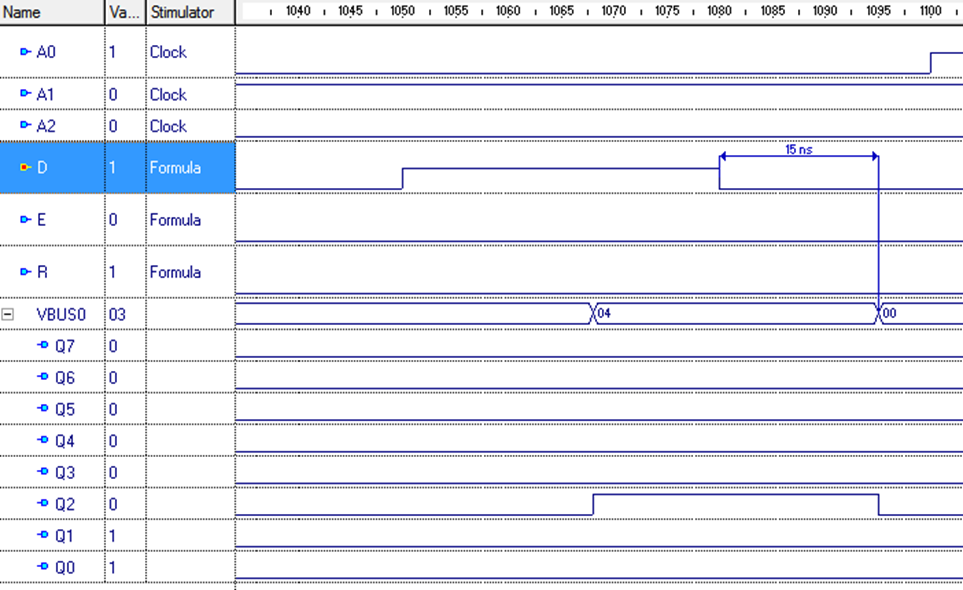

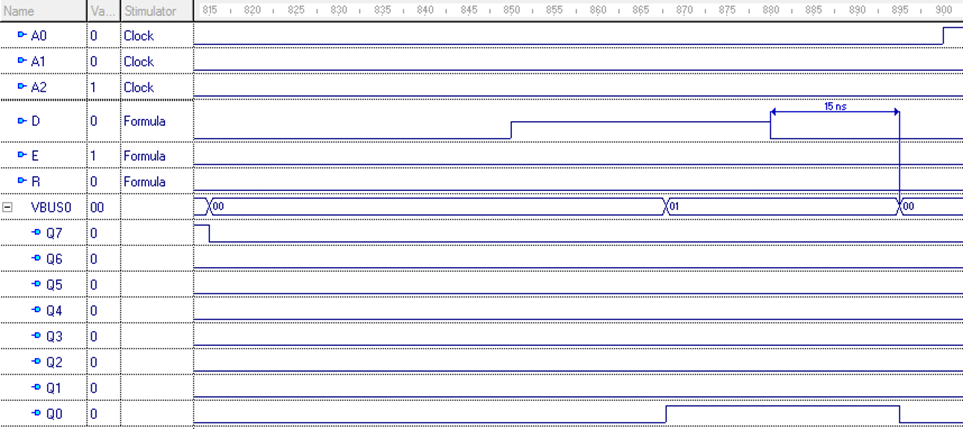

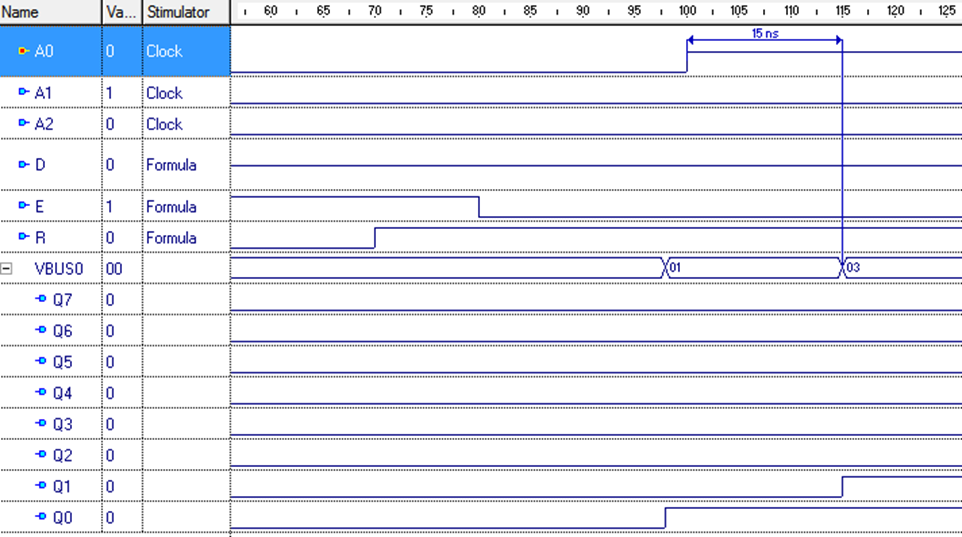

Рис.40. Задержка распространения сигнала от входа D до выхода Q при переключении его из 1 в 0 (15 нс).

Рис.41. Задержка распространения сигнала от входа D до выхода Q при переключении его из 0 в 1 (18 нс).

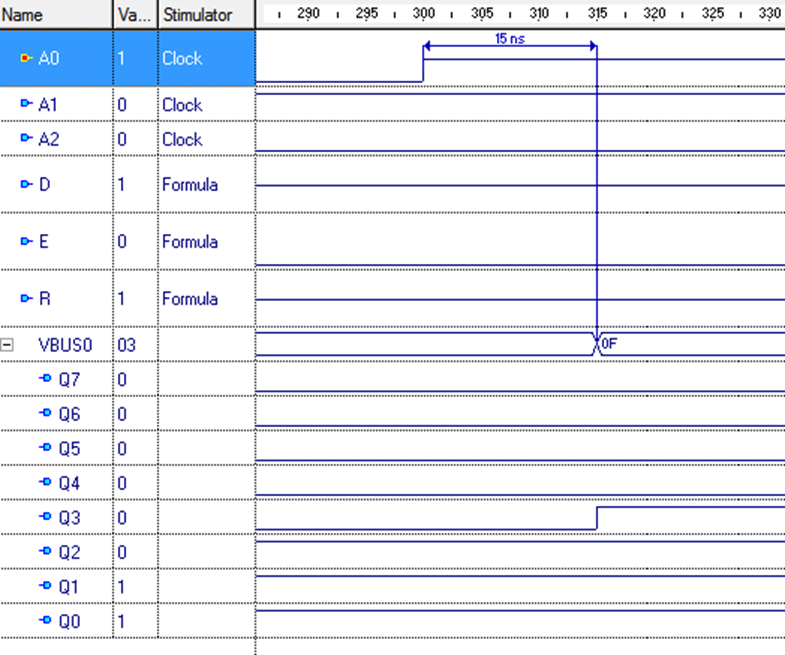

Рис.42. Задержка распространения сигнала от входа A до выхода Q при переключении его из 0 в 1 (15 нс)

Поведенческая VHDL-модель узла представлена в разделе 7.9.

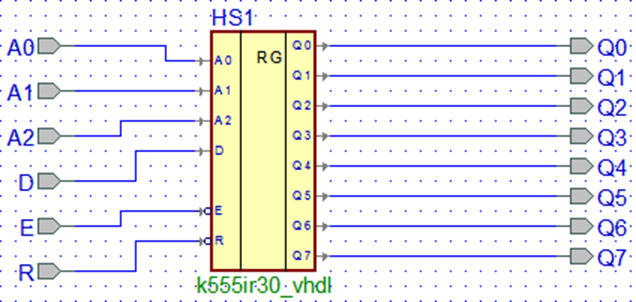

Рис.43.Схема верификации иерархического символа с подключенной vhdl-моделью.

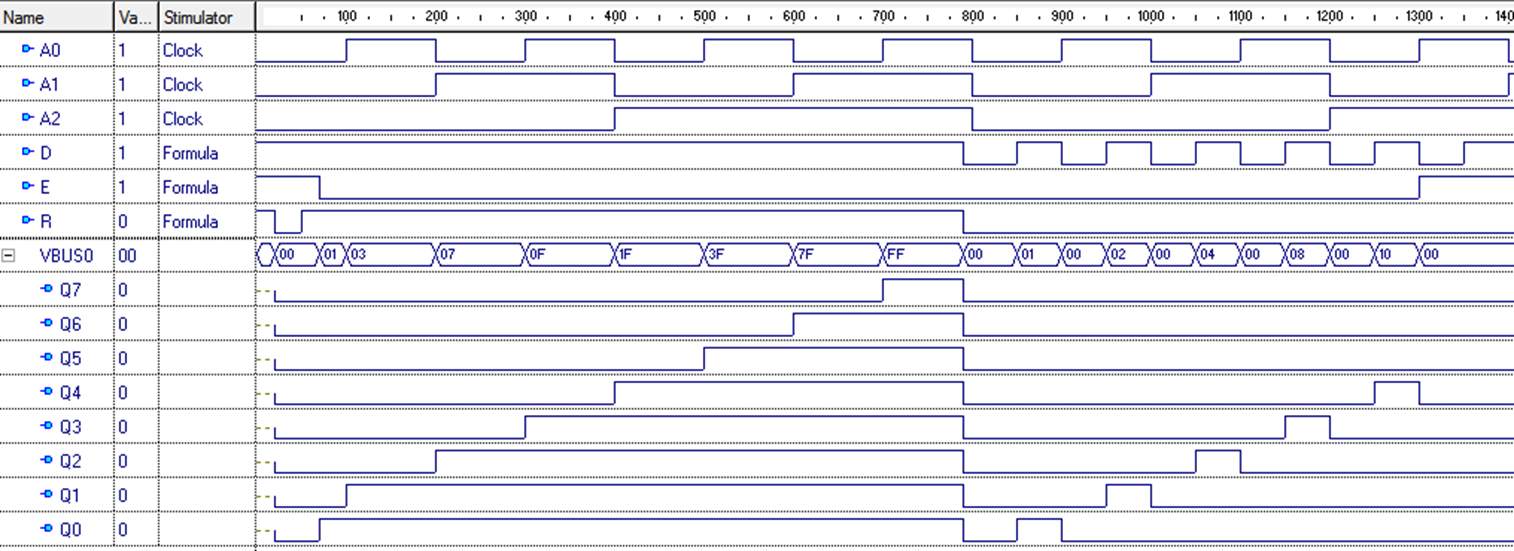

Рис.43. Временная диаграмма моделирования VHDL-модели узла.

Из полученных диаграмм можно сделать вывод, что подключенная VHDL - модель работает аналогично иерархическому символу, построенному с использованием схемы замещения. Следовательно, VHDL - модель функционирует верно.

Для того чтобы убедиться в том, что задержки подобраны верно, рассмотрены временнее диаграммы моделируемого узла (рис.44-49).

Рис.44. Задержка распространения сигнала от входа R до выхода Q при переключении его из 1 в 0 (17 нс).

Рис.45. Задержка распространения сигнала от входа E до выхода Q при переключении его из 1 в 0 (18 нс).

Рис.46. Задержка распространения сигнала от входа E до выхода Q при переключении его из 0 в 1 (19 нс).

Рис.47. Задержка распространения сигнала от входа D до выхода Q при переключении его из 1 в 0 (15 нс).

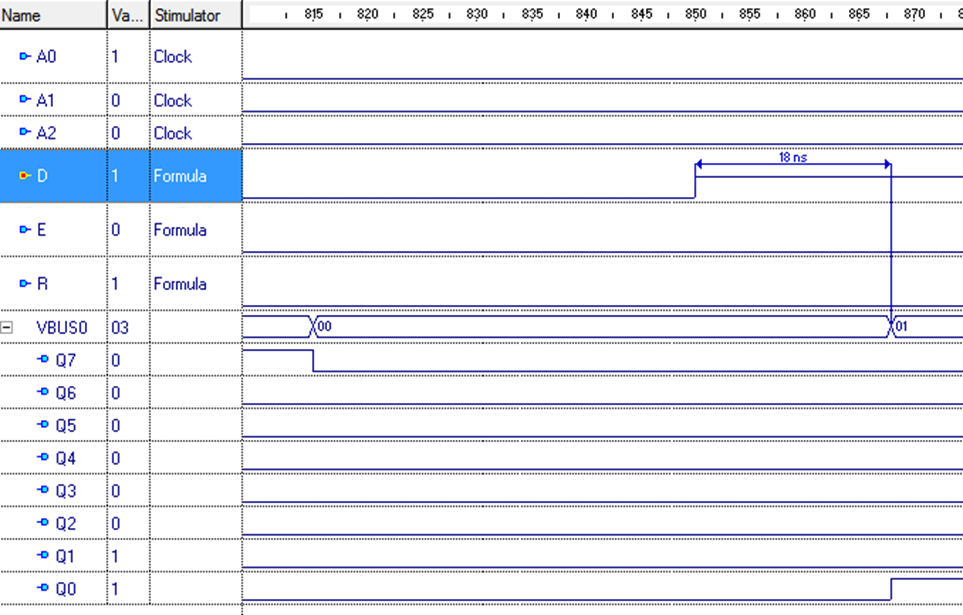

Рис.48.

Задержка распространения сигнала от входа D до

выхода Q при переключении его из 0 в 1 (18 нс).

Рис.48.

Задержка распространения сигнала от входа D до

выхода Q при переключении его из 0 в 1 (18 нс).

Рис.49. Задержка распространения сигнала от входа A до выхода Q при переключении его из 0 в 1 (15 нс)

В ходе выполнения курсовой работы были созданы структурные и поведенческие модели исследуемого цифрового узла на языке VHDL в пакетах OrCad 9.1., Active-HDL 8.1. Были проведены имитационные эксперименты с разработанным узлом, целью которых являлось подтверждение работоспособности узла.

При работе выяснилось, что пакет OrCad 9.1. не функционирует на операционной системе Windows 7, но через раз работает в Windows Vista, в связи с чем мне пришлось устанавливать на мой рабочий компьютер виртуальную машину Sun VirtualBox, с операционной системой Windows XP, где неожиданные вылеты программы случались весьма редко (если, конечно, сравнивать с ОС, перечисленными выше). Узел собирался и моделировался в данном пакете в течение нескольких месяцев. Схема была собрана в нескольких вариантах с одинаковой логикой, но разным количеством элементов. В работе использовалась схема с минимальным количеством элементов.

Пакет Active-HDL 8.1. оказался намного стабильнее в работе, так как проблем при проектировании узла, в нем не возникло. Так же он показал отличную работу на всех используемых операционных системах. Возврат к предыдущему шагу (Ctrl+Z) для данного пакета возможен более одного раза, в отличие от пакета OrCad 9.1. Узел был собран в данном пакете с первого раза и промоделирован в течение одного рабочего дня.

Не считая неустойчивости пакета OrCad 9.1 в некоторых операционных системах и сложности в подборе задержек, проектирование показалось достаточно легким. Выполнение данной работы помогло углубить знания, полученные за 6 семестр в моделировании схемотехнических устройств.

1. www.datasheetarchive.com/datasheet-pdf/01/DSA007418.html

2. Шалагинов А.В. Методические рекомендации «Как делать курсовую работу 2009».

3. Шалагинов А.В. Цифровое моделирование в САПР OrCAD 9.1.Учеб. Пособие. – Новосибирск: Изд-во НГТУ, 2002. – 104с.

4. Угрюмов Е.П. Цифровая схемотехника: Уче. Пособие для вузов. – 2-е изд., перераб. и доп. – СПб.: БХВ-Петербург, 2004. – 800 с.: ил.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.