Язык VHDL (Very-High-Speed Hardware Description Language) используется во многих системах для моделирования цифровых систем, например в САПР OrCAD или Active HDL фирмы ALDEC.

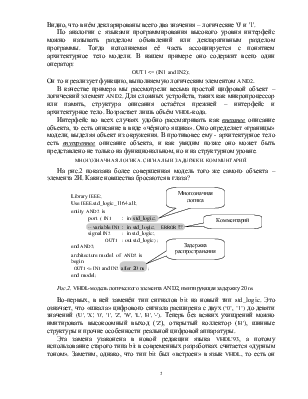

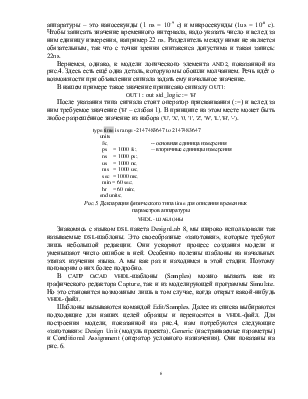

Начнём знакомство с создания очень простой модели логического элемента AND2, выполняющего функцию 2И (рис. 1).

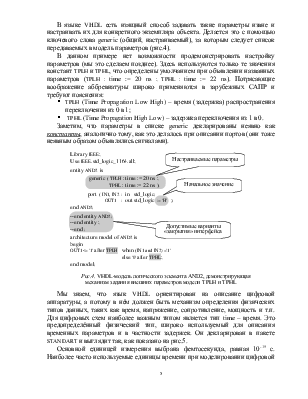

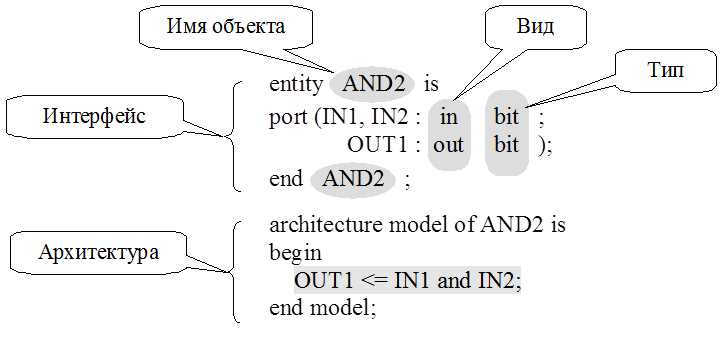

Мы видим, что модель состоит из двух частей. Верхняя часть (первые четыре строчки) – это интерфейс модели, нижняя – её архитектурное тело.

Описание интерфейса всегда начинается с ключевого слова entity, за которым следует имя моделируемого объекта (в данном случае элемента AND2). Слово entity переводится с английского языка как «сущность» или «объект».

В терминологии языка VHDL схему цифрового устройства принято рассматривать как проект, а каждый её компонент (триггер, регистр, память или процессор) – как объект этого проекта. Для любого компонента его окружением будут другие компоненты схемы, с которыми он обменивается данными. Этот обмен осуществляется через специальные «точки» внешнего интерфейса, называемые портами. Через них моделируемый объект взаимодействует с внешним миром, «окружением».

Полный список портов следует за ключевым словом port. Это могут быть входные (in), выходные (out) или двунаправленные (inout) порты.

С понятием «порт» ассоциируется, прежде всего, имя контакта элемента. Однако удобнее отождествлять его с именем сигнала, подаваемого на этот порт. В нашем примере входные порты IN1 и IN2, а также выходной порт OUT1 предназначены для подачи и съёма сигналов типа bit. Тип задаёт множество допустимых значений сигнала. Тип bit, используемый в первой редакции языка VHDL’87 (и в нашей первой модели), определён как:

type bit is ('0', '1');

Видно, что в нём декларированы всего два значения – логические '0' и '1'.

По аналогии с языками программирования высокого уровня интерфейс можно называть разделом объявлений или декларативным разделом программы. Тогда исполняемая её часть ассоциируется с понятием архитектурное тело модели. В нашем примере оно содержит всего один оператор:

OUT1 <= (IN1 and IN2);

Он то и реализует функцию, выполняемую логическим элементом AND2.

В качестве примера мы рассмотрели весьма простой цифровой объект – логический элемент AND2. Для сложных устройств, таких как микропроцессор или память, структура описания остаётся прежней – интерфейс и архитектурное тело. Возрастает лишь объём VHDL-кода.

Интерфейс во всех случаях удобно рассматривать как внешнее описание объекта, то есть описание в виде «чёрного ящика». Оно определяет «границы» модели, выделяя объект из окружения. В противовес ему - архитектурное тело есть внутреннее описание объекта, и как увидим позже оно может быть представлено не только на функциональном, но и на структурном уровне.

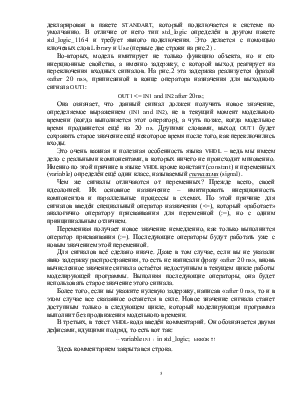

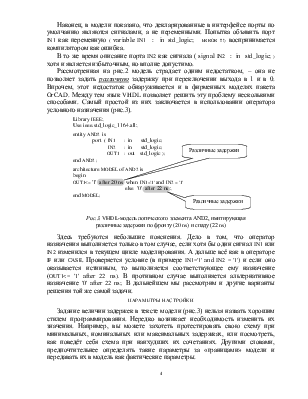

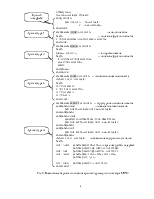

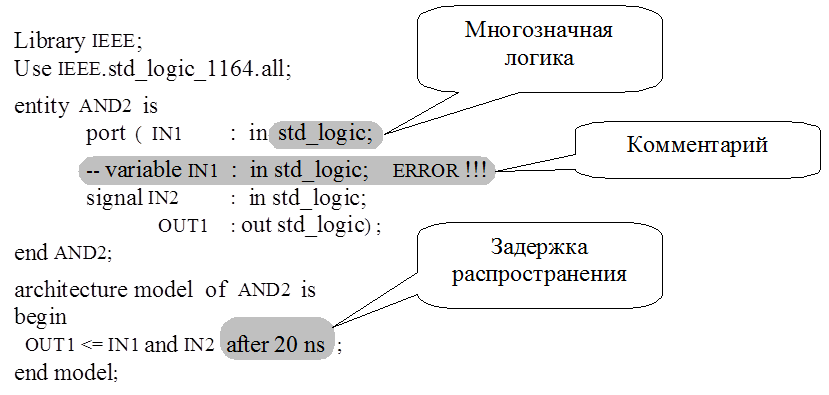

На рис.2 показана более совершенная модель того же самого объекта – элемента 2И. Какие новшества бросаются в глаза?

Во-первых, в ней заменён тип сигналов bit на новый тип std_logic. Это означает, что «шкала» цифрового сигнала расширена с двух (‘0’, ’1’) до девяти значений ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-'). Теперь без всяких ухищрений можно имитировать высокоомный выход ('Z'), открытый коллектор ('H'), шинные структуры и прочие особенности реальной цифровой аппаратуры.

Эта замена узаконена в новой редакции языка VHDL’93, а потому использование старого типа bit в современных разработках считается «дурным тоном». Заметим, однако, что тип bit был «встроен» в язык VHDL, то есть он декларирован в пакете STANDART, который подключается к системе по умолчанию. В отличие от него тип std_logic определён в другом пакете std_logic_1164 и требует явного подключения. Это делается с помощью ключевых слов Library и Use (первые две строки на рис.2) .

Во-вторых, модель имитирует не только функцию объекта, но и его инерционные свойства, а именно задержку, с которой выход реагирует на переключения входных сигналов. На рис.2 эта задержка реализуется фразой «after 20 ns», приписанной в конце оператора назначения для выходного сигнала OUT1:

OUT1 <= IN1 and IN2 after 20ns;

Она означает, что данный сигнал должен получить новое значение, определяемое выражением (IN1 and IN2), не в текущий момент модельного времени (когда выполняется этот оператор), а чуть позже, когда модельное время продвинется ещё на 20 ns. Другими словами, выход OUT1 будет сохранять старое значение ещё некоторое время после того, как переключились входы.

Это очень важная и полезная особенность языка VHDL – ведь мы имеем дело с реальными компонентами, в которых ничего не происходит мгновенно. Именно по этой причине в языке VHDL кроме констант (constant) и переменных (variable) определён ещё один класс, называемый сигналами (signal).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.