Чем же сигналы отличаются от переменных? Прежде всего, своей идеологией. Их основное назначение – имитировать инерционность компонентов и параллельные процессы в схемах. По этой причине для сигналов введён специальный оператор назначения (<=), который «работает» аналогично оператору присваивания для переменной (:=), но с одним принципиальным отличием.

Переменная получает новое значение немедленно, как только выполнится оператор присваивания (:=). Последующие операторы будут работать уже с новым значением этой переменной.

Для сигналов всё сделано иначе. Даже в том случае, если вы не указали явно задержку распространения, то есть не написали фразу «after 20 ns», вновь вычисленное значение сигнала остаётся недоступным в текущем цикле работы моделирующей программы. Выполняя последующие операторы, она будет использовать старое значение этого сигнала.

Более того, если вы укажите нулевую задержку, написав «after 0 ns», то и в этом случае все сказанное останется в силе. Новое значение сигнала станет доступным только в следующем цикле, который моделирующая программа выполнит без продвижения модельного времени.

В третьих, в текст VHDL-кода введён комментарий. Он обозначается двумя дефисами, идущими подряд, то есть вот так:

-- variable IN1 : in std_logic; ERROR !!!

Здесь комментарием закрыта вся строка.

Наконец, в модели показано, что декларированные в интерфейсе порты по умолчанию являются сигналами, а не переменными. Попытка объявить порт IN1 как переменную ( variable IN1 : in std_logic; ERROR !!!) воспринимается компилятором как ошибка.

В то же время описание порта IN2 как сигнала ( signal IN2 : in std_logic; ) хотя и является избыточным, но вполне допустимо.

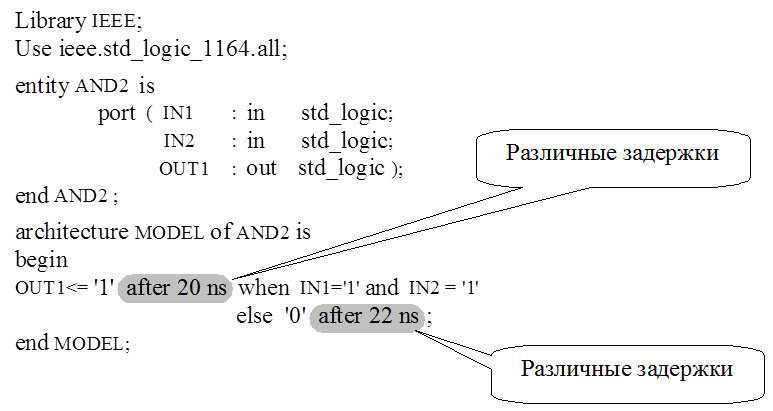

Рассмотренная на рис.2 модель страдает одним недостатком, – она не позволяет задать различную задержку при переключении выхода в 1 и в 0. Впрочем, этот недостаток обнаруживается и в фирменных моделях пакета OrCAD. Между тем язык VHDL позволяет решить эту проблему несколькими способами. Самый простой из них заключается в использовании оператора условного назначения (рис.3).

Здесь требуются небольшие пояснения. Дело в том, что оператор назначения выполняется только в том случае, если хотя бы один сигнал IN1 или IN2 изменился в текущем цикле моделирования. А дальше всё как в операторе IF или CASE. Проверяется условие (в примере IN1='1' and IN2 = '1') и если оно оказывается истинным, то выполняется соответствующее ему назначение (OUT1<= '1' after 22 ns). В противном случае выполняется альтернативное назначение '0' after 22 ns;. В дальнейшем мы рассмотрим и другие варианты решения той же самой задачи.

Задание величин задержек в тексте модели (рис.3) нельзя назвать хорошим стилем программирования. Нередко возникает необходимость изменить их значения. Например, вы можете захотеть протестировать свою схему при минимальных, номинальных или максимальных задержках, или посмотреть, как поведёт себя схема при наихудших их сочетаниях. Другими словами, предпочтительнее определять такие параметры за «границами» модели и передавать их в модель как фактические параметры.

В языке VHDL есть изящный способ задавать такие параметры извне и настраивать их для конкретного экземпляра объекта. Делается это с помощью ключевого слова generic (общий, настраиваемый), за которым следует список передаваемых в модель параметров (рис.4).

В данном примере нет возможности продемонстрировать настройку параметров (мы это сделаем позднее). Здесь используются только те значения констант TPLH и TPHL, что определены умолчанием при объявлении названных параметров (TPLH : time := 20 ns ; TPHL : time := 22 ns). Потрясающие воображение аббревиатуры широко применяются в зарубежных САПР и требуют пояснения:

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.