В исполняемой части архитектурного тела (после слова begin) по объявленным ранее шаблонам компонентов INVR, AND2 и OR2 создаются их конкретные экземпляры. Причём каждый экземпляр получает свою уникальную метку (обычно это позиционное обозначение): DD1..DD4. При необходимости в карте настройки элемента (generic map) указываются желаемые параметры, а в карте порта (port map) отражаются структурные связи между компонентами схемы.

Разберём подробнее первую запись:

DD1 : AND2 generic map (10ns,12ns) --карта настройки задержек

port map (IN1=>D0, IN2=>F1,OUT1=>F2); -- карта порта

Она описывает элемент DD1, выполняющий функцию 2И (рис.7, в). Модель этого элемента имеет имя AND2. В ней объявлен список настраиваемых параметров generic (см. рис.4), которым теперь (при конкретизации объекта), мы можем передать желаемые параметры. Делается это через карту настройки generic map. В данном случае соответствие между формальными (TPLH, TPHL) и фактическими (10ns, 12ns) параметрами устанавливается позиционным сопоставлением, то есть первый формальный параметр TPLH получит первое значение в списке фактических параметров. И путать местами их нельзя.

Существует другой, более надёжный способ связывания, называемый поимённым или ключевым сопоставлением. Он демонстрируется при конкретизации элемента DD3 того же самого назначения:

DD3 : AND2 generic map (TPHL=>15ns, TPLH=>11ns) -- карта настройки

port map (D1, A, F3); -- карта порта

Обратите внимание на изменения в его карте настройки. Теперь мы поимённо назвали параметры задержки TPHL и TPLH и «настроили» их на конкретные значения 15ns и 11ns. Не знаю, заметили ли вы, что следуют они в карте настройки в обратном порядке.

Элементы DD1 и DD3 выполняют одну функцию, но имеют разные задержки, и этот эффект достигнут благодаря индивидуальной настройке их параметров.

Те же самые приёмы используются при связывании формальных имен портов (IN1, IN2, OUT1) с фактическими именами сигналов, действующих в моделируемой схеме (D0, D1, A, F1, F2, F3, Y).

Эта работа выполняется с помощью карт портов каждого экземпляра компонента. Для разнообразия в карте порта компонента DD1 используется поимённое связывание (port map (IN1=>D0, IN2=>F1, OUT1=>F2); ), а в компоненте DD3 связь между портами и сигналами реализуется позиционным сопоставлением (port map (D1, A, F3); ).

Как видно, язык VHDL ориентирован на явное описание элементов и неявное описание связей между ними. Однако и соединения тоже легко проследить по одинаковым именам сигналов (цепей) в картах портов. На рис.8 в архитектуре 4 одно из таких соединений выделено цветом. Выходной порт OUT1 элемента DD1 формирует сигнал F2, который по не описанному явно проводнику поступает на входной порт IN1 элемента DD2. Аналогичным образом обнаруживаются и все остальные соединения в схеме.

Рассмотренные способы поведенческого, потокового и структурного описания, казалось бы, составляют полный арсенал инструментальных средств разработчика цифровой аппаратуры. Но, оказывается, язык VHDL позволяет комбинировать их в произвольных сочетаниях. Это очень полезная особенность языка. Чаще всего она используется на начальных этапах проектирования, когда полного структурного описания проекта ещё не существует.

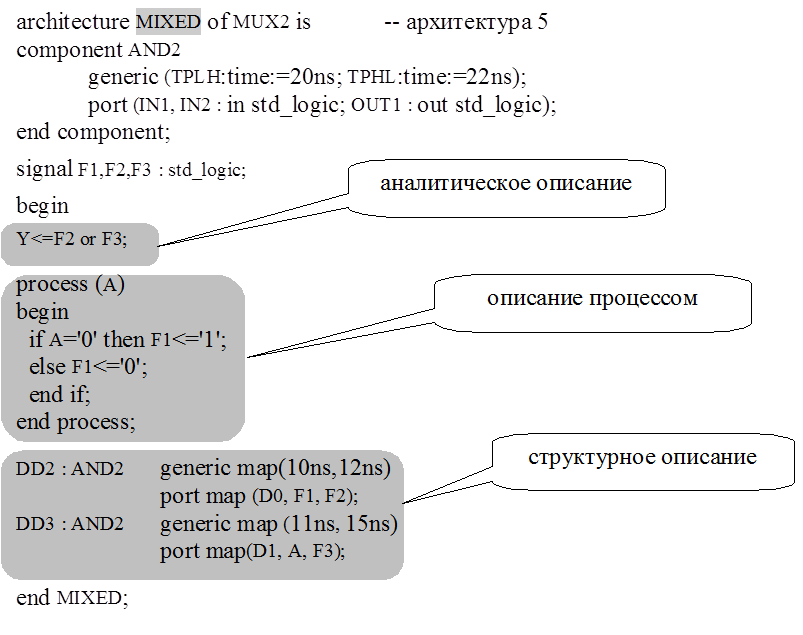

Смешанное описание позволяет «плавно» перейти от алгоритма к структуре, постепенно заменяя отдельные его абстрактные представления аппаратными решениями. На рис.9 показан один из многочисленных вариантов смешанного описания. Архитектура называется MIXED (смешанный). Она содержит фрагмент аналитического описания (Y<=F2 or F3;), описание инвертора процессом (process (A) ) и структурное описание остальной части мультиплексора (элементы DD2 и DD3).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.