Тип BITтоже содержит только два значения '0' и '1':

type bit is ('0', '1');

Однако будет ошибкой отождествлять оба типа: значение TRUE не эквивалентно значению '1', а FALSE не есть '0'.

Мы использовали тип bit в самой первой модели (см. рис.1) и отметили его «убогость». Оба названных типа являются предопределёнными, они декларированы в пакете STANDARD, который хранится в файле с аналогичным названием standard.vhd.

В этом же пакете объявлен и физический тип TIME – время:

type time is range -2147483647 to 2147483647…(см. рис. 5)

И, наконец, здесь же декларируется уже известный нам целочисленный тип INTEGER:

type integer is range -2147483648 to 2147483647; (см. рис.12)

Кроме названных типов, в старой редакции VHDL’87 широко использовался тип BIT_VECTOR, определяемый как массив битов:

type bit_vector is array (natural range <>) of bit;

По уже известным причинам этот тип заменён более совершенным типом std_logic_vector (версия VHDL’93):

type std_logic_vector is array ( natural range <>) of std_logic;

С ним мы встречались совсем недавно (см. рис.15).

Чтобы закончить разговор о стандартных типах данных, «встроенных» в язык VHDL, приведём оставшиеся типы для «полноты картины».

Символьный тип CHARACTER представляет собой набор символов ASCII-кода:

type character is (nul, ..'0',..'9',.. 'A', ..'Z', ..'a', ..'z', ..del, ..'А', ..'Я', ..'а', ..'я' );

Здесь приведены только некоторые из возможных значений данного типа, чтобы показать, что кириллические символы тоже допустимы в языке VHDL. Правда OrCAD по каким-то причинам их не поддерживает.

Строковый тип STRING декларирован как массив символов:

type string is array (positive range <>) of character;

Обратите внимание, символы заключаются в одиночные, а строки – в двойные кавычки.

В язык VHDL встроен ещё один тип SEVERITY_LEVEL, предупреждающий о степени серьёзности обнаруженной ошибки:

type severity_level is (note, warning, error, failure);

Он содержит всего четыре значения: note – уведомление, warning – предупреждение, error – ошибка и failure – авария (фатальная ошибка). Названный тип используется совместно с оператором assert для контроля временных соотношений в схеме. Позднее мы познакомимся с ним более подробно.

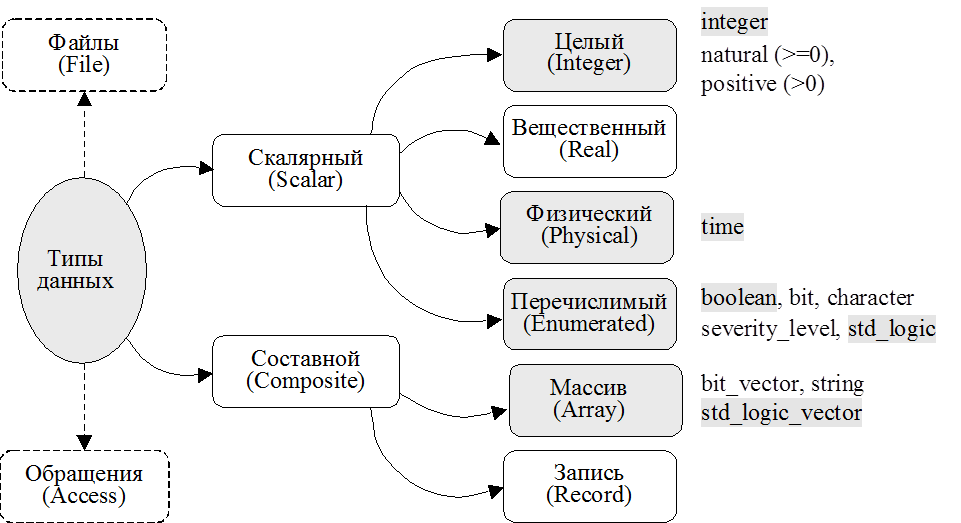

На рис.17 приведена классификация типов данных языка VHDL. Серой заливкой выделены типы, наиболее часто используемые при построении VHDL-моделей цифровой аппаратуры (std_logic, std_logic_vector, time, boolean, integer). Пунктиром показаны типы данных, которые не находят применения в процедурах функциональной верификации, выполняемых методом моделирования.

Рис.17. Классификация типов данных языка VHDL

Может показаться странным, что в язык описания аппаратуры VHDL введён вещественный тип REAL. Между тем, он широко используется для высокоуровневых поведенческих описаний и для определения физических типов. Например, физический тип VOLTAGE (напряжение) можно декларировать так:

type VOLTAGE is range 0.0 to 10.0;

Тип STRING тоже находит применение при моделировании цифровой аппаратуры. Он используется оператором report, чтобы уточнить обнаруженное нарушение временных соотношений в схеме.

Кроме типа в языке VHDL может быть декларирован подтип данных (subtype), задающий подмножество значений данного типа. Например, для типа INTEGER предопределены два подтипа NATURAL и POSITIVE:

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

Первый подтип исключает из диапазона целых чисел все отрицательные числа, второй – сужает диапазон ещё на одну позицию, исключая 0.

Аналогичным образом, подтип DELAY_LENGTH (длина задержки) исключает из физического типа TIME (время) все отрицательные значения:

subtype delay_length is time range 0 fs to time'high;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.