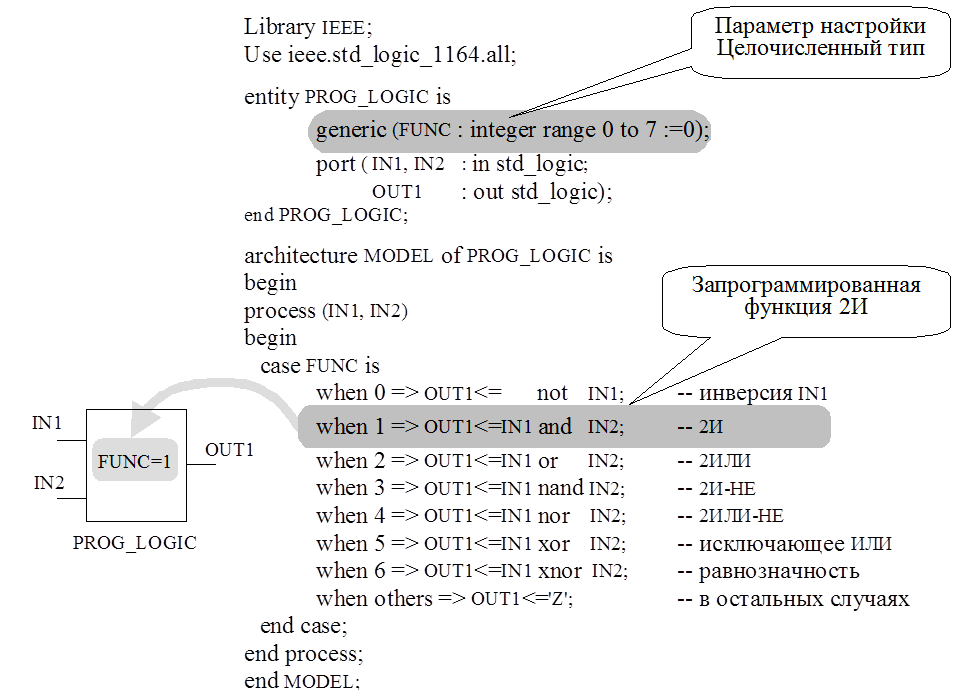

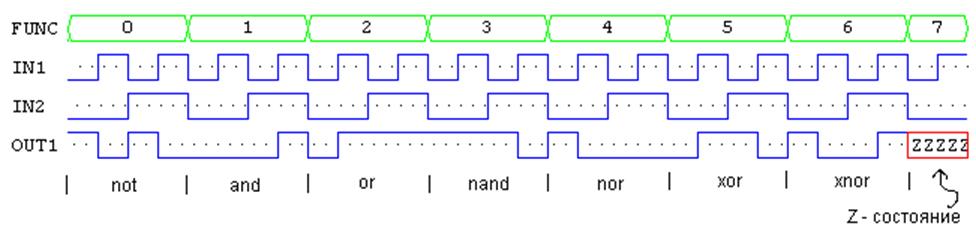

Прежде чем говорить о возможных типах данных в языке VHDL, рассмотрим весьма поучительный пример – модель логического элемента с программируемой функцией (рис.12).

По мнению специалистов «программируемая аппаратура произведёт в ближайшие годы такой же переворот, как микрокомпьютеры в начале 70-х годов». Это серьёзное заявление, конечно же, адресовано большим интегральным схемам, но мы начнём с низкого уровня.

Рис.12. VHDL-модель логического элемента с программируемой функцией

В описание интерфейса введён параметр настройки FUNC. Он имеет целый тип и может принимать значения в диапазоне от 0 до 7. По умолчанию параметру FUNC определено значение 0, то есть элемент инвертирует данные с входа IN1, игнорируя вход IN2 (верхняя строка в операторе case).

Задавая различные значения параметру FUNC, мы можем программировать элемент на любую из 7 логических функций, определённых в языке VHDL (not, and, or, nand, nor, xor, xnor). Например, если задать FUNC=1 (как в нашем примере), то элемент будет выполнять логическое умножение 2И.

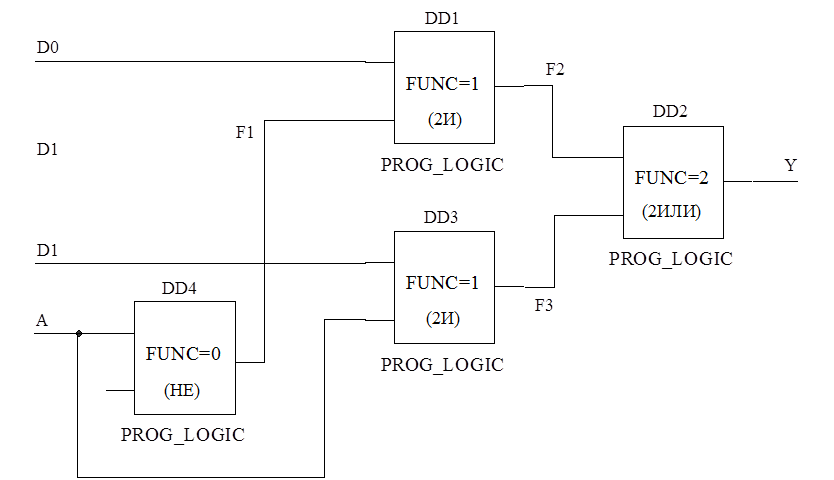

На рис.13 показан уже известный нам мультиплексор MUX2 (см. рис.7, в), реализованный на элементах с программируемой функцией. Элементы DD1 и DD3 настроены на операцию 2И, элемент DD2 реализует функцию 2ИЛИ, а DD4 «превращён» в инвертор.

Рис.13. Мультиплексор MUX2, построенный на элементах с программируемой функцией

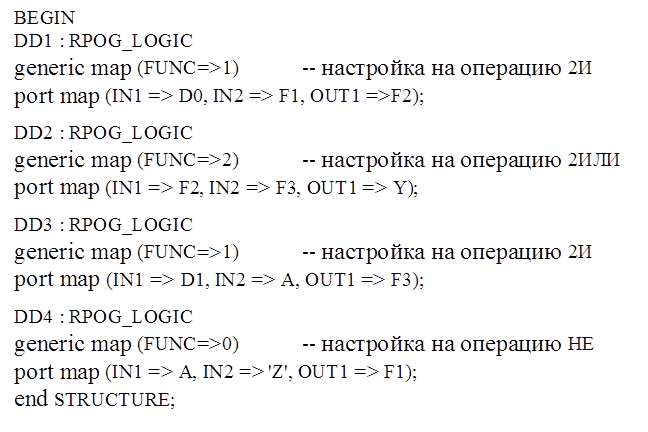

На рис.14 показан фрагмент структурной модели MUX2, где хорошо видна настройка отдельных экземпляров элемента PROG_LOGIC на желаемую функцию.

Рассмотренный пример демонстрирует статическую настройку, напоминающую программирование ПЛМ пережиганием перемычек. Другими словами, оперативно изменять настройку мы не можем. Действительно, чтобы поменять функцию, надо внести изменения в исходный VHDL-код, а затем выполнить новую компиляцию модели.

Между тем в современной схемотехнике уже давно существует целый класс динамически программируемых устройств с триггерной памятью реконфигурации (FPGA). В них реализована быстрая (оперативная) смена настроек, что позволяет использовать одну и ту же аппаратуру в разных ролях.

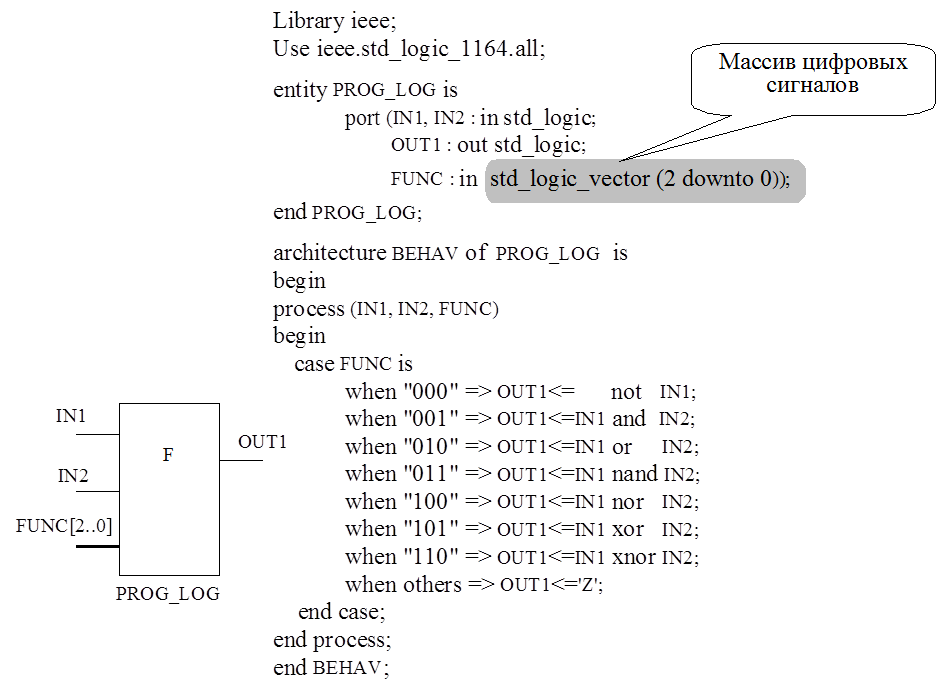

Попробуем и мы усовершенствовать своё детище, обеспечив элементу PROG_LOG «динамическую реконфигурацию». Одно из возможных решений показано на рис.15.

Рис. 15. VHDL-модель

логического элемента PROG_LOG с динамически

перепрограммируемой функцией

Теперь элемент PROG_LOG имеет управляющий вход, на который подаётся 3-разрядный двоичный код, задающий выполняемую функцию. Другими словами, управляющий вход представляет собой многоразрядный контакт, на который подаётся шинный сигнал. На языке VHDL такой сигнал описывается как одномерный массив типа std_logic_vector. В нашем примере размер массива (ширина шины) задаётся убывающим диапазоном (2 downto 0) и содержит три одиночных сигнала (проводника).

Такое решение позволяет оперативно (в ходе одного эксперимента) управлять логической функцией элемента PROG_LOG. Кстати, свободная позиция “111” позволяет реализовать ещё и режим высокоомного выхода (рис.16).

Рис.16. Оперативное управление логической функцией элемента PROG_LOG

Рассмотренные примеры показывают, что язык VHDL, как и большинство языков программирования, поддерживает различные типы данных. В частности, они дают разработчику аппаратуры возможность непосредственно представлять шины в виде целого числа или массива цифровых сигналов.

Вспомним уже известные нам типы данных. Тип BOOLEAN состоит из двух значений TRUE (истина) и FALSE (ложь). Он декларируется строкой:

type boolean is (false, true);

Этот тип широко применяется в условных операторах, например, в операторе if A='0' then …(см. рис.9) выражение A='0' принимает значения булевского типа.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.