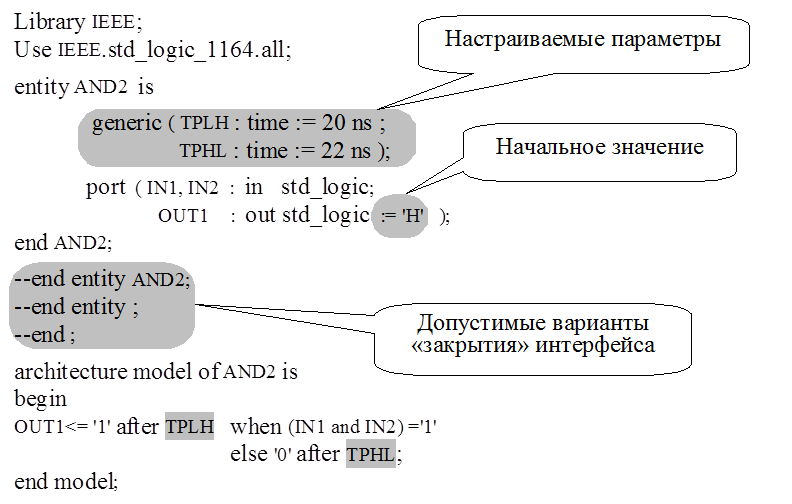

§ TPLH (Time Propagation Low High) – время (задержка) распространения переключения из 0 в 1;

§ TPHL (Time Propagation High Low) – задержка переключения из 1 в 0.

Заметим, что параметры в списке generic декларированы неявно как константы, аналогично тому, как это делалось при описании портов (они тоже неявным образом объявлялись сигналами).

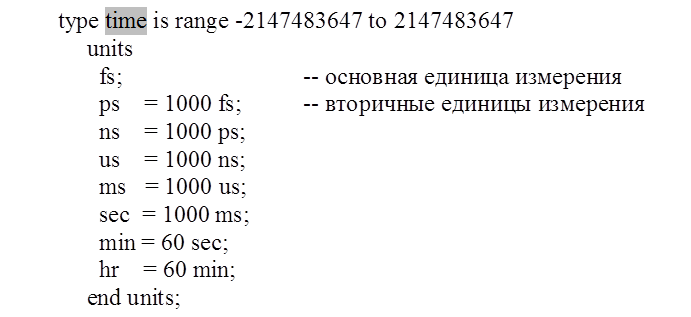

Мы знаем, что язык VHDL ориентирован на описание цифровой аппаратуры, а потому в нём должен быть механизм определения физических типов данных, таких как время, напряжение, сопротивление, мощность и т.п. Для цифровых схем наиболее важным типом является тип time – время. Это предопределённый физический тип, широко используемый для описания временных параметров и в частности задержек. Он декларирован в пакете STANDART и выглядит так, как показано на рис.5.

Основной единицей измерения выбрана фемтосекунда, равная 10-15 с. Наиболее часто используемые единицы времени при моделировании цифровой аппаратуры – это наносекунды (1 ns = 10-9 c) и микросекунды (1us = 10-6 c). Чтобы записать значение временного интервала, надо указать число и вслед за ним единицу измерения, например 22 ns. Разделитель между ними не является обязательным, так что с точки зрения синтаксиса допустима и такая запись: 22ns.

Вернемся, однако, к модели логического элемента AND2, показанной на рис.4. Здесь есть ещё одна деталь, которую мы обошли молчанием. Речь идёт о возможности при объявлении сигнала задать ему начальное значение.

В нашем примере такое значение приписано сигналу OUT1:

OUT1 : out std_logic := 'H'

После указания типа сигнала стоит оператор присваивания (:=) и вслед за ним требуемое значение ('H' – слабая 1). В принципе на этом месте может быть любое разрешённое значение из набора ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-').

Знакомясь с языком DSL пакета DesignLab 8, мы широко использовали так называемые DSL-шаблоны. Это своеобразные «заготовки», которые требуют лишь небольшой редакции. Они ускоряют процесс создания модели и уменьшают число ошибок в ней. Особенно полезны шаблоны на начальных этапах изучения языка. А мы как раз и находимся в этой стадии. Поэтому поговорим о них более подробно.

В САПР OrCAD VHDL-шаблоны (Samples) можно вызвать как из графического редактора Capture, так и из моделирующей программы Simulate. Но это становится возможным лишь в том случае, когда открыт какой-нибудь VHDL-файл.

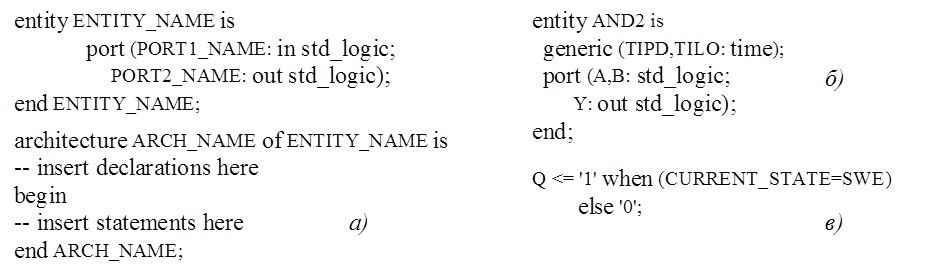

Шаблоны вызываются командой Edit/Samples. Далее из списка выбираются подходящие для наших целей образцы и переносятся в VHDL-файл. Для построения модели, показанной на рис.4, нам потребуются следующие «заготовки»: Design Unit (модуль проекта), Generic (настраиваемые параметры) и Conditional Assignment (оператор условного назначения). Они показаны на рис. 6.

С помощью первого шаблона создаётся каркас VHDL-модели, второй шаблон вставляется в интерфейс, а третий – в архитектурное тело. После этого остаётся лишь заменить формальные имена идентификаторов, параметров и выражений реальными. Вот и вся работа. Результатом её будет модель, показанная на рис. 4.

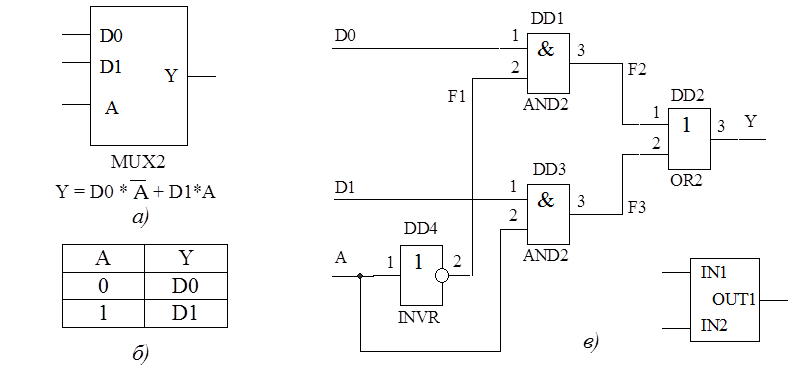

Любой объект проекта имеет только один интерфейс, но у него может быть несколько архитектур. Это объясняется тем, что одна и та же функция при реализации даёт множество структурных решений. Сказанное подтвердим на простом примере, выбрав в качестве объекта проекта мультиплексор MUX2 (рис.7).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.