Вероятно, вас уже давно мучает вопрос, как при моделировании задать желаемую архитектуру, если их несколько. Самое простое решение – использовать механизм умолчаний. Например, САПР OrCAD_9 по умолчанию выбирает первую архитектуру, расположенную сразу за описанием интерфейса. Если вам потребуется другая архитектура, то её надо просто переместить наверх. На первых порах можно смириться с таким неудобством.

Понятно, что все архитектуры должны давать одно и то же поведение объекта. А это значит, что по временным диаграммам мы не в состоянии выяснить, с какой архитектурой имеем дело в настоящий момент. Чтобы идентифицировать каждую архитектуру, придётся задать в ней хотя бы один отличительный признак. Для мультиплексора мы поступили просто: каждая архитектура формирует результат со своей задержкой. Для архитектуры 1 (FUNC) – это 5ns, для архитектуры 2 (BEHAV) – 10ns и т.д. (см. рис.8).

В дальнейшем мы познакомимся с понятием конфигурация (configuration), которая играет ключевую роль в организации VHDL-описания всего проекта, и, в частности, в ней задаётся желаемая архитектура.

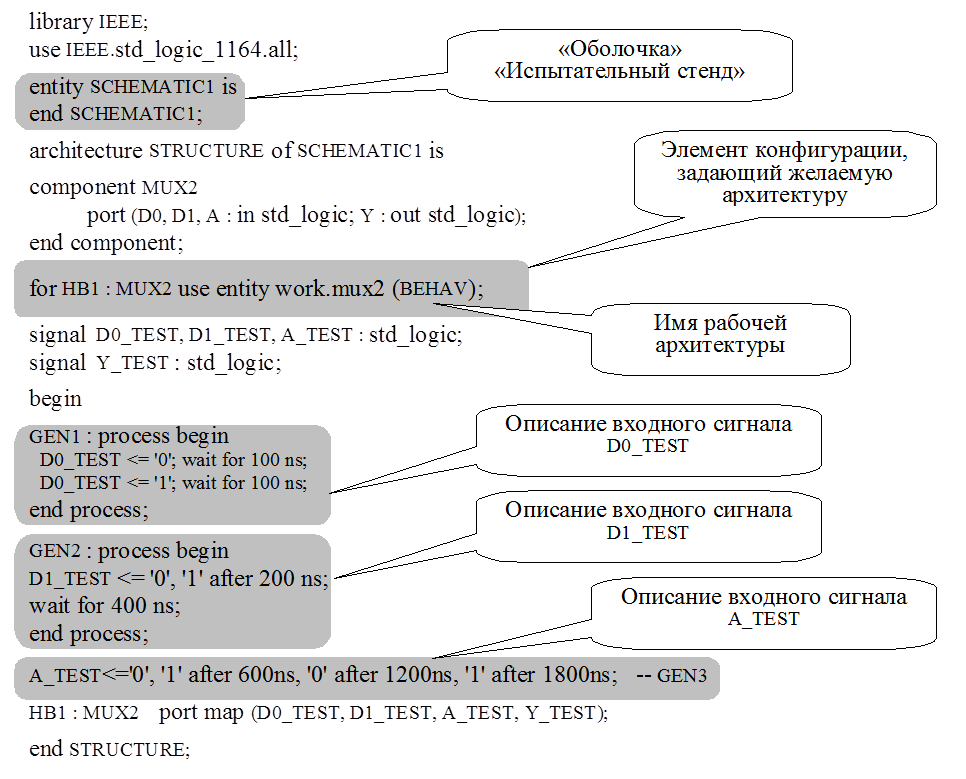

Для пытливого ума предлагаю компромиссный вариант. Надо открыть VHDL-файл, автоматически создаваемый системой OrCAD при передаче вашей схемы на моделирование (команда Tools/Simulate) и добавить в него элемент конфигурации проекта, выделенный на рис.10 серым цветом.

Эта строка означает, что для элемента схемы HB1 (for HB1) надо использовать (use) объект проекта MUX2, находящийся в рабочей библиотеке work, с архитектурой, указанной в круглых скобках. В нашем примере – это архитектура behav. Добавлю, что рабочая библиотека – это библиотека проекта, в которой содержатся все откомпилированные VHDL-файлы, подключённые к проекту.

Теперь, заменяя только одно слово, вы можете ссылаться на любую подключённую к объекту MUX2 архитектуру (FUNC, BEHAV, FLOW, STRUCT, MIXED). Не забывайте, их отличия в работе проявляются только разными задержками.

Обратите внимание ещё на одну вещь. Автоматически сгенерированный VHDL-код тоже имеет структуру объекта проекта, то есть содержит интерфейс с именем SCHEMATICS1 и архитектурное тело STRUCTURE.

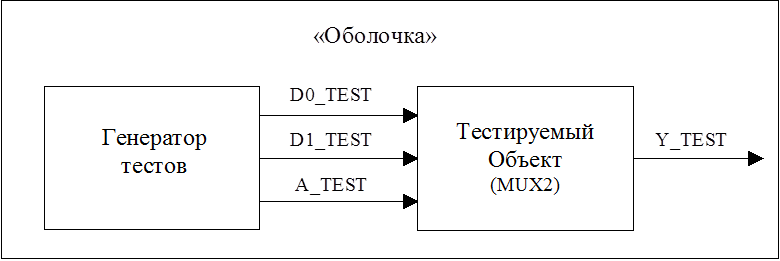

Единственная его особенность - в нём нет портов, а, значит, отсутствуют и связи с внешним миром. Кажется – это совершенно бессмысленная «вещь в себе». Но как говорится, первое впечатление обманчиво. Перед нами «оболочка», в которую помещается объект проектирования для проверки правильности его работы. Иногда её называют «испытательным стендом», и служит эта установка для имитации процесса тестирования цифровой аппаратуры.

Внутри оболочки можно разместить не только тестируемый объект, но и VHDL-описания входных сигналов, которые должны на него подаваться в качестве внешних воздействий (рис.11). Генератор тестовых наборов может быть оформлен как самостоятельный объект проекта, но проще его «встроить» в оболочку, в качестве отдельных процессов. На рис.10 именно так и сделано, при этом демонстрируются различные способы VHDL-описания внешних воздействий. Обратите внимание на очень важный момент, они (внешние воздействия) являются внешними только для тестируемого объекта, но для «испытательного стенда» они остаются внутри оболочки.

Наиболее просто реализуется временная диаграмма (waveform) с помощью оператора назначения (см. рис.10, сигнал A_TEST). Оказывается, что любому сигналу можно назначить не одно, а несколько будущих значений (транзакций). И пусть вас не смущает, что вы делаете назначение входному сигналу.

Именно эта возможность используется для описания внешнего воздействия A_TEST (A_TEST<='0', '1' after 600ns, '0' after 1200ns, '1' after 1800ns ; -- GEN3).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.