Министерство образования и науки РФ

Новосибирский Государственный Технический Университет

Кафедра ВТ

|

|||||

|

|

||||

Курсовая работа

по дисциплине

Факультет: АВТ

Группа: АМ-215

Студент: Белоглазов А. В.

Преподаватель: Шалагинов А. В.

Новосибирск

2005

Содержание

1. Постановка задачи.. 3

2. Условное графическое обозначение моделируемого узла.. 3

3. Таблица назначения выводов узла.. 3

4. Логическая таблица режимов работы узла.. 4

5. Таблица реальных задержек работы узла.. 4

6. Описание работы узла.. 4

7. Моделирование узла в пакете DesignLab 8. 5

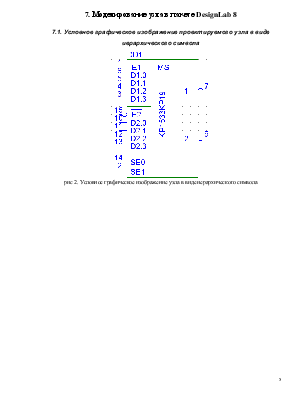

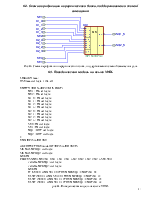

7.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 5

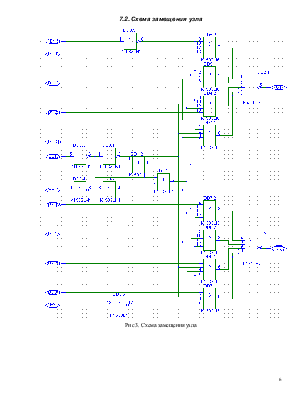

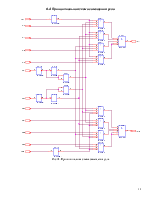

7.2. Схема замещения узла. 6

7.3. Текстовое SPICE-описание моделируемого узла. 7

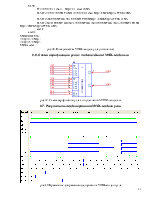

7.4. Файл описания внешних воздействий. 8

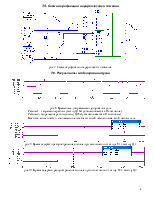

7.5. Схема верификации иерархического символа. 9

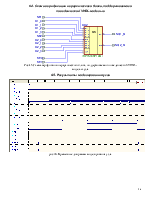

7.6. Результаты моделирования узла. 9

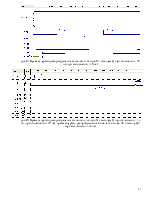

7.7. Функциональное описание проектируемого узла. 12

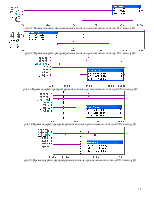

7.8. Схема верификации символа с подключённой макромоделью.. 13

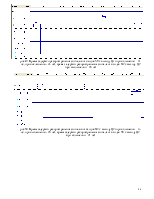

7.9. Результаты моделирования символа с подключённой макромоделью.. 14

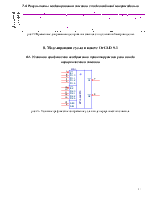

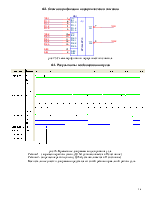

8. Моделирование узла в пакете OrCAD 9.1. 14

8.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 14

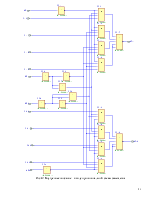

8.2. Принципиальная схема замещения узла. 15

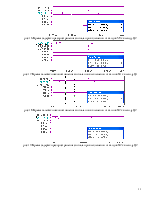

8.3. Схема верификации иерархического символа. 16

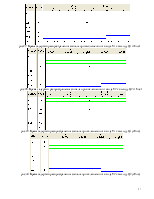

8.4. Результаты моделирования узла. 16

8.5. Поведенческая VHDL-модель узла. 19

8.6. Схема верификации узла с подключённой VHDL-моделью.. 21

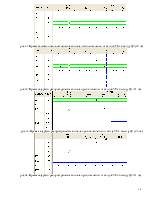

8.7. Результаты моделирования VHDL-модели узла. 21

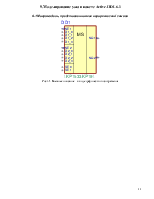

9. Моделирование узла в пакете Active-HDL 6.1. 22

9.1 Макромодель, представленная как иерархический символ. 22

9.2. Схема верификации иерархического блока, поддерживаемого схемой замещения. 24

9.3. Поведенческая модель на языке VHDL. 24

9.4. Схема верификации иерархического блока, поддерживаемого поведенческой VHDL-моделью.. 26

9.5. Результаты моделирования узла. 26

10. Выводы... 29

10.1. Выводы по работе. 29

10.2. Сравнительный анализ использованных пакетов. 29

11. Список использованной литературы... 31

Создать структурные и поведенческие модели исследуемого цифрового узла в пакетах DesignLab 8, OrCad 9.1, Active-HDL 6.1. Провести имитационные эксперименты с разработанным узлом, подтвердить его работоспособность и соответствие временных задержек требуемым. Исследовать возможности используемых инструментальных средств проектирования.

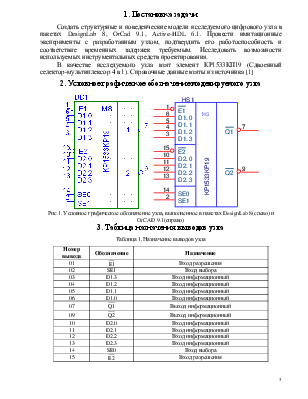

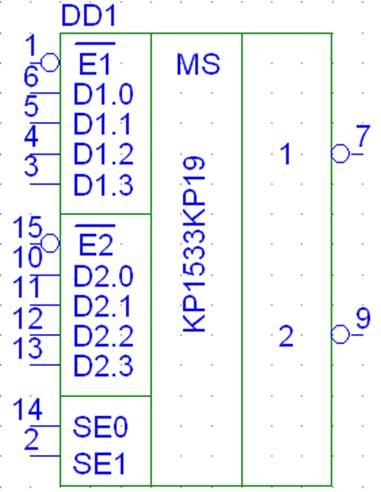

В качестве исследуемого узла взят элемент КР1533КП19 (Сдвоенный селектор-мультиплексор 4 в 1). Справочные данные взяты из источника [1]

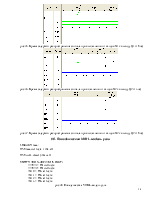

Рис 1. Условное графическое обозначение узла, выполненное в пакетах DesignLab 8(слево) и OrCAD 9.1(справо)

Таблица 1. Назначение выводов узла

|

Номер вывода |

Обозначение |

Назначение |

|

01 |

|

Вход разрешения |

|

02 |

SE1 |

Вход выбора |

|

03 |

D1.3 |

Вход информационный |

|

04 |

D1.2 |

Вход информационный |

|

05 |

D1.1 |

Вход информационный |

|

06 |

D1.0 |

Вход информационный |

|

07 |

|

Выход информационный |

|

09 |

|

Выход информационный |

|

10 |

D2.0 |

Вход информационный |

|

11 |

D2.1 |

Вход информационный |

|

12 |

D2.2 |

Вход информационный |

|

13 |

D2.3 |

Вход информационный |

|

14 |

SE0 |

Вход выбора |

|

15 |

|

Вход разрешения |

Таблица 2. Логическая таблица режимов работы узла

|

Входы |

Выход |

Примечание. |

||||||

|

SE1 |

SE0 |

0 |

1 |

2 |

3 |

|

|

|

|

X |

X |

X |

X |

X |

X |

H |

H |

Запрещение работы (все выходы в H состоянии) |

|

L |

L |

L |

X |

X |

X |

L |

H |

Работа |

|

L |

L |

H |

X |

X |

X |

L |

L |

|

|

L |

H |

X |

L |

X |

X |

L |

H |

|

|

L |

H |

X |

H |

X |

X |

L |

L |

|

|

H |

L |

X |

X |

L |

X |

L |

H |

|

|

H |

L |

X |

X |

H |

X |

L |

L |

|

|

H |

H |

X |

X |

X |

L |

L |

H |

|

|

H |

H |

X |

X |

X |

H |

L |

L |

|

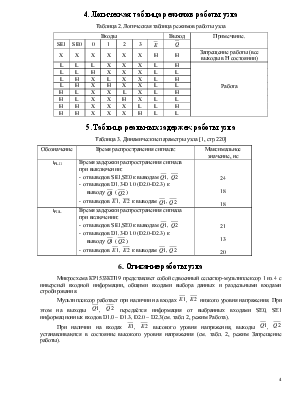

Таблица 3. Динамические параметры узла [1, стр.220]

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.