+ D0_GATE IO_ALS00 IO_LEVEL={IO_LEVEL}

+ LOGIC:

+ NE1_INT = { NE1 }

+ NE2_INT = { NE2 }

+ SE0_INT = { SE0 }

+ SE1_INT = { SE1 }

+ D1_0_INT = { D1_0 }

+ D1_1_INT = { D1_1 }

+ D1_2_INT = { D1_2 }

+ D1_3_INT = { D1_3 }

+ D2_0_INT = { D2_0 }

+ D2_1_INT = { D2_1 }

+ D2_2_INT = { D2_2 }

+ D2_3_INT = { D2_3 }

+ E1 = { ~NE1_INT }

+ E2 = { ~NE2_INT }

+ ABAR = { ~SE0_INT }

+ BBAR = { ~SE1_INT }

+ I0 = { E1 & BBAR & ABAR & D1_0_INT }

+ I1 = { E1 & BBAR & SE0_INT & D1_1_INT }

+ I2 = { E1 & SE1_INT & ABAR & D1_2_INT }

+ I3 = { E1 & SE1_INT & SE0_INT & D1_3_INT }

+ I4 = { E2 & BBAR & ABAR & D2_0_INT }

+ I5 = { E2 & BBAR & SE0_INT & D2_1_INT }

+ I6 = { E2 & SE1_INT & ABAR & D2_2_INT }

+ I7 = { E2 & SE1_INT & SE0_INT & D2_3_INT }

+ NQ1_INT = { ~(I0 | I1 | I2 | I3) }

+ NQ2_INT = { ~(I4 | I5 | I6 | I7) }

*

U1533KP19MDLY PINDLY (2,0,12) DPWR DGND

+ NQ1_INT NQ2_INT

+ NE1_INT NE2_INT SE0_INT SE1_INT D1_0_INT D1_1_INT D1_2_INT D1_3_INT D2_0_INT D2_1_INT D2_2_INT D2_3_INT

+ NQ1 NQ2

+ IO_ALS00

+ MNTYMXDLY = {MNTYMXDLY} IO_LEVEL = {IO_LEVEL}

+ BOOLEAN:

+ DATA1 = { (CHANGED(D1_0_INT,0) | CHANGED(D1_1_INT,0) | CHANGED(D1_2_INT,0) |

рис 20. Файл KP19.lib

+ CHANGED(D1_3_INT,0)) }

+ DATA2 = { (CHANGED(D2_0_INT,0) | CHANGED(D2_1_INT,0) | CHANGED(D2_2_INT,0) |

+ CHANGED(D2_3_INT,0)) }

+ SELECT = { CHANGED(SE0_INT,0) | CHANGED(SE1_INT,0) }

+ PINDLY:

+ NQ1 = {

+ CASE(

+ SELECT & TRN_LH, DELAY(5NS,14.5NS,24NS),

+ SELECT & TRN_HL, DELAY(5NS,13NS,21NS),

+ CHANGED(NE1_INT,0) & TRN_HL, DELAY(4NS,12NS,20NS),

+ CHANGED(NE1_INT,0) & TRN_LH, DELAY(3NS,10NS,18NS),

+ DATA2 & TRN_LH, DELAY(3NS,10NS,18NS),

+ DATA2 & TRN_HL, DELAY(2NS,7.5NS,13NS),

+ DELAY(6NS,15NS,25NS)

+ )

+ }

+ NQ2 = {

+ CASE(

+ SELECT & TRN_LH, DELAY(5NS,14.5NS,24NS),

+ SELECT & TRN_HL, DELAY(5NS,13NS,21NS),

+ CHANGED(NE2_INT,0) & TRN_HL, DELAY(4NS,12NS,20NS),

+ CHANGED(NE2_INT,0) & TRN_LH, DELAY(3NS,10NS,18NS),

+ DATA2 & TRN_LH, DELAY(3NS,10NS,18NS),

+ DATA2 & TRN_HL, DELAY(2NS,7.5NS,13NS),

+ DELAY(6NS,15NS,25NS)

+ )

+ }

*

.ENDS

*

*$

рис 20. Файл KP19.lib (окончание)

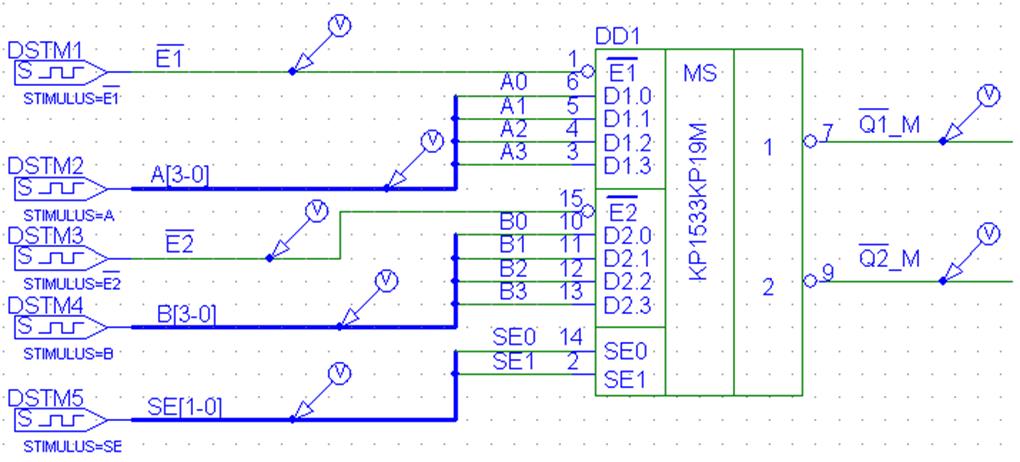

рис 21. Схема верификации символа с подключённой макромоделью

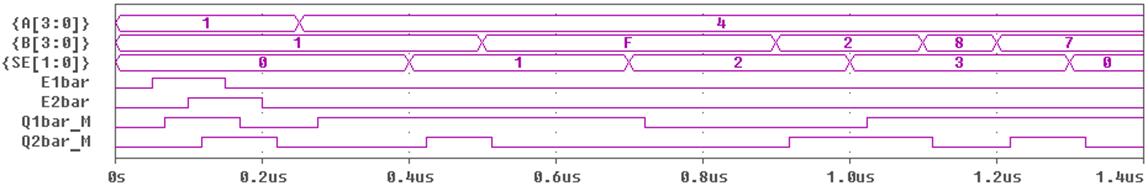

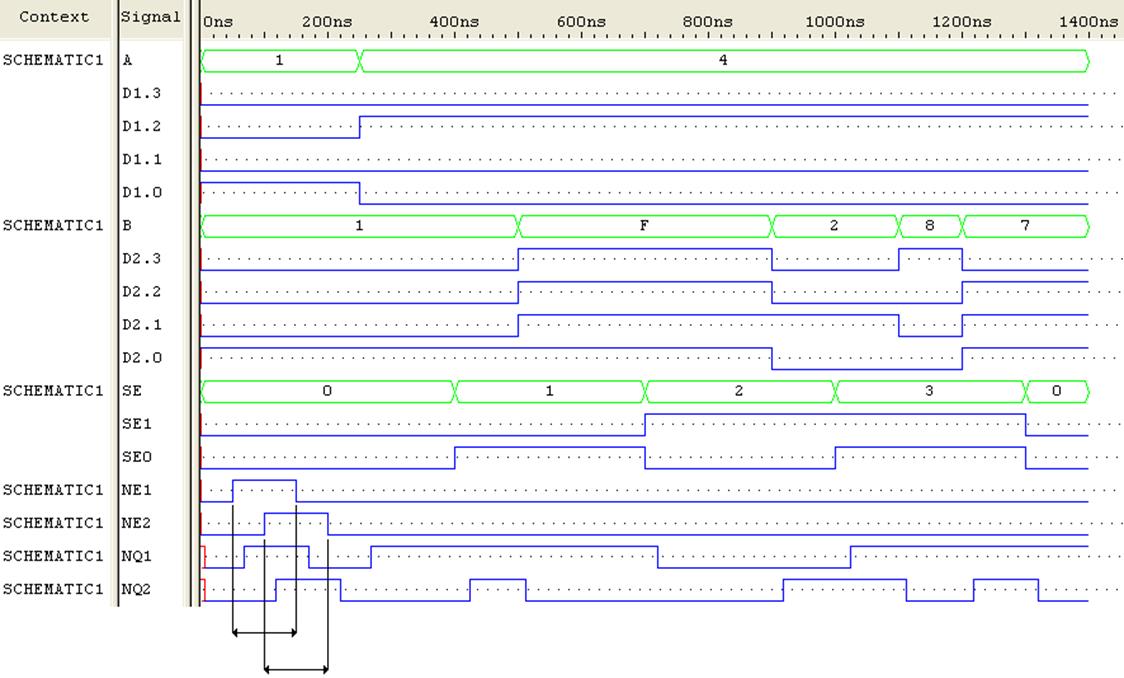

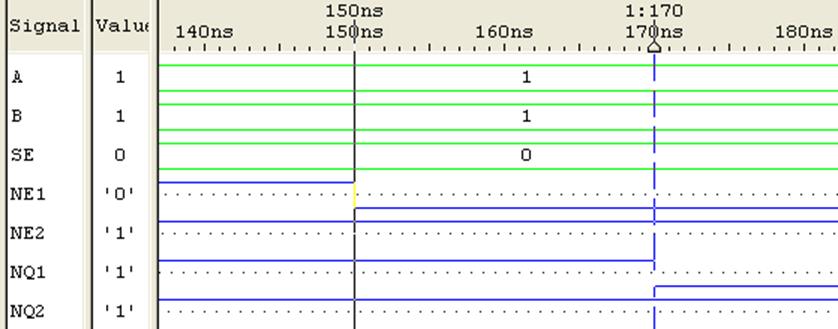

рис 22. Временные диаграммы моделирования символа с подключённой макромоделью

рис 23. Условное графическое изображение узла в виде иерархического символа

Рис 24. Принципиальная схема замещения узла

рис 25. Схема верификации иерархического символа

рис 26. Временные диаграммы моделирования узла

Режим 1 – запрещение работы (выход Q1bar устанавливается в H состояние)

Режим 2 - запрещение работы (выход Q2bar устанавливается в H состояние)

Все остальные участки диаграммы представляют собой режим нормальной работы узла.

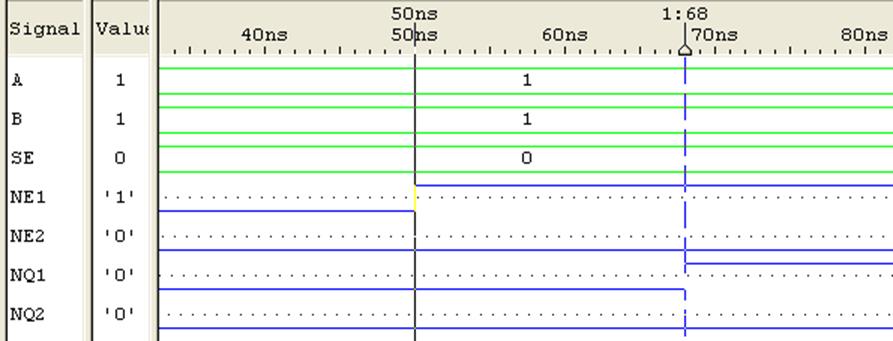

рис 27. Время задержки распространения сигнала при выключении от входа E1 к выходу Q1 (18 нс)

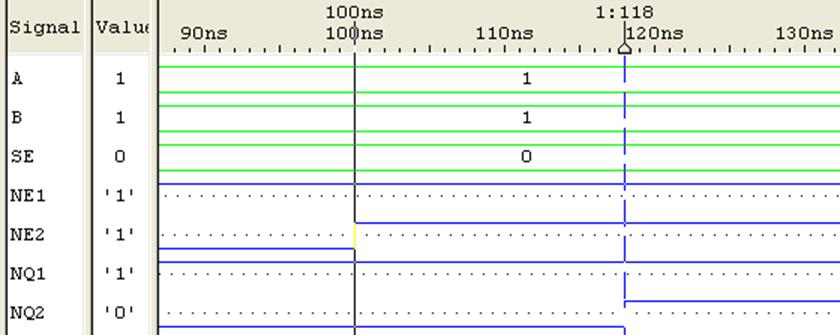

рис 28. Время задержки распространения сигнала при выключении от входа E2 к выходу Q2 (18 нс)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.