end if;

IF NPOQ1'DELAYED = '0' THEN

IF (NE1='1') then NPOQ1<= '1' after 18 NS;

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NPOQ1 <=(NPREQ1) AFTER 24NS;

ELSIF (D1_0'EVENT OR D1_1'EVENT OR D1_2'EVENT OR D1_3'EVENT) THEN NPOQ1 <=(NPREQ1) AFTER 18NS;

end if;

ELSE

IF (NE1='1') then NPOQ1<= '1' after 18NS;

ELSIF (NE1'EVENT AND NE1='0') then NPOQ1 <=NPREQ1 AFTER 20NS;

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NPOQ1 <=NPREQ1 AFTER 21NS;

ELSIF (D1_0'EVENT OR D1_1'EVENT OR D1_2'EVENT OR D1_3'EVENT) THEN NPOQ1 <=NPREQ1 AFTER 13NS;

end if;

end if;

-----------------

IF (SE0='0' AND SE1='0') THEN NPREQ2 := NOT(D2_0);

ELSIF(SE0='1' AND SE1='0') THEN NPREQ2 := NOT(D2_1);

ELSIF (SE0='0' AND SE1='1') THEN NPREQ2 := NOT(D2_2);

ELSIF (SE0='1' AND SE1='1') THEN NPREQ2 := NOT(D2_3);

end if;

IF NPOQ2'DELAYED = '0' THEN

IF (NE2='1') then NPOQ2<= '1' after 18NS;

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NPOQ2 <=(NPREQ2) AFTER 24NS;

ELSIF (D2_0'EVENT OR D2_1'EVENT OR D2_2'EVENT OR D2_3'EVENT) THEN NPOQ2 <=NPREQ2 AFTER 18NS;

end if;

ELSE

IF (NE2='1') then NPOQ2<= '1' after 18NS;

ELSIF (NE2'EVENT AND NE2='0') then NPOQ2 <=NPREQ2 AFTER 20NS;

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NPOQ2 <=NPREQ2 AFTER 21NS;

ELSIF (D2_0'EVENT OR D2_1'EVENT OR D2_2'EVENT OR D2_3'EVENT) THEN NPOQ2 <=NPREQ2 AFTER 13NS;

end if;

end if;

END PROCESS;

NQ1 <= NPOQ1;

NQ2 <= NPOQ2;

END model;

рис 44. Поведенческая модель на языке VHDL (окончание)

Рис 45. Схема верификации иерархического блока, поддерживаемого поведенческой VHDL-моделью узла

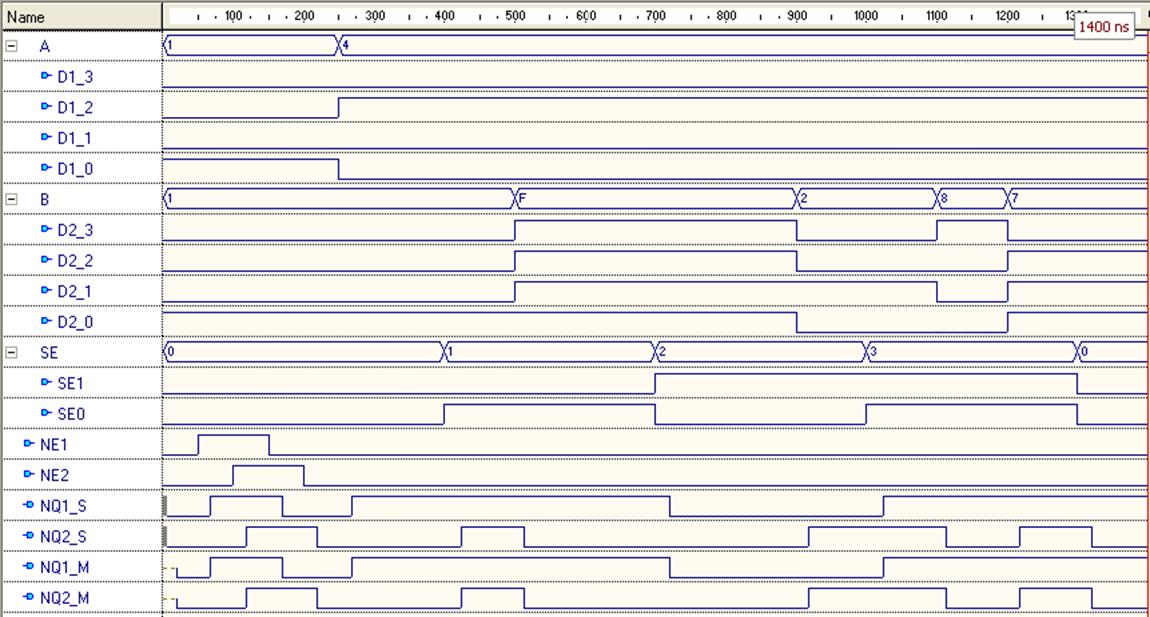

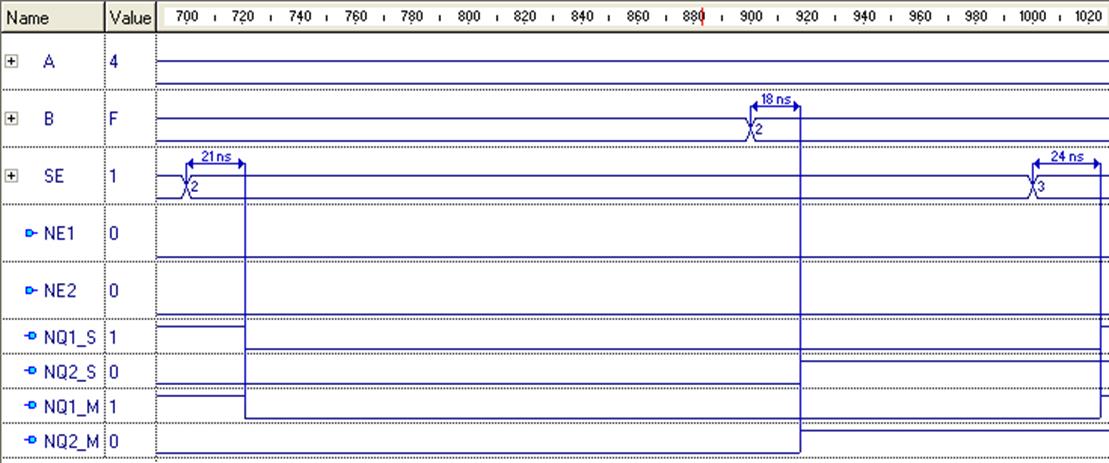

рис 46. Временные диаграммы моделирования узла

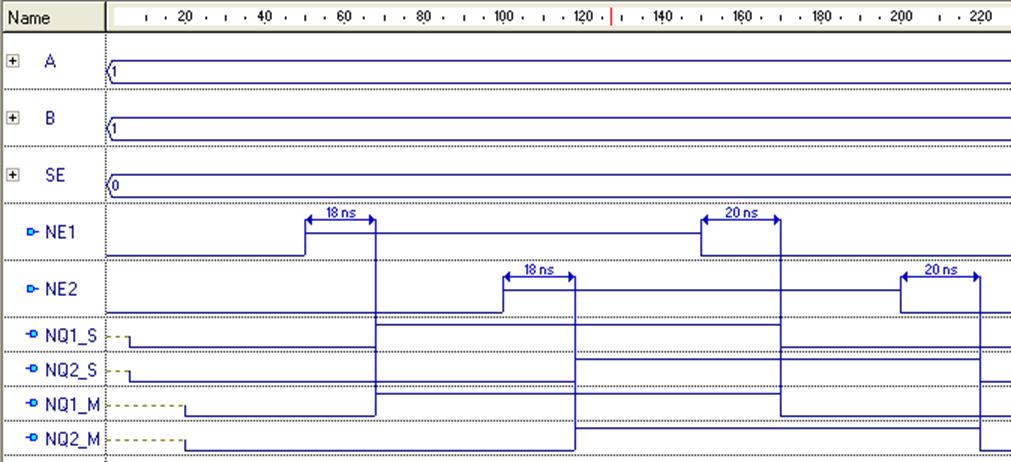

рис 47. Время задержки распространения сигналов от входов E к выходам Q (при включении – 20 нс, при выключении - 18 нс)

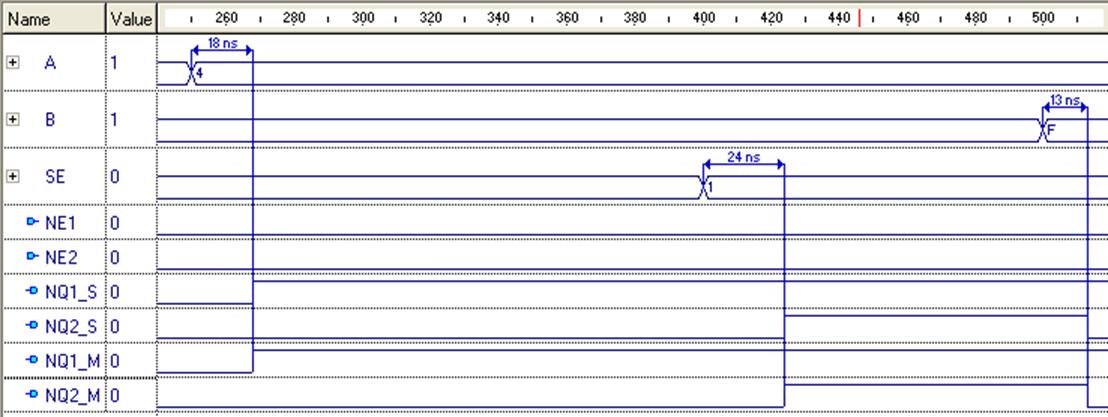

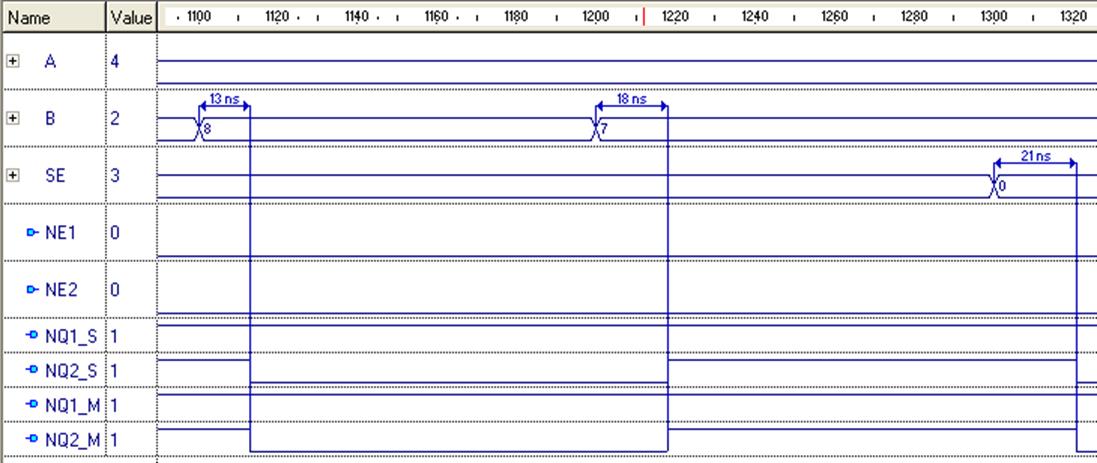

рис 48. Время задержки распространения сигналов от входов D к выходам Q (при включении – 13 нс, при выключении - 18 нс), время задержки распространения сигнала от входов SE к выходу Q2 (при выключении - 24 нс)

рис 49. Время задержки распространения сигналов от входов SE к выходу Q1 (при включении – 21 нс, при выключении - 24 нс), время задержки распространения сигнала от входов D2 к выходу Q2 (при выключении – 18 нс)

рис 50. Время задержки распространения сигналов от входов D2 к выходу Q2 (при включении – 13 нс, при выключении - 18 нс), время задержки распространения сигнала от входов SE к выходу Q2 (при включении – 21 нс)

Моделирование сдвоенного селектора-мультиплексора КР1533КП19 — узла предложенного по варианту было выполнено мною в трёх пакетах. Два из них, DesignLab8 и Orcad 9.1, были освоены мною на лабораторных работах в прошлом семестре, а один совершенно новый для меня, ActiveHDL 6.1,пришлось постигать отчасти самостоятельно, отчасти консультируясь с однокурсниками, успевшими освоить этот пакет заранее.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.