|

Обозначение |

Время распространения сигнала: |

Максимальное значение, нс |

|

tPLH |

Время задержки распространения сигнала при выключении: - от выводов SE1,SE0 к выводам - от выводов D1.3-D1.0 (D2.0-D2.3) к выводу - от выводов |

24 18 18 |

|

tPHL |

Время задержки распространения сигнала при включении: - от выводов SE1,SE0 к выводам - от выводов D1.3-D1.0 (D2.0-D2.3) к выводу - от выводов |

21 13 20 |

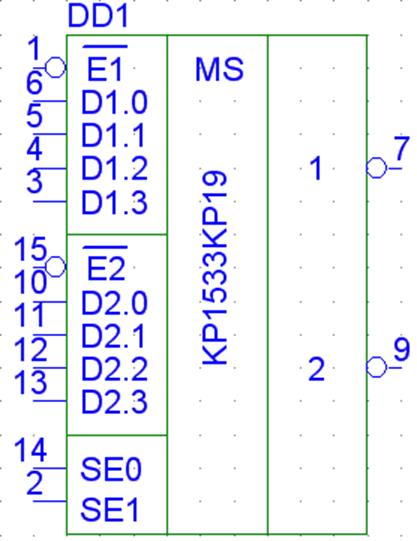

Микросхема КР1533КП19 представляет собой сдвоенный селектор-мультиплексор 1 из 4 с инверсией входной информации, общими входами выбора данных и раздельными входами стробирования.

Мультиплексор

работает при наличии на входах ![]() ,

, ![]() низкого уровня напряжения. При этом на выходы

низкого уровня напряжения. При этом на выходы ![]() ,

, ![]() передаётся информация от выбранных входами SE0,

SE1 информационных входов D1.0 – D1.3, D2.0 – D2.3(см. табл. 2, режим Работа).

передаётся информация от выбранных входами SE0,

SE1 информационных входов D1.0 – D1.3, D2.0 – D2.3(см. табл. 2, режим Работа).

При наличии на

входах ![]() ,

, ![]() высокого уровня напряжения, выходы

высокого уровня напряжения, выходы ![]() ,

, ![]() устанавливаются в состояние высокого уровня

напряжения (см. табл. 2, режим Запрещение работы).

устанавливаются в состояние высокого уровня

напряжения (см. табл. 2, режим Запрещение работы).

рис 2. Условное графическое изображение узла в виде иерархического символа

|

Рис 3. Схема замещения узла

* D:\Study_Sasha\Modelirovanie\KR\DL8\second.sch

* Schematics Version 8.0 - July 1997

* Thu Oct 27 16:47:40 2005

** Analysis setup **

.tran 20ns 1400ns

.OPTIONS DIGMNTYMX=3

.LIB "D:\Study_Sasha\Modelirovanie\KR\DL8\DL8.lib" --библиотека собственных элементов

.STMLIB "D:\Study_Sasha\Modelirovanie\KR\DL8\second.stl" --файл описания внешних воздействий

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "nom.lib"

.INC "second.net"

.INC "second.als"

.probe

.END

Рис 4. Файл second.cir

* Schematics Netlist *

U_DSTM3 STIM(4,0) $G_DPWR $G_DGND A3 A2 A1 A0 IO_STM STIMULUS=A

U_DSTM4 STIM(1,0) $G_DPWR $G_DGND E1bar IO_STM STIMULUS=E1

U_DSTM5 STIM(1,0) $G_DPWR $G_DGND E2bar IO_STM STIMULUS=E2

U_DSTM1 STIM(4,0) $G_DPWR $G_DGND B3 B2 B1 B0 IO_STM STIMULUS=B

U_DSTM2 STIM(2,0) $G_DPWR $G_DGND SE1 SE0 IO_STM STIMULUS=SE

X_DD1_DD1_1 $N_0001 $N_0001 $N_0002 $G_DPWR $G_DGND K1533LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD1_2 $N_0003 $N_0003 $N_0004 $G_DPWR $G_DGND K1533LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD2_1 $N_0005 $N_0006 $N_0007 $N_0008 $N_0008 Q1bar $G_DPWR

+ $G_DGND K531LE7 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD3_1 $N_0003 $N_0009 $G_DPWR $G_DGND K1533LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD3_2 $N_0001 $N_0010 $G_DPWR $G_DGND K1533LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD3_3 SE1 $N_0003 $G_DPWR $G_DGND K1533LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD3_4 SE0 $N_0001 $G_DPWR $G_DGND K1533LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD4_1 $N_0011 $N_0009 $N_0010 A3 $N_0008 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD4_2 $N_0011 $N_0009 $N_0002 A2 $N_0007 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD5_1 $N_0011 $N_0004 $N_0010 A1 $N_0006 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD5_2 $N_0011 $N_0004 $N_0002 A0 $N_0005 $G_DPWR $G_DGND K1533LI6

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.