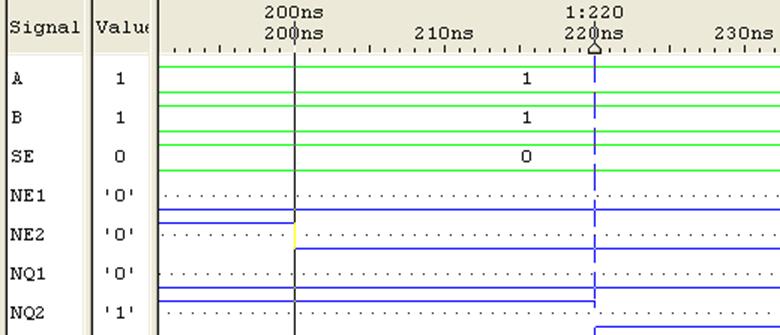

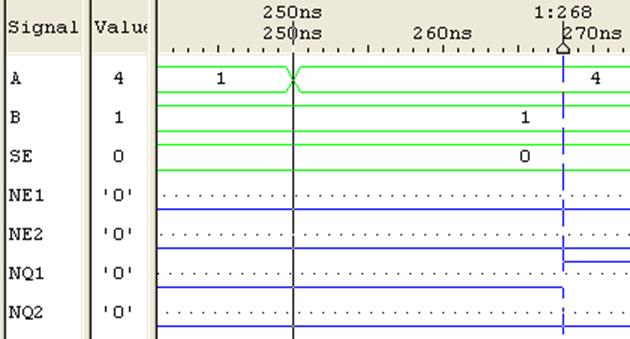

рис 29. Время задержки распространения сигнала при включении от входа E1 к выходу Q1 (20 нс)

рис 30. Время задержки распространения сигнала при включении от входа E2 к выходу Q2 (20 нс)

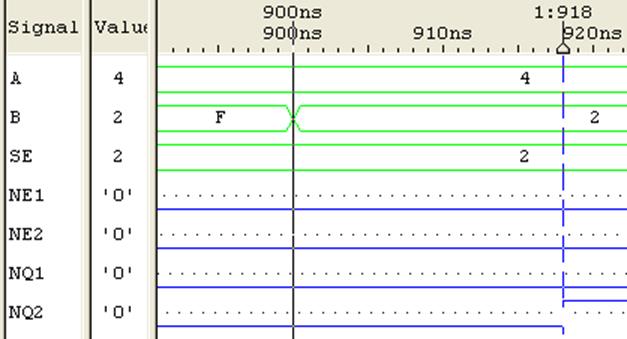

рис 31. Время задержки распространения сигнала при выключении от входов SE к выходу Q2 (24 нс)

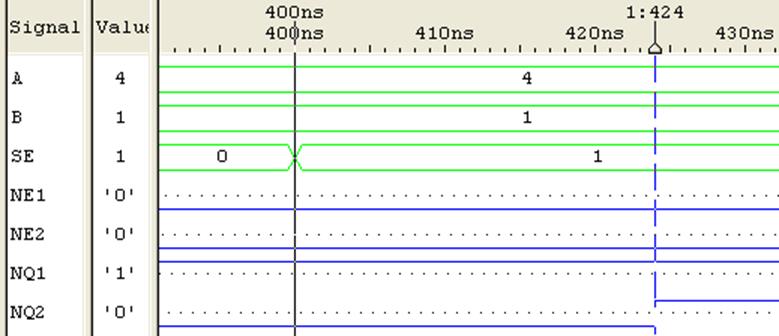

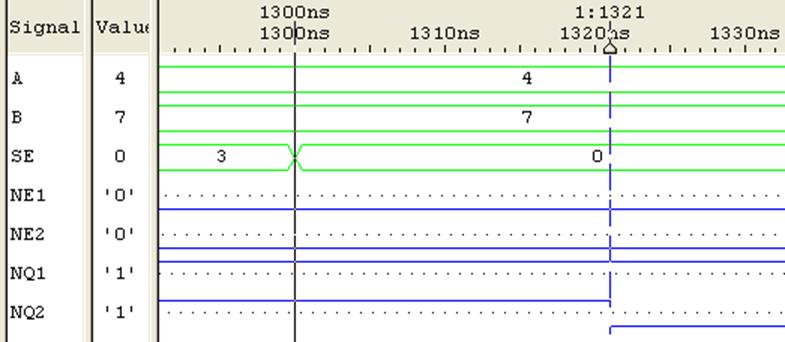

рис 32. Время задержки распространения сигнала при включении от входов SE к выходу Q1 (21 нс)

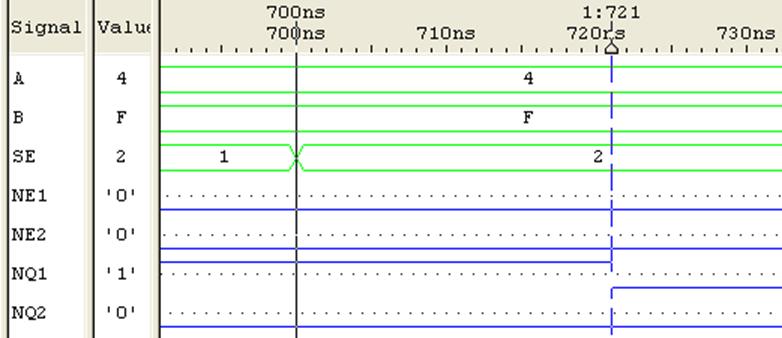

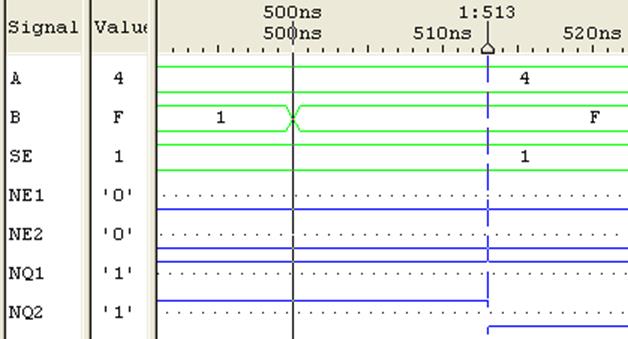

рис 33. Время задержки распространения сигнала при выключении от входа SE к выходу Q1 (24 нс)

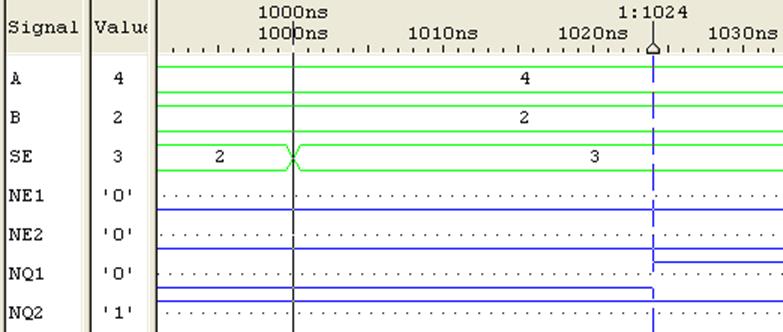

рис 34. Время задержки распространения сигнала при включении от входов SE к выходу Q2 (21 нс)

рис 35. Время задержки распространения сигнала при выключении от входов D1 к выходу Q1 (18 нс)

рис 36. Время задержки распространения сигнала при включении от входов D2 к выходу Q2 (13 нс)

рис 37. Время задержки распространения сигнала при выключении от входов D2 к выходу Q2 (18 нс)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \KP1533KP19M\ IS PORT(

\\\\\E\\1\ : IN std_logic;

\\\\\E\\2\ : IN std_logic;

\D1.0\ : IN std_logic;

\D1.1\ : IN std_logic;

\D1.2\ : IN std_logic;

\D1.3\ : IN std_logic;

рис 38. Поведенческая VHDL-модель узла

\D2.0\ : IN std_logic;

\D2.1\ : IN std_logic;

\D2.2\ : IN std_logic;

\D2.3\ : IN std_logic;

SE0 : IN std_logic;

SE1 : IN std_logic;

\\\\\Q\\1\ : OUT std_logic;

\\\\\Q\\2\ : OUT std_logic

);

END \KP1533KP19M\;

ARCHITECTURE model OF \KP1533KP19M\ IS

SIGNAL NQ1: std_logic;

SIGNAL NQ2: std_logic;

BEGIN

PROCESS(\\\\\E\\1\,\\\\\E\\2\,\D1.0\,\D1.1\,\D1.2\,\D1.3\,\D2.0\,\D2.1\,\D2.2\,\D2.3\,SE0,SE1)

variable NPREQ1: std_logic; --переменные для хранения возможного значения для

variable NPREQ2: std_logic; -- выхода

BEGIN

IF (SE0='0' AND SE1='0') THEN NPREQ1 := NOT(\D1.0\); --подготовка

ELSIF(SE0='1' AND SE1='0') THEN NPREQ1 := NOT(\D1.1\); --к мультиплексированию

ELSIF (SE0='0' AND SE1='1') THEN NPREQ1 := NOT(\D1.2\);

ELSIF (SE0='1' AND SE1='1') THEN NPREQ1 := NOT(\D1.3\);

end if;

IF NQ1'DELAYED = '0' THEN --переключение из 0 в 1(выключение)

IF (\\\\\E\\1\='1') then NQ1<= '1' after 18NS; --переход в Н состояние

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NQ1 <=(NPREQ1) AFTER 24NS; -- изменение данных на выходе из-за смены данных на селекторных входах

ELSIF (\D1.0\'EVENT OR \D1.1\'EVENT OR \D1.2\'EVENT OR \D1.3\'EVENT) THEN NQ1 <=(NPREQ1) AFTER 18NS; --изменение данных на выходе из-за смены данных на информационных входах

end if;

ELSE --переключение из 1 в 0(включение)

IF (\\\\\E\\1\='1') then NQ1<= '1' after 18NS; --переход в Н состояние

ELSIF (\\\\\E\\1\'EVENT AND \\\\\E\\1\='0') then NQ1 <=NPREQ1 AFTER 20NS; -- выходи из Н состояния в рабочий режим

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NQ1 <=NPREQ1 AFTER 21NS; -- изменение данных на выходе из-за смены данных на селекторных входах

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.