+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD3_5 E1bar $N_0011 $G_DPWR $G_DGND K1533LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Рис 5. Файл second.net

X_DD1_DD6_1 B2 $N_0009 $N_0002 $N_0013 $N_0012 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD3_6 E2bar $N_0013 $G_DPWR $G_DGND K1533LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD6_2 B1 $N_0004 $N_0010 $N_0013 $N_0014 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD7_1 B3 $N_0009 $N_0010 $N_0013 $N_0015 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD7_2 B0 $N_0004 $N_0002 $N_0013 $N_0016 $G_DPWR $G_DGND K1533LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD2_2 $N_0016 $N_0014 $N_0012 $N_0015 $N_0015 Q2bar $G_DPWR

+ $G_DGND K531LE7 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Рис 5. Файл second.net (окончание)

* D:\Study_Sasha\Modelirovanie\KR\DL8\second.stl written on Wed Oct 19 23:20:04 2005

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! A Digital B Digital SE Digital E1 Digital E2 Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 1.4us

;!AutoUniverse

;!XminRes 50ns

;!YminRes 1n

;!Ok

.STIMULUS E2 STIM (1, 1)

+ +0s 0

+ 100ns 1

+ 200ns 0

.STIMULUS E1 STIM (1, 1)

+ +0s 0

+ 50ns 1

+ 150ns 0

.STIMULUS A STIM (4, 1111) ;! Hex

+ +0s 0001

+ 250ns 0100

.STIMULUS B STIM (4, 1111) ;! Hex

+ +0s 0001

+ 500ns 1111

+ 900ns 0010

+ 1.1us 1000

+ 1.2us 0111

.STIMULUS SE STIM (2, 11) ;! Hex

+ +0s 00

+ 400ns 01

+ 700ns 10

+ 1us 11

+ 1.3us 00

Рис 6. Файл second.stl

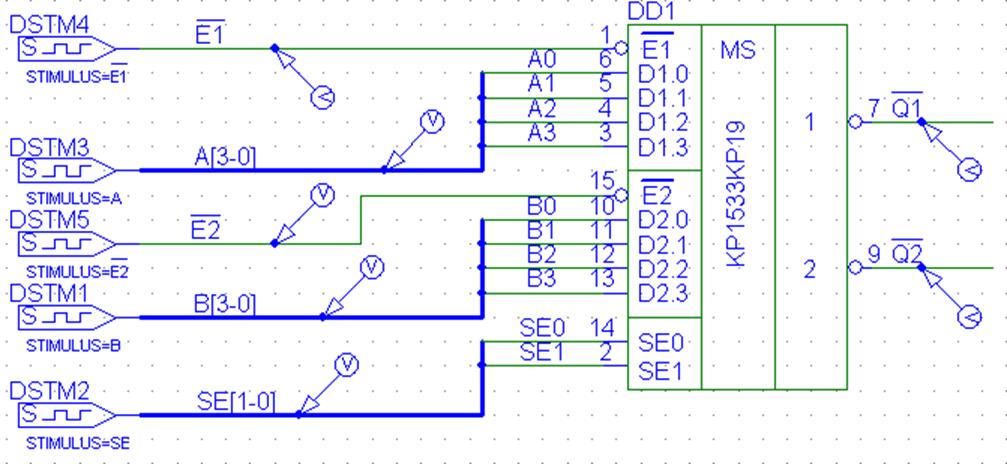

рис 7. Схема верификации иерархического символа

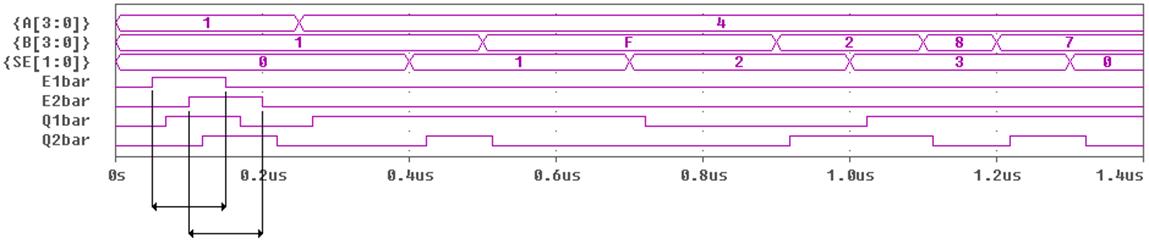

рис 8. Временные диаграммы моделирования узла

Режим 1 – запрещение работы (выход Q1bar устанавливается в H состояние)

Режим 2 - запрещение работы (выход Q2bar устанавливается в H состояние)

Все остальные участки диаграммы представляют собой режим нормальной работы узла.

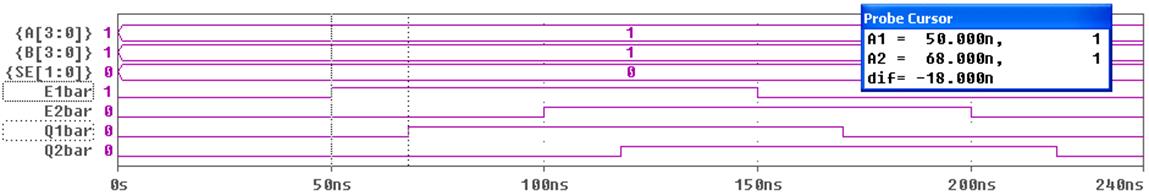

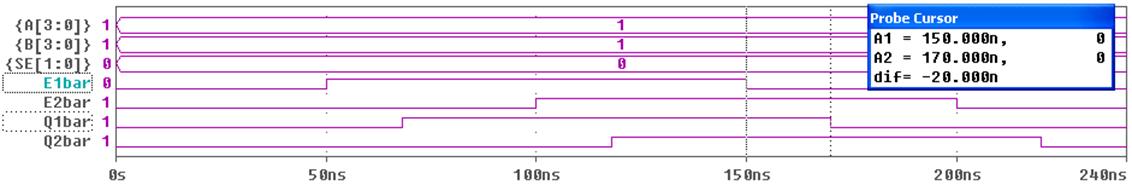

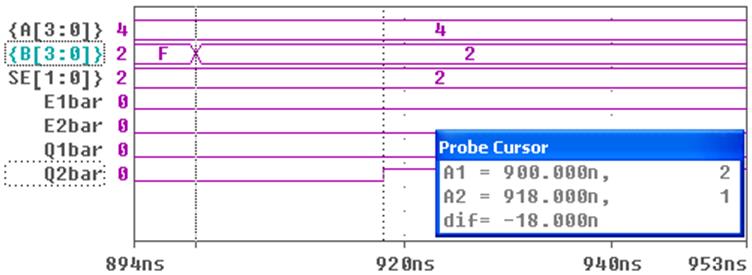

рис 9. Время задержки распространения сигнала при выключении от входа E1 к выходу Q1

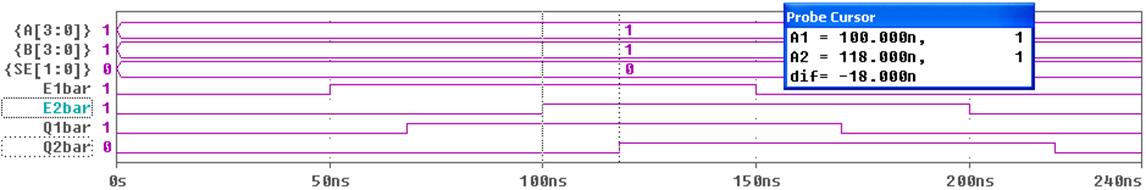

рис 10. Время задержки распространения сигнала при выключении от входа E2 к выходу Q2

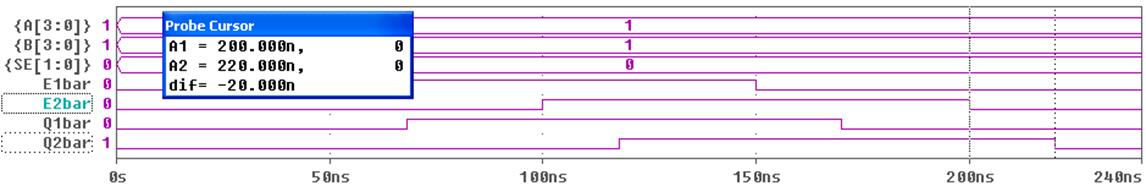

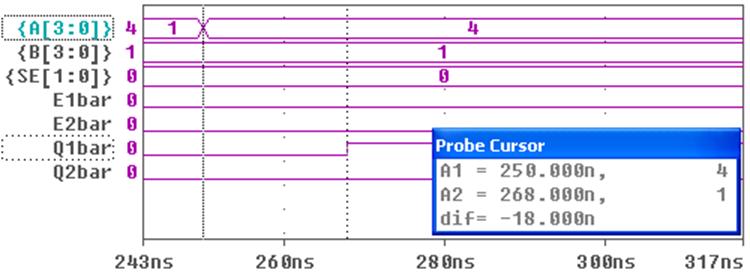

рис 11. Время задержки распространения сигнала при включении от входа E1 к выходу Q1

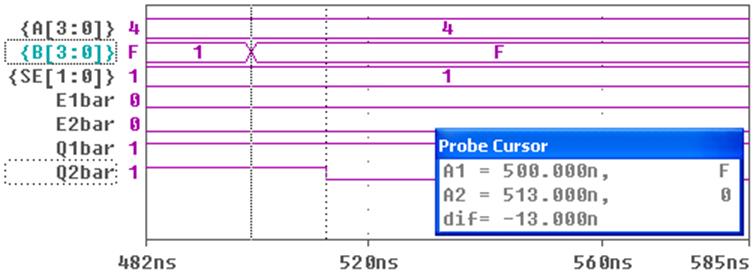

рис 12. Время задержки распространения сигнала при включении от входа E2 к выходу Q2

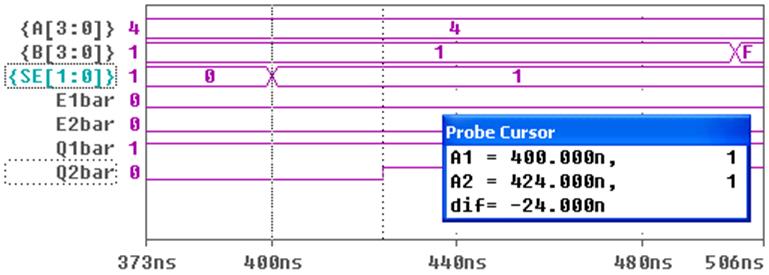

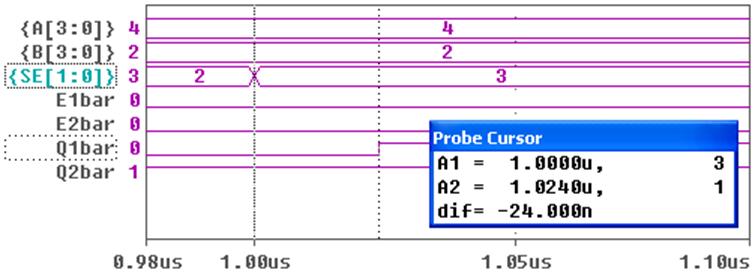

рис 13. Время задержки распространения сигнала при выключении от входов SE к выходу Q2

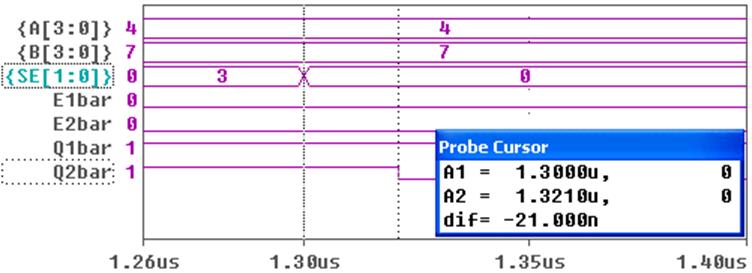

рис 14. Время задержки распространения сигнала при включении от входов SE к выходу Q1

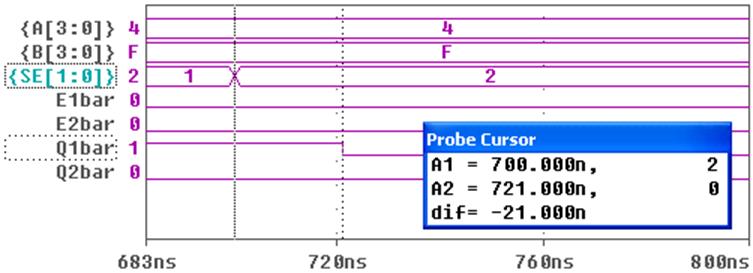

рис 15. Время задержки распространения сигнала при выключении от входа SE к выходу Q1

рис 16. Время задержки распространения сигнала при включении от входов SE к выходу Q2

рис 17. Время задержки распространения сигнала при выключении от входов D1 к выходу Q1

рис 18. Время задержки распространения сигнала при включении от входов D2 к выходу Q2

рис 19. Время задержки распространения сигнала при выключении от входов D2 к выходу Q2

* KP1533KP19M Сдвоенный селектор-мультиплексор 4-1

*

* The ALS/AS Data Book, 1986, TI

* JSW 8/24/92 Remodeled using LOGICEXP, PINDLY, & CONSTRAINT devices

*

.SUBCKT KP1533KP19M NE1 NE2 SE0 SE1 D1_0 D1_1 D1_2 D1_3

+ D2_0 D2_1 D2_2 D2_3 NQ1 NQ2

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

U1533KP19MLOG LOGICEXP(12,14) DPWR DGND

+ NE1 NE2 SE0 SE1 D1_0 D1_1 D1_2 D1_3 D2_0 D2_1 D2_2 D2_3

+ NE1_INT NE2_INT SE0_INT SE1_INT D1_0_INT D1_1_INT D1_2_INT D1_3_INT D2_0_INT D2_1_INT D2_2_INT D2_3_INT NQ1_INT NQ2_INT

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.