ELSIF (\D1.0\'EVENT OR \D1.1\'EVENT OR \D1.2\'EVENT OR \D1.3\'EVENT) THEN NQ1 <=NPREQ1 AFTER 13NS; --изменение данных на выходе из-за смены данных на информационных входах

end if;

end if;

-----------------

IF (SE0='0' AND SE1='0') THEN NPREQ2 := NOT(\D2.0\);

ELSIF(SE0='1' AND SE1='0') THEN NPREQ2 := NOT(\D2.1\);

ELSIF (SE0='0' AND SE1='1') THEN NPREQ2 := NOT(\D2.2\);

ELSIF (SE0='1' AND SE1='1') THEN NPREQ2 := NOT(\D2.3\);

end if;

IF NQ2'DELAYED = '0' THEN

IF (\\\\\E\\2\='1') then NQ2<= '1' after 18NS;

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NQ2 <=(NPREQ2) AFTER 24NS;

ELSIF (\D2.0\'EVENT OR \D2.1\'EVENT OR \D2.2\'EVENT OR \D2.3\'EVENT) THEN NQ2 <=NPREQ2 AFTER 18NS;

end if;

рис 38. Поведенческая VHDL-модель узла (продолжение)

ELSE

IF (\\\\\E\\2\='1') then NQ2<= '1' after 18NS;

ELSIF (\\\\\E\\2\'EVENT AND \\\\\E\\2\='0') then NQ2 <=NPREQ2 AFTER 20NS;

ELSIF (SE0'EVENT OR SE1'EVENT) THEN NQ2 <=NPREQ2 AFTER 21NS;

ELSIF (\D2.0\'EVENT OR \D2.1\'EVENT OR \D2.2\'EVENT OR \D2.3\'EVENT) THEN NQ2 <=NPREQ2 AFTER 13NS;

end if;

end if;

END PROCESS;

\\\\\Q\\1\ <= NQ1;

\\\\\Q\\2\ <= NQ2;

END model;

рис 38. Поведенческая VHDL-модель узла (окончание)

рис 39. Схема верификации узла с подключенной VHDL-моделью

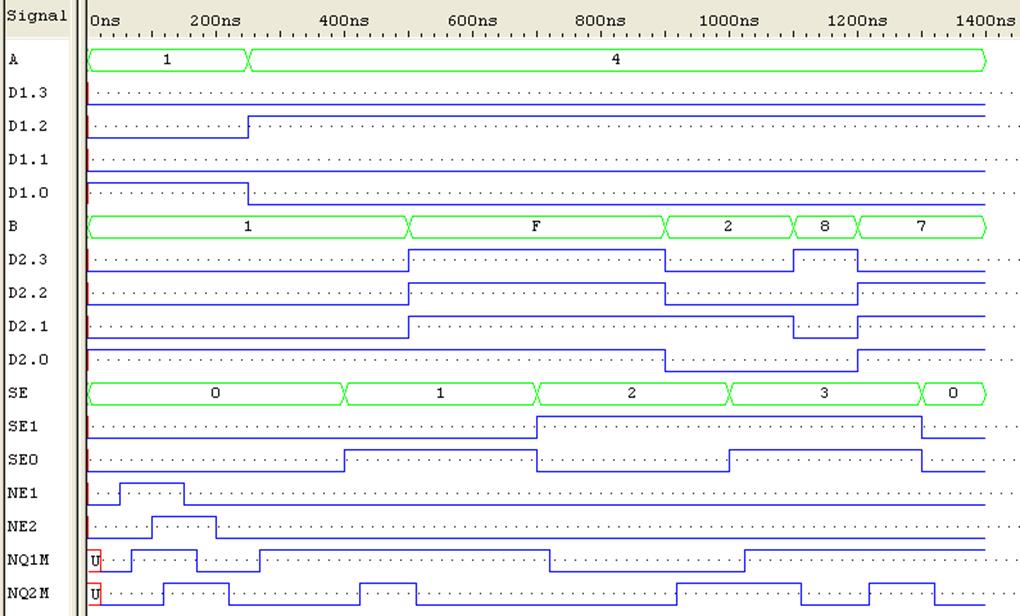

рис 40. Временные диаграммы моделирования VHDL-модели узла

Рис 41. Внешнее описание – в виде графического изображения

Рис 42. Внутреннее описание – в виде принципиальной схемы замещения

Рис 43. Схема верификации иерархического блока, поддерживаемого схемой замещения узла

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY \KP1533KP19M\ IS PORT(

NE1 : IN std_logic;

NE2 : IN std_logic;

D1_0 : IN std_logic;

D1_1 : IN std_logic;

D1_2 : IN std_logic;

D1_3 : IN std_logic;

D2_0 : IN std_logic;

D2_1 : IN std_logic;

D2_2 : IN std_logic;

D2_3 : IN std_logic;

SE0 : IN std_logic;

SE1 : IN std_logic;

NQ1 : OUT std_logic;

NQ2 : OUT std_logic

);

END \KP1533KP19M\;

ARCHITECTURE model OF \KP1533KP19M\ IS

SIGNAL NPOQ1: std_logic;

SIGNAL NPOQ2: std_logic;

BEGIN

PROCESS(NE1,NE2,D1_0,D1_1,D1_2,D1_3,D2_0,D2_1,D2_2,D2_3,SE0,SE1)

variable NPREQ1: std_logic;

variable NPREQ2: std_logic;

BEGIN

IF (SE0='0' AND SE1='0') THEN NPREQ1 := NOT(D1_0);

ELSIF(SE0='1' AND SE1='0') THEN NPREQ1 := NOT(D1_1);

ELSIF (SE0='0' AND SE1='1') THEN NPREQ1 := NOT(D1_2);

ELSIF (SE0='1' AND SE1='1') THEN NPREQ1 := NOT(D1_3);

рис 44. Поведенческая модель на языке VHDL

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.