Министерство образования и науки РФ

Федеральное агентство по образованию

Государственное образовательное учреждение

высшего профессионального образования

Новосибирский государственный технический университет

Кафедра ВТ

|

Пояснительная записка к курсовой работе по

дисциплине

|

|||||

|

|||||

|

|||||

Факультет: АВТ

Группа: АМ-411

Группа: АМ-411

Студент: Сероштан В.Ю.

Преподаватель:

Шалагинов А. В.

Преподаватель:

Шалагинов А. В.

Новосибирск 2007 г.

Содержание

1. Постановка задачи.. 3

2. Условное графическое обозначение моделируемого узла.. 3

3. Таблица назначения выводов узла.. 3

4. Логическая таблица режимов работы узла.. 4

5. Таблица реальных задержек работы узла.. 4

6. Описание работы узла.. 4

7. Моделирование узла в пакете DesignLab 8. 5

7.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 5

7.2. Схема замещения узла. 6

7.3. Текстовое SPICE-описание моделируемого узла. 8

7.4. Файл описания внешних воздействий. 8

7.5. Схема верификации иерархического символа. 9

7.6. Результаты моделирования узла. 9

7.7. Оценка предельных скоростных возможностей исследуемого узла. 10

7.8. Функциональное описание проектируемого узла. 11

7.9. Схема верификации символа с подключённой макромоделью.. 12

7.10. Результаты моделирования символа с подключённой макромоделью.. 13

8. Моделирование узла в пакете OrCAD 9.1. 14

8.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 14

8.2. Принципиальная схема замещения узла. 14

8.3. Схема верификации иерархического символа. 15

8.4. Результаты моделирования узла. 16

8.5. Поведенческая VHDL-модель узла. 17

8.6. Схема верификации узла с подключённой VHDL-моделью.. 18

8.7. Результаты моделирования VHDL-модели узла. 19

9. Моделирование узла в пакете Active-HDL 6.1. 20

9.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 20

9.2. Принципиальная схема замещения узла. 20

9.3. Поведенческая модель на языке VHDL. 22

9.4. Схема верификации иерархического блока, поддерживаемого схемой замещения и поведенческой VHDL-моделью.. 23

9.5. Результаты моделирования иерархического блока со схемой замещения и поведенческой VHDL-моделью.. 23

10. Выводы... 26

10.1. Выводы по работе. 26

10.2. Сравнительный анализ использованных пакетов. 26

11. Список использованной литературы... 28

Создать структурные и поведенческие модели исследуемого цифрового узла в пакетах DesignLab 8, OrCAD 9.1, Active-HDL 6.1. Провести имитационные эксперименты с разработанным узлом, подтвердить его работоспособность и соответствие временных задержек требуемым. Исследовать возможности используемых инструментальных средств проектирования.

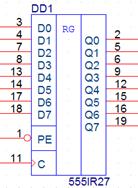

В качестве исследуемого узла взят элемент К555ИР27 (Восьмиразрядный регистр с параллельным входом).

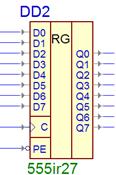

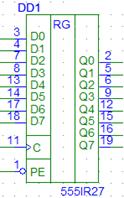

Ниже представлены условные графические обозначения моделируемого узла в пакетах DesignLab 8 (рис. 1. слева) и OrCAD 9.1 (рис. 1. посередине) и Active HGL 6.2 (справа).

|

|

|

|

Рис. 1. Условное графическое обозначение узла, выполненное в пакетах DesignLab 8, OrCAD 9. и Active HDL 6.2 (слева направо).

Таблица 1. Назначение выводов узла

|

Номер вывода |

Обозначение |

Назначение |

|

01 |

|

Вход разрешения |

|

02 |

Q0 |

Выход информационный |

|

03 |

D0 |

Вход информационный |

|

04 |

D1 |

Вход информационный |

|

05 |

Q1 |

Выход информационный |

|

06 |

Q2 |

Выход информационный |

|

07 |

D2 |

Вход информационный |

|

08 |

D3 |

Вход информационный |

|

09 |

Q3 |

Выход информационный |

|

10 |

GND |

Земля |

|

11 |

C |

Синхронный тактовый вход |

|

12 |

Q4 |

Выход информационный |

|

13 |

D4 |

Вход информационный |

|

14 |

D5 |

Вход информационный |

|

15 |

Q5 |

Выход информационный |

|

16 |

Q6 |

Выход информационный |

|

17 |

D6 |

Вход информационный |

|

18 |

D7 |

Вход информационный |

|

19 |

Q7 |

Выход информационный |

|

20 |

VCC |

Напряжение питания |

Таблица 2. Логическая таблица режимов работы узла

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.