Рис 14. Файл 555IR27.MOD

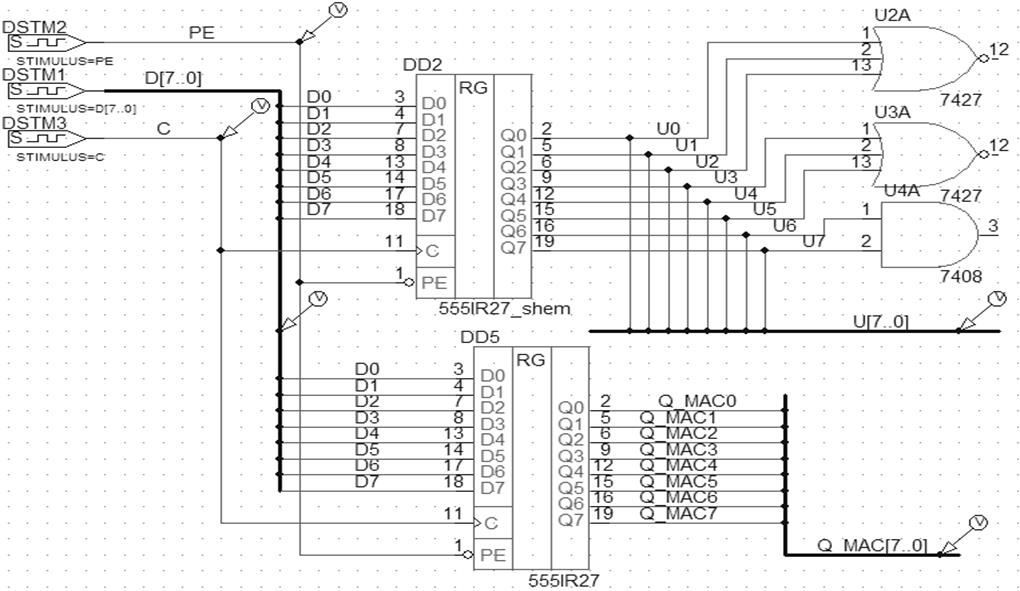

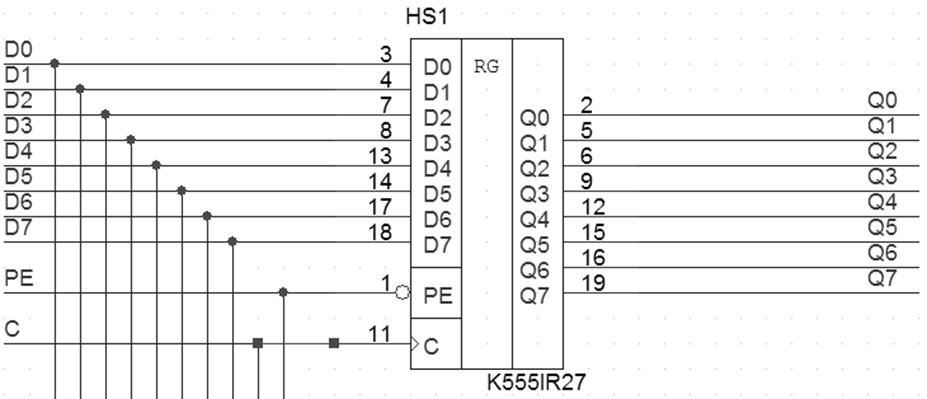

Схема верификации символа с подключённой к нему макромоделью представлена на рис. 13.

Рис 15. Схема верификации символа с подключённой макромоделью элемент DD5.

|

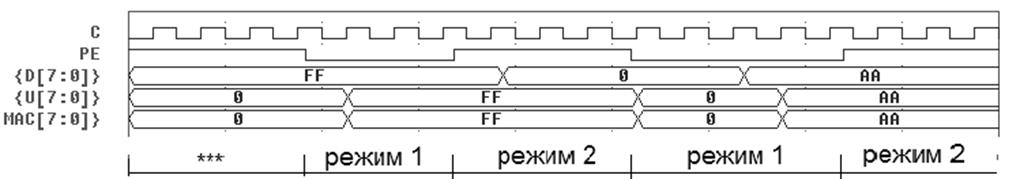

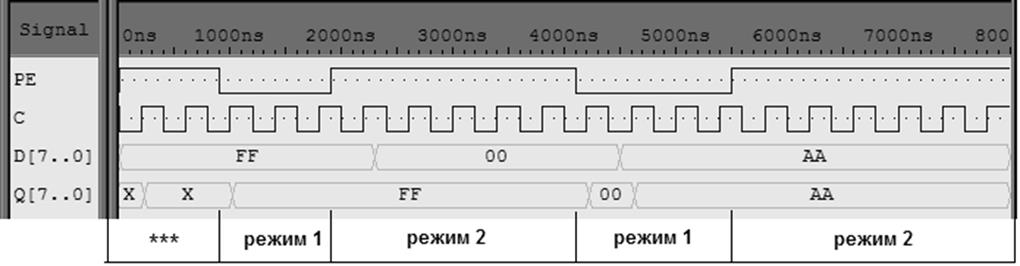

Рис 16. Временные диаграммы моделирования символа с подключённой макромоделью.

Режим 1 – запись (вход PE устанавливается в L состояние)

Режим 2 – хранение (вход PE устанавливается в H состояние)

MAC(7..0) - Выход информационный (макромодель).

Задержки макромодели (зарубежный аналог 74LS377) и элемента 555IR27_shem(со схемой замещения) сходятся.

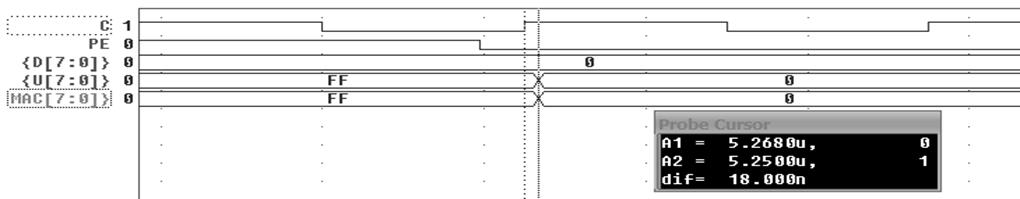

Рис 17. Сравнение задержек распространения сигнала при включении (tPHL) от входа С к выходу U7…U0 и MAC7…MAC0.

Дальнейшее рассмотрение задержек не имеет смысла, так как они идентичны.

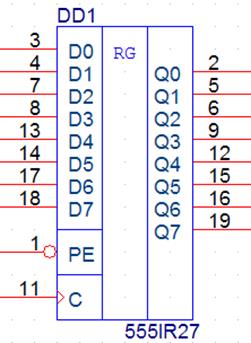

Иерархический символ проектируемого узла представлен на рис. 16.

Рис 18. Условное графическое изображение узла в виде иерархического символа

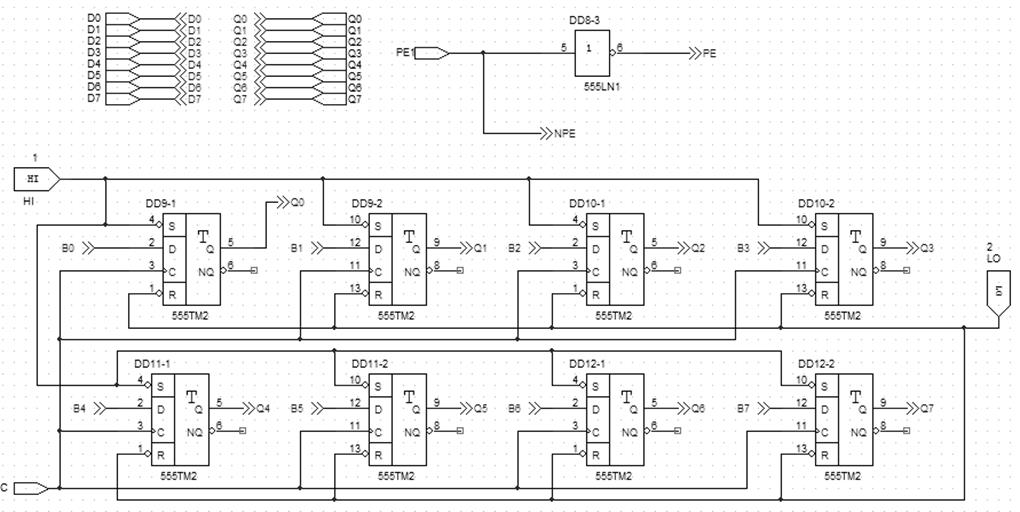

Рис 19. Принципиальная схема замещения узла страница №1

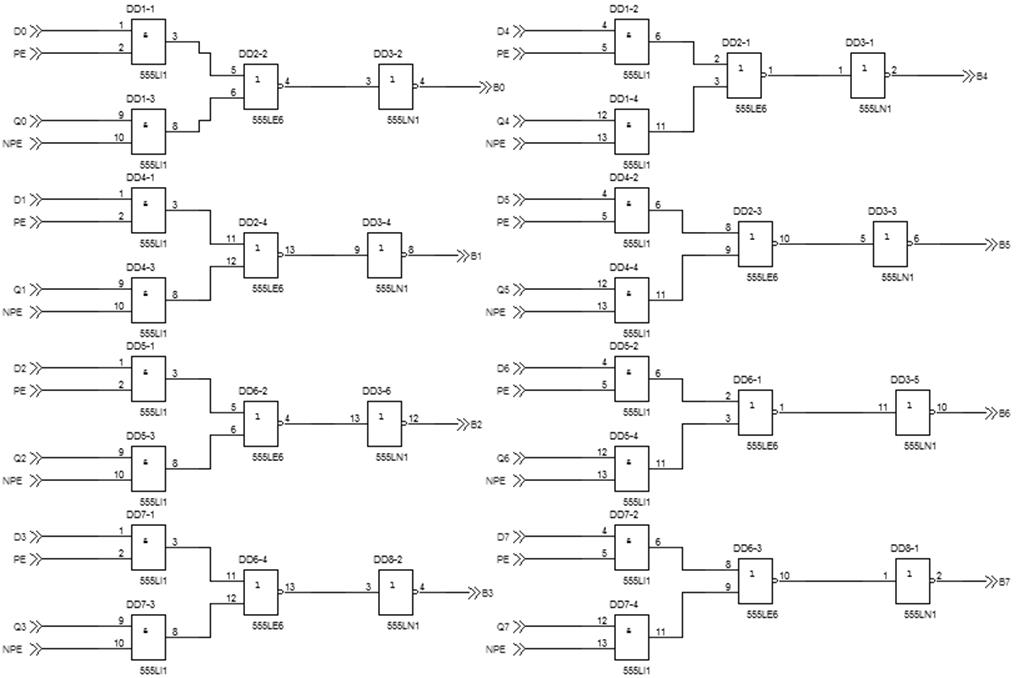

Рис 20. Принципиальная схема замещения узла страница №2

Рис 21. Схема верификации иерархического символа

Рис 22. Временные диаграммы моделирования узла

На приведённых ниже временных диаграммах показаны все случаи задержек распространения сигналов.

Режим 1 – запись (вход PE устанавливается в L состояние)

Режим 2 – хранение (вход PE устанавливается в H состояние)

C – Синхронный тактовый вход.

PE – Вход разрешения.

D(7..0) – Вход информационный.

Q(7..0) – Выход информационный (схема замещения).

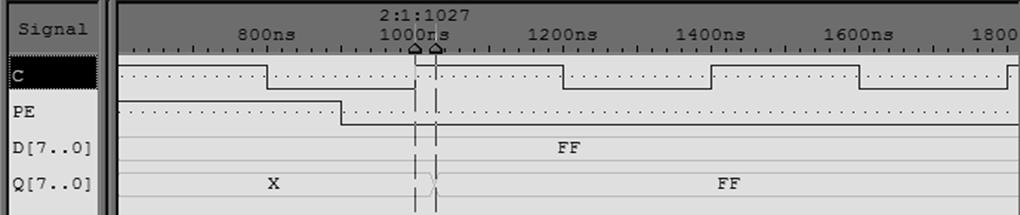

Рис 23. Время задержки распространения сигнала при выключении (tPLH) от входа С к выходу Q7…Q0 (27нс).

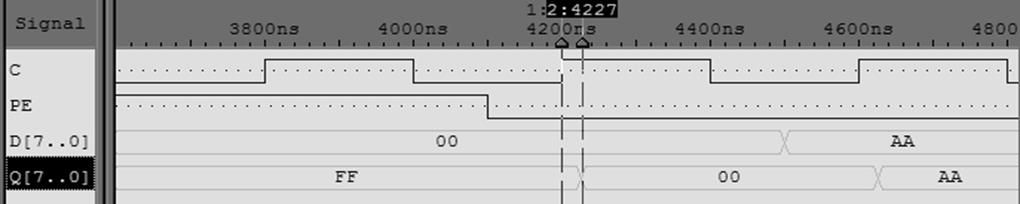

Рис 24. Время задержки распространения сигнала при включении (tPHL) от входа С к выходу Q7…Q0 (27нс).

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \555IR27\ IS PORT(

D0 : IN std_logic;

D1 : IN std_logic;

D2 : IN std_logic;

D3 : IN std_logic;

D4 : IN std_logic;

D5 : IN std_logic;

D6 : IN std_logic;

PE : IN std_logic;

D7 : IN std_logic;

C : IN std_logic;

Q0 : OUT std_logic;

Q1 : OUT std_logic;

Q2 : OUT std_logic;

Q3 : OUT std_logic;

Q4 : OUT std_logic;

Q5 : OUT std_logic;

Q6 : OUT std_logic;

Q7 : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \555IR27\;

ARCHITECTURE model OF \555IR27\ IS

signal Q_INT : std_logic_vector (0 to 7);

begin

process(D0,D1,D2,D3,D4,D5,D6,D7,C,PE)

begin

IF PE = '1' and C = '1' and C'EVENT then

Q_INT(0 to 7) <= Q_INT(0 to 7) after 17ns;

elsif PE = '0' and C = '1' and C'EVENT then

Q_INT(0)<=D0 after 27ns;

Q_INT(1)<=D1 after 27ns;

Q_INT(2)<=D2 after 27ns;

Q_INT(3)<=D3 after 27ns;

Q_INT(4)<=D4 after 27ns;

Q_INT(5)<=D5 after 27ns;

Q_INT(6)<=D6 after 27ns;

Q_INT(7)<=D7 after 27ns;

end if;

end process;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.