Рис 32. Поведенческая VHDL-модель узла.

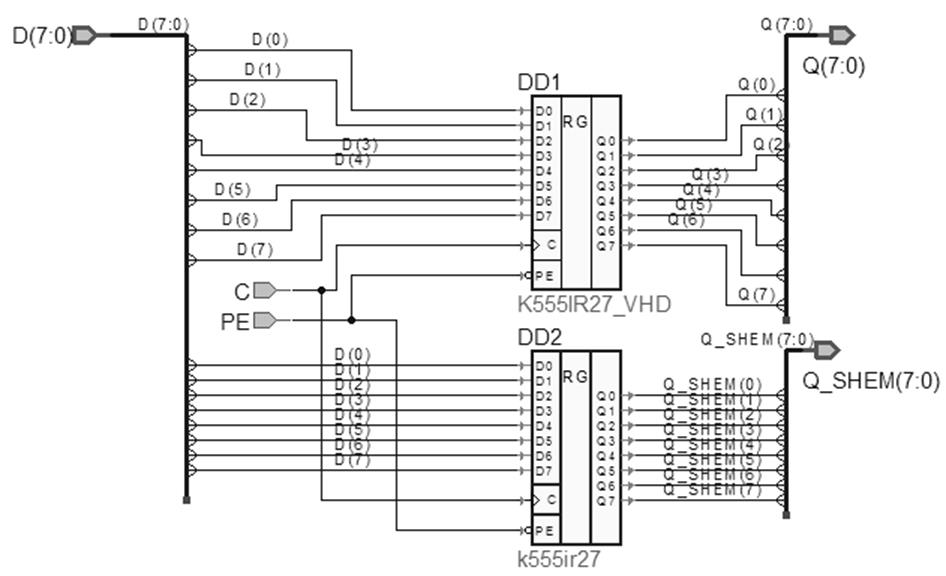

Рис 33. Схема верификации иерархического блока, поддерживаемого схемой замещения и поведенческой VHDL-моделью узла.

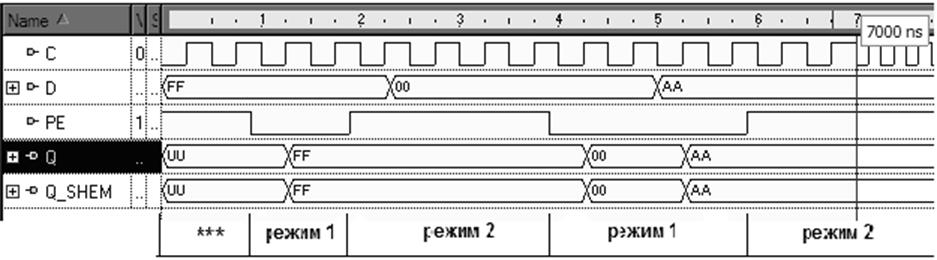

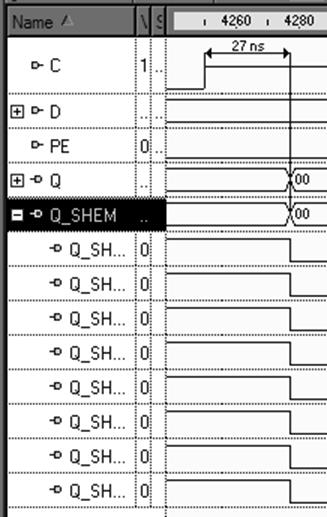

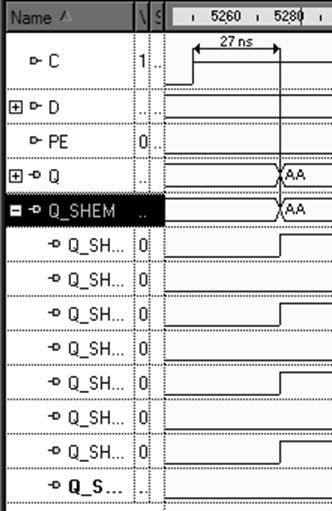

Рис 34. Временные диаграммы моделирования узла

Режим 1 – запись (вход PE устанавливается в L состояние)

Режим 2 – хранение (вход PE устанавливается в H состояние)

C – Синхронный тактовый вход.

PE – Вход разрешения.

D(7..0) – Вход информационный.

Q_SHEM(7..0) – Выход информационный (схема замещения).

Q(7..0) – Выход информационный (VHDL модель).

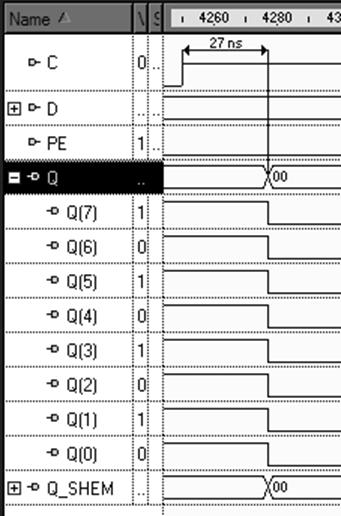

Рис 35. Время задержки распространения сигнала при включении (tPHL) от входа С к выходу Q_SHEM7… Q_SHEM0.

Рис 36. Время задержки распространения сигнала при выключении tPLH от входа С к выходу Q_SHEM7… Q_SHEM0.

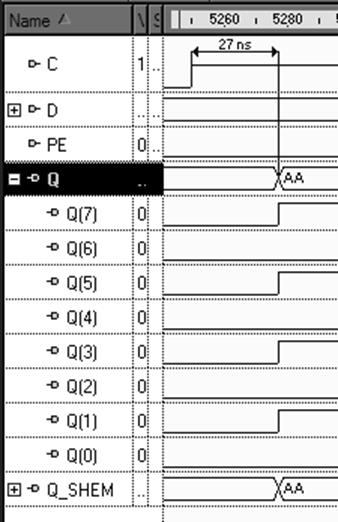

Рис 37. Время задержки распространения сигнала при включении (tPHL) от входа С к выходу Q7… Q0.

Рис 38. Время задержки распространения сигнала при выключении tPLH от входа С к выходу Q 7… Q0.

Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитирования.

В ходе выполнения данной курсовой работы было выполнено индивидуальное задание по разработке цифрового узла ИР27 (Восьмиразрядный регистр с параллельным входом), созданию его структурных и поведенческих моделей (на языке VHDL в пакетах DesignLab 8, OrCAD 9.1 и ActiveHDL 6.2). Были проведены имитационные эксперименты с разработанным узлом, целью которых являлось подтверждение работоспособности узла и соответствие его временных задержек требуемым. Не пройденный на лабораторных работах в прошлом семестре пакет ActiveHDL 6.2, в этом семестре мне представилась возможность изучить его, что я и сделал и получил большое удовольствие моделирования в совершенном пакете ActiveHDL 6.2.

Проведение имитационных экспериментов, про которые говорилось выше, сопутствовалось использованием одинаковых диаграмм входных сигналов. Данный метод обеспечивает наглядность идентичности всех задержек, вне зависимости от того строился ли элемент на основе схемы замещения или в виде макромодели(VHDL-модели), также в некоторых пакетах я использовал зарубежный аналог регистра ИР27 это 74LS377, для сравнения правильности работы моих изобретения и сравнения задержек.

Курсовая работа выполнялась в течении полутора месяцев, так как приходилось выполнять моделирование в выходные или в короткие промежутки времени на работе. При выполнении использовалось руководство к курсовой работе, и уроки по каждому пакету в отдельности, хотелось бы отметить, что это самые наглядные методические указания которые я встречал за все время учебы, спасибо за это Шалагинову А.В..

Перейдём к краткой характеристики и сравнительному анализу использованных пакетов моделирования.

Пакет DesignLab представляет собой САПР, разделённую на несколько рабочих модулей (Schematics, Probe, Stimulus Editor), это удобно, можно выполнять работу с отдельным модулем или с совместным использованием модулей.

Пакет OrCAD – это OrCAD Capture, который включает менеджер проекта, выполняющий роль управляющей оболочки, и OrCAD Simulate.

Пакет ActiveHDL представляет собой единое пространство проектирование, включающее менеджер проекта, редактор внешних воздействий, редактор библиотек и другое. Единство рабочего пространства значительно облегчает работу с проектом в этом пакете. Для удобства использования каждый файл, с которым ведётся работа, может быть выведен в отдельное окно, а затем с лёгкостью свёрнут в главное окно пакета.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.