+ +0s 1

+ 1.83us 0

+ 3.36us 1

+ 5.194us 0

+ 7.4us 1

.STIMULUS D STIM (8, 11111111) ;! Hex

+ +0s 11111111

+ 3.87us 00000000

+ 6.37us 10101010

.STIMULUS DSTM6 STIM (8, 11111111) ;! Hex

+ +0s 11111111

.STIMULUS R STIM (1, 1)

+ +0s 1

Рис 6. Файл SHEM.stl

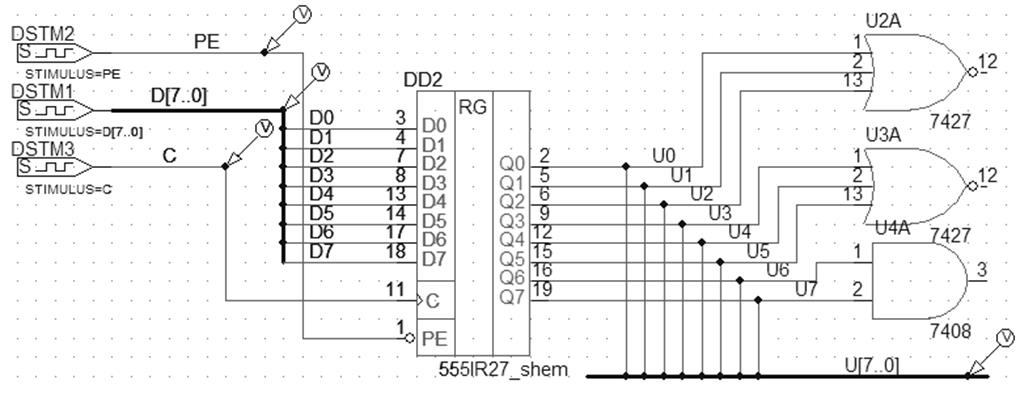

Рис 7. Схема верификации иерархического символа

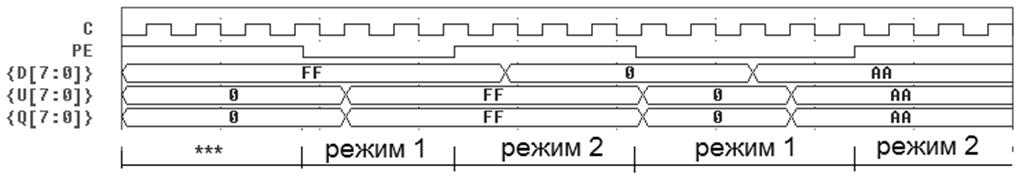

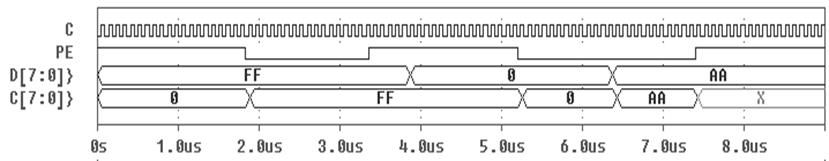

Рис 8. Временные диаграммы моделирования узла

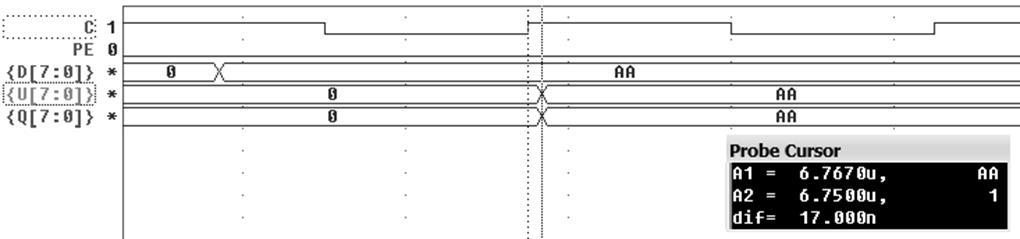

На приведённых ниже временных диаграммах показаны все случаи задержек распространения сигналов.

Режим 1 – запись (вход PE устанавливается в L состояние)

Режим 2 – хранение (вход PE устанавливается в H состояние)

C – Синхронный тактовый вход.

PE – Вход разрешения.

D(7..0) – Вход информационный.

U(7..0) – Выход информационный (схема замещения).

Q(7..0) – Выход информационный (зарубежный аналог 74LS377).

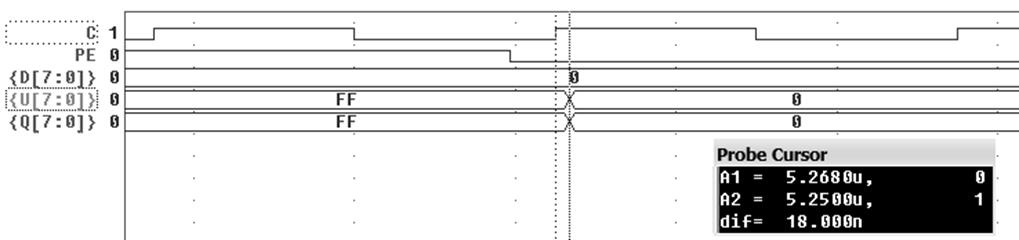

Рис 9. Время задержки распространения сигнала при включении (tPHL) от входа С к выходу U7…U0.

Рис 10. Время задержки распространения сигнала при выключении tPLH от входа С к выходу U7…U0.

Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитирования.

Заранее ясно, что частота не может быть выше заложенной в модель задержек. Предельная частота изменения сигналов на входах узла– величина, обратная максимальной задержке распространения сигнала от входа до выхода.

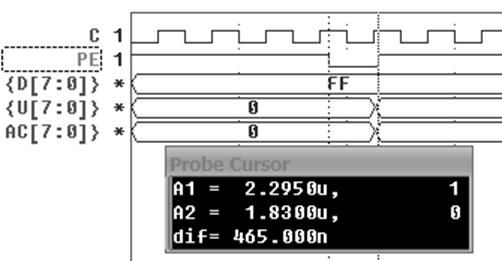

На рис. 11 приведен пример, того, как время удержания сигнала PE = 0 мало для того, чтобы схема успела среагировать и регистр «включился» на работу. Данное время не должно быть менее чем время 460ns, в примере данное время равно 465ns.

Рис.11. Граница нарушения временных соотношений.

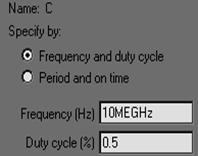

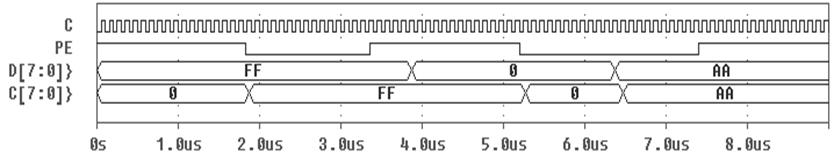

Надо попытаться захватывать постоянные данные с одной шины, при этом увеличивать частоту синхросигнала пока модель «не сломается».

На рис.12 работоспособный узел с максимальной частотой.

Рис 12.Узел работает без ошибок на частоте 10 МГц.

Рис 13.Узел не корректно работает на частоте 11 МГц.

Частота, на которой узел стал не корректно работать, равна 11МГц.

Таким образом, увеличив частоту на 1МГц разработанный узел перестает работать.

|

*--------- * 555IR27 Octal D-TYPE Flip-Flops with Clock Enable * * The TTL Data Book, Vol 2, 1985, TI * atl 8/7/89 Update interface and model names * .subckt 555IR27 NPE C D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 + optional: DPWR=$G_DPWR DGND=$G_DGND + params: MNTYMXDLY=0 IO_LEVEL=0 UBUF bufa(2) DPWR DGND + NPE C GBBUF CLKBUF + D0_GATE IO_LS IO_LEVEL={IO_LEVEL} X1Q GBBUF CLKBUF D0 Q0 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X2Q GBBUF CLKBUF D1 Q1 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X3Q GBBUF CLKBUF D2 Q2 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X4Q GBBUF CLKBUF D3 Q3 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X5Q GBBUF CLKBUF D4 Q4 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X6Q GBBUF CLKBUF D5 Q5 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X7Q GBBUF CLKBUF D6 Q6 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} X8Q GBBUF CLKBUF D7 Q7 DPWR DGND LS377DAT + params: MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} .ends * .subckt LS377DAT GB C D Q DPWR DGND + params: MNTYMXDLY=0 IO_LEVEL=0 UBUF buf DPWR DGND + D DBUF + D0_GATE IO_LS IO_LEVEL={IO_LEVEL} USET inv DPWR DGND + GB G2 + D_IR27_1 IO_LS MNTYMXDLY={MNTYMXDLY} UNXOR nxor DPWR DGND + GB G2 EN + D0_GATE IO_LS UIN buf3 DPWR DGND + $D_X EN IN + D0_TGATE IO_LS UD1 buf DPWR DGND + DBUF DX + D0_GATE IO_LS UD2 buf DPWR DGND + DBUF DX + D_IR27_2 IO_LS MNTYMXDLY={MNTYMXDLY} UINV inv DPWR DGND + GB G + D0_GATE IO_LS UAO ao(2,2) DPWR DGND + G DX GB QBUF IN + D0_GATE IO_LS IO_LEVEL={IO_LEVEL} UDFF dff(1) DPWR DGND + $D_HI $D_HI C IN QBUF $D_NC + D_IR27_3 IO_LS MNTYMXDLY={MNTYMXDLY} UQOUT buf DPWR DGND + QBUF Q + D_IR27_4 IO_LS MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL} .ends * .model D_IR27_1 ugate ( + tphlmn=15ns + ) .model D_IR27_2 ugate ( + tplhmn=10ns tphlmn=10ns + ) .model D_IR27_3 ueff ( + twclklmn=20ns twclkhmn=20ns + tsudclkmn=10ns thdclkmn=5ns + ) .model D_IR27_4 ugate ( + tplhty=17ns tplhmx=27ns + tphlty=18ns tphlmx=27ns + ) *$ *--------- |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.