Содержание:

1. Постановка задачи. 3

2. Условное графическое обозначение моделируемого узла. 3

3. Таблица назначения выводов узла. 3

4. Логическая таблица режимов работы узла. 4

5. Таблица реальных задержек работы узла. 4

6. Описание работы узла. 5

7. Моделирование узла в пакете OrCAD 9.1. 6

7.1. Условное графическое обозначение проектируемого узла в виде иерархического символа. 6

7.2. SPICE – проект. Схема замещения проектируемого узла. 6

7.3. Схема верификации иерархического символа. 11

7.4. Результаты моделирования узла. 11

7.5. Оценка предельных скоростных возможностей узла. 14

7.6. PCB Simulate – проект. Схема замещения проектируемого узла. 15

7.7. Схема верификации и результаты моделирования узла. 19

7.8. Поведенческая VHDL-модель узла. 23

7.9. Схема верификации узла с подключенной VHDL-моделью. 24

7.10. Результаты моделирования VHDL-модели узла. 24

8. Моделирование узла в пакете Active-HDL 8.1. 28

8.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 28

8.2. Принципиальная схема замещения узла. 28

8.4. Результаты моделирования иерархического блока со схемой замещения. 32

8.5. Поведенческая VHDL-модель узла. 36

8.6. Схема верификации узла с подключенной VHDL-моделью. 36

8.7. Результаты моделирования VHDL-модели узла. 36

9. Выводы. 40

9.1. Общие выводы. 40

9.2. Сравнительный анализ пакетов. 40

9.3. Личные впечатления. 41

10. Список использованной литературы. 42

Приложение 1. Функциональные модели проекта PSPICE. 43

Приложение 2. VHDL-модели отечественных элементов. 46

Создать структурные и поведенческие модели исследуемого цифрового узла в пакетах OrCAD 9.1, Active-HDL 8.1. Провести имитационные эксперименты с разработанным узлом, подтвердить его работоспособность и соответствие временных задержек требуемым. Исследовать возможности используемых инструментальных средств проектирования.

В качестве исследуемого цифрового узла взят элемент К555ИМ3 (полный двоичный четырехразрядный сумматор).

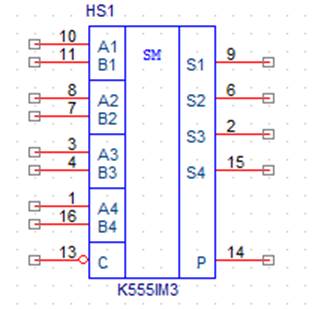

Ниже представлены условные графические обозначения моделируемого узла в пакетах OrCAD 9.1 (рис. 1 слева) и Active-HDL 8.1 (рис. 1 справа). Цоколевка микросхемы К555ИМ3 взята из справочника «Цифровые устройства на интегральных микросхемах» Бирюков С.А.

Рис. 1. Условное графическое обозначение узла, выполненное в пакетах OrCAD 9.1(слева) и ActiveHDL8.1(справа).

Таблица 1. Назначение выводов узла.

|

Номер вывода |

Обозначение |

Назначение |

|

01 |

A4 |

Вход данных (четвертый разряд первого слова) |

|

02 |

S3 |

Выход суммы (третий разряд) |

|

03 |

A3 |

Вход данных (третий разряд первого слова) |

|

04 |

B3 |

Вход данных (третий разряд второго слова) |

|

06 |

S2 |

Выход суммы (второй разряд) |

|

07 |

B2 |

Вход данных (второй разряд второго слова) |

|

08 |

A2 |

Вход данных (второй разряд первого слова) |

|

09 |

S1 |

Выход суммы (первый разряд) |

|

10 |

A1 |

Вход данных (первый разряд первого слова) |

|

11 |

B1 |

Вход данных (первый разряд второго слова) |

|

13 |

С |

Вход переноса |

|

14 |

P |

Выход переноса |

|

15 |

S4 |

Выход суммы (четвертый разряд) |

|

16 |

B4 |

Вход данных (четвертый разряд второго слова) |

Таблица 2. Логическая таблица режимов работы узла.

|

Входы |

Выходы |

Примечание |

|||

|

С(n-1) |

An |

Bn |

Sn |

Cn |

|

|

L |

L |

L |

L |

L |

суммирование без переносов (входного и выходного) |

|

L |

L |

H |

H |

L |

|

|

L |

H |

L |

H |

L |

|

|

L |

H |

H |

L |

H |

суммирование с формированием выходного переноса |

|

H |

L |

L |

H |

L |

входной перенос увеличивает результат на единицу |

|

H |

L |

H |

L |

H |

входной перенос увеличивает результат на единицу, что вызывает переполнение и формирует выходной перенос |

|

H |

H |

L |

L |

H |

|

|

H |

H |

H |

H |

H |

переполнение при суммирование уже сформировало выходной перенос, входной перенос лишь увеличивает значение суммы на единицу |

|

L – низкий уровень; H – высокий уровень; S – выход суммы; C0 – входной перенос (на цоколевке обозначен как С); С1-С3 – внутренний перенос; С4 - выходной перенос (на цоколевке обозначен как P). |

Примечание: в логической таблице режимов работы узла, для ее более удобного восприятия, выход P (выходной перенос)обозначен как С4.

Таблица 3. Реальные задержки распространения.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.