USE ieee.std_logic_unsigned.all;

USE ieee.std_logic_arith.all;

USE ieee.std_logic_1164.all;

ENTITY K555IM3M IS PORT( --входы и выходы;

A1 : IN std_logic;

A2 : IN std_logic;

A3 : IN std_logic;

A4 : IN std_logic;

B1 : IN std_logic;

B2 : IN std_logic;

B3 : IN std_logic;

B4 : IN std_logic;

C : IN std_logic;

S1 : OUT std_logic;

S2 : OUT std_logic;

S3 : OUT std_logic;

S4 : OUT std_logic;

P : OUT std_logic

);END K555IM3M;

ARCHITECTURE model OF K555IM3M IS -- архитектура узла;

BEGIN -- начало описания архитектуры;

PROCESS(A1,A2,A3,A4,B1,B2,B3,B4,C) -- процесс, который обрабатывается при

--изменении сигнала на входе;

variable A: std_logic_vector(3 downto 0); --вектор, для объединения данных А;

variable B: std_logic_vector(3 downto 0); --вектор, для объединения данных B;

variable Y: std_logic_vector(4 downto 0); --вектор, для результата суммирования;

BEGIN

A := (A4,A3,A2,A1); --присвоение

B := (B4,B3,B2,B1); --входных значений;

Y := ('0'&A)+('0'&B)+("0000"&C); --вычисление суммы;

S1 <=Y(0) AFTER 24NS; --передача

S2 <=Y(1) AFTER 24NS; --результата

S3 <=Y(2) AFTER 24NS; --на выходы

S4 <=Y(3) AFTER 24NS; --с соответствующими

P <=Y(4) AFTER 17NS; --задержками;

END PROCESS; -- окончание описания процесса;

END model; -- окончания описания архитектуры.

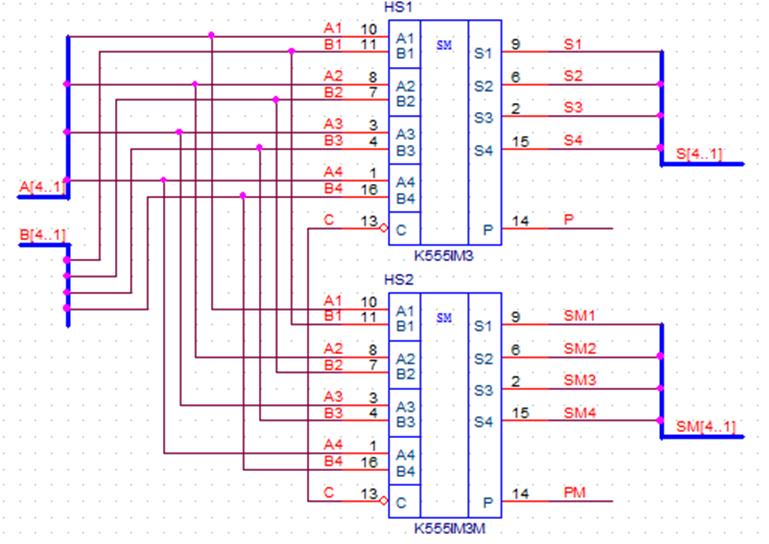

Рис. 21. Схема верификации узла с подключенной VHDL-моделью (HS2) и элемента со схемой замещения (HS1).

7.10. Результаты

моделирования VHDL-модели узла.

7.10. Результаты

моделирования VHDL-модели узла.

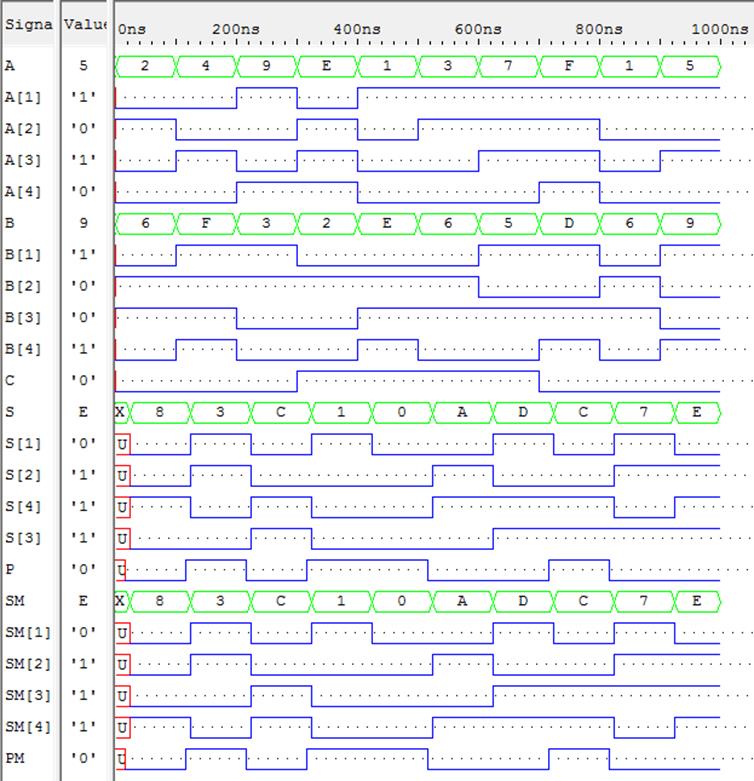

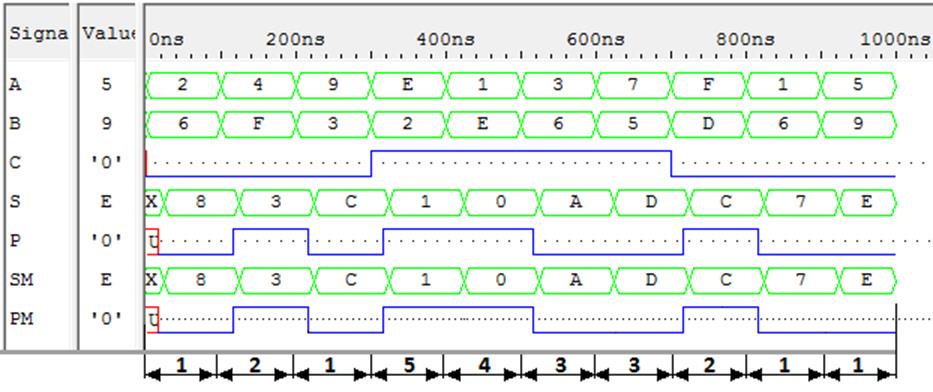

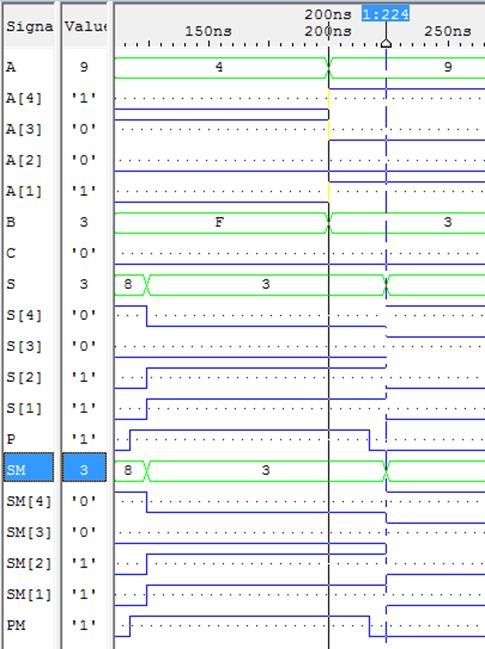

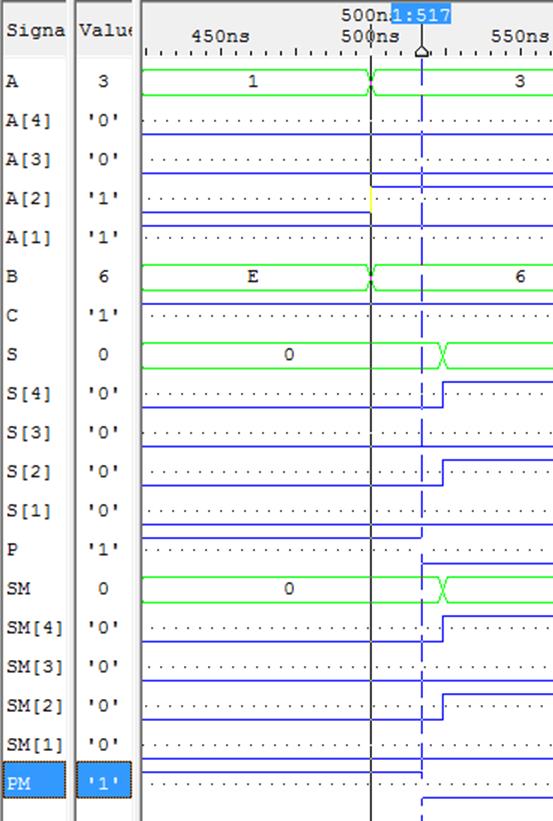

Рис. 22. Временные диаграммы моделирования VHDL-модели узла (HS2) и элемента со схемой замещения (HS1).

Для наглядного представления временных диаграмм и их анализа, оставим только шинные сигналы и сигналы С, Р и PM (рис. 23).

Рис. 23. Временные диаграммы моделирования VHDL-модели узла (HS2) и элемента со схемой замещения (HS1).

Пояснения к временным диаграммам моделирования узла:

режим №1 – суммирование без переносов (входного и выходного);

режим №2 – суммирование с формированием выходного переноса P(PM);

режим №3 – входной перенос C увеличивает результат на единицу;

режим №4 – входной перенос увеличивает результат на единицу, что вызывает переполнение и

формирует выходной перенос;

режим №5 – переполнение при суммирование уже сформировало выходной перенос, входной

перенос лишь увеличивает значение суммы на единицу.

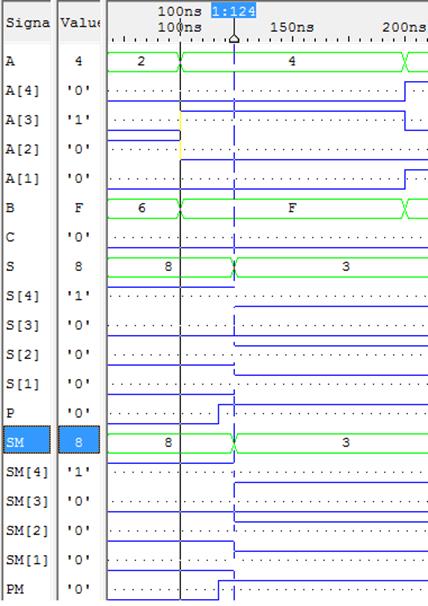

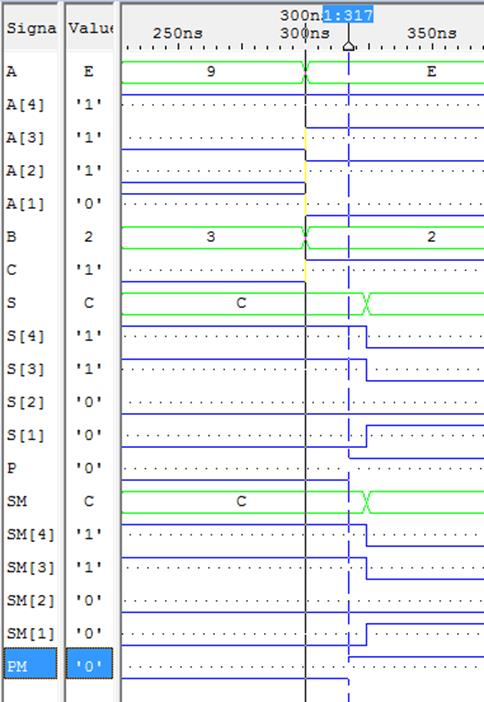

Исходя из результатов эксперимента, VHDL-модель работает корректно. Перейдем к контролю временных соотношений в VHDL-модели (рис. 24-27).

Рис. 24. Время задержки распространения сигнала при включении:

Входы А,В – выход S (SM) - 24нс.

Рис. 25. Время задержки распространения сигнала при выключении:

Входы А,В – выход S (SM) - 24нс.

|

Рис. 26. Время задержки распространения сигнала при включении:

Вход C – выход P(PM) - 17нс.

Рис. 27. Время задержки распространения сигнала при выключении:

Вход C – выход P(PM) - 17нс.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.