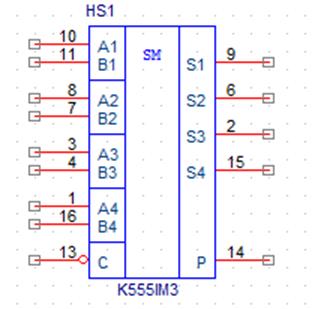

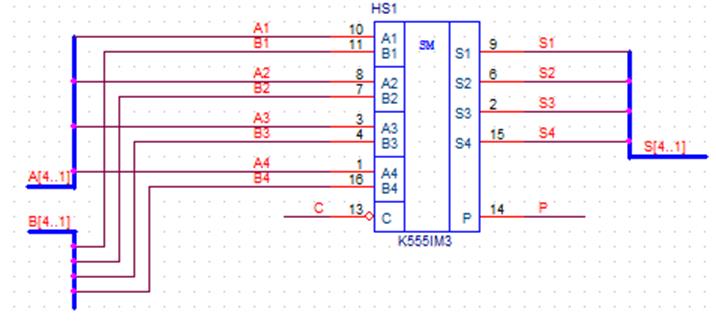

Рис. 5. Схема верификации иерархического символа (HS1) и зарубежного аналога(U1).

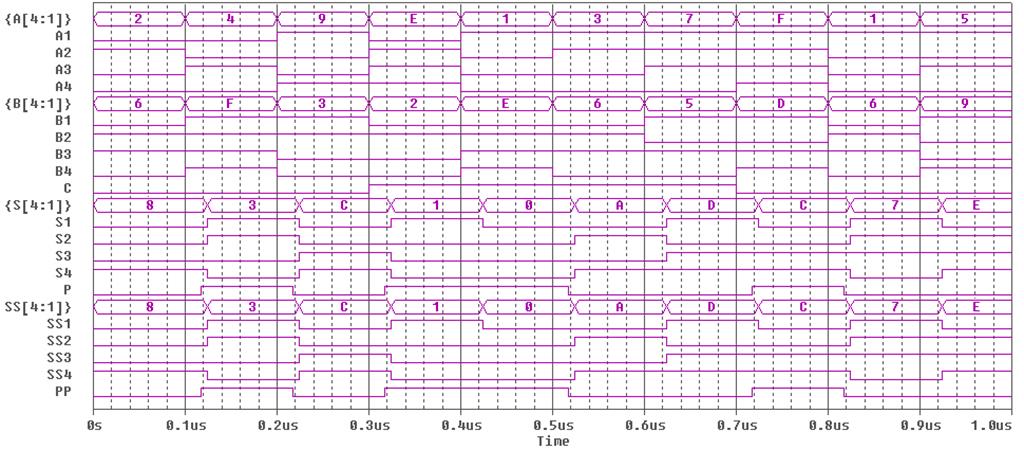

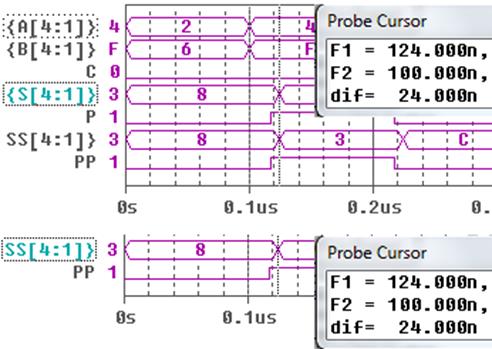

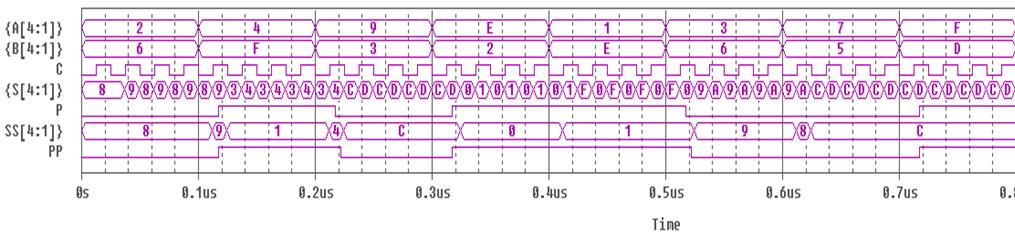

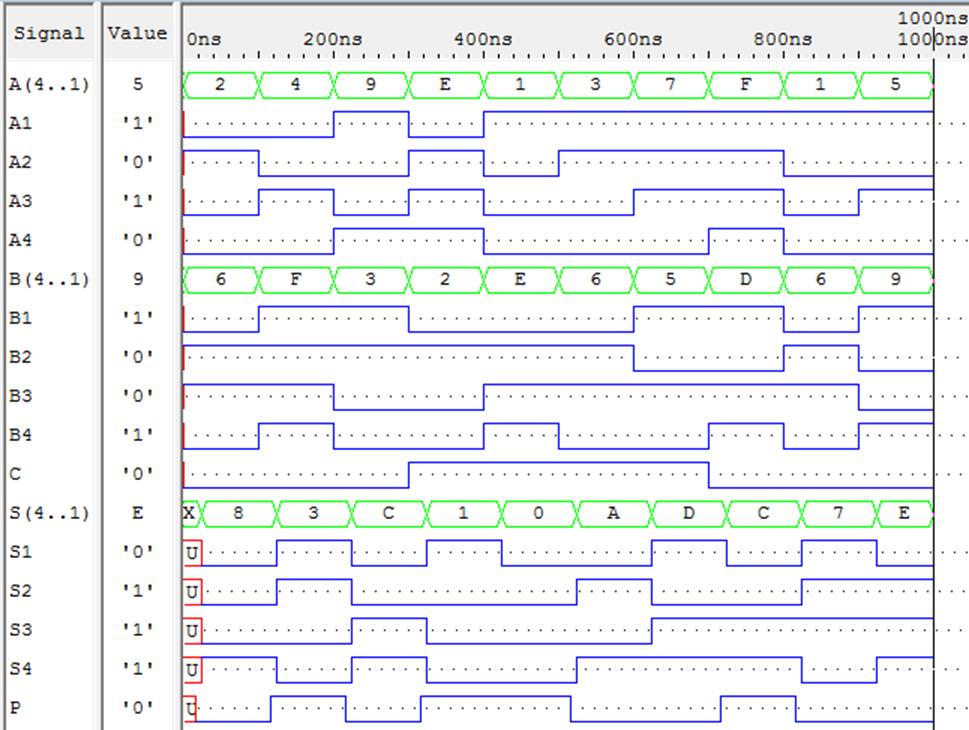

Рис. 6. Временные диаграммы моделирования иерархического символа (HS1) и его зарубежного аналога(U1).

A[4..1] – первое входное слово (первое слагаемое);

B[4..1] – второе входное слово (второе слагаемое);

С – входной перенос;

S[4..1] – выходное слово (сумма) элемента K555IM3;

P – выходной перенос элемента K555IM3;

SS[4..1] – выходное слово (сумма) элемента 74LS83A;

PP – выходной перенос элемента 74LS83A.

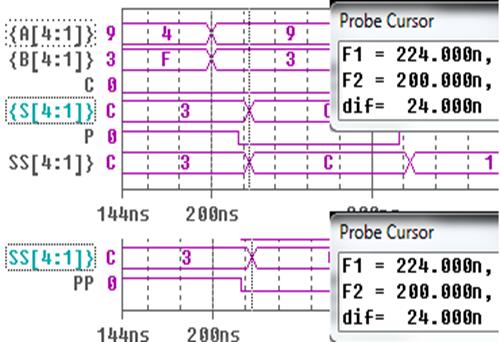

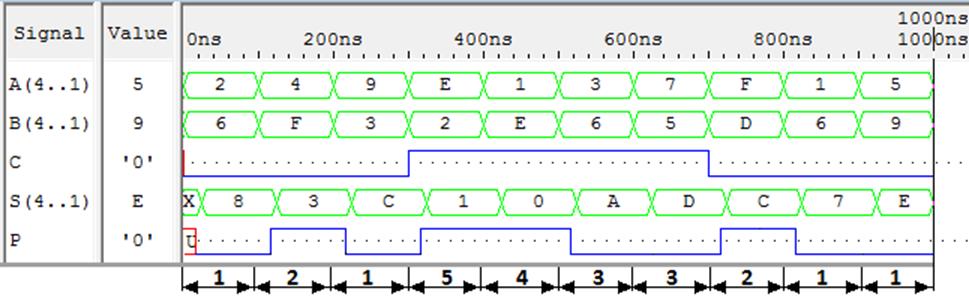

Для наглядного представления временных диаграмм и их анализа, оставим только шинные сигналы и сигналы С, Р и PP (рис. 7).

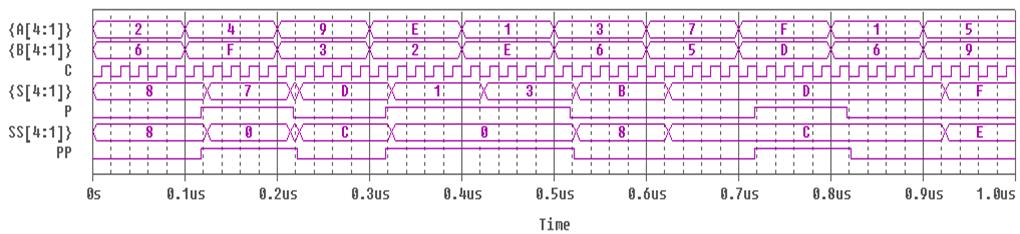

Рис. 7. Временные диаграммы моделирования иерархического символа (HS1) и его зарубежного аналога(U1).

Пояснения к временным диаграммам моделирования узла:

режим №1 – суммирование без переносов (входного и выходного);

режим №2 – суммирование с формированием выходного переноса P(PP);

режим №3 – входной перенос C увеличивает результат на единицу;

режим №4 – входной перенос увеличивает результат на единицу, что вызывает переполнение и

формирует выходной перенос;

режим №5 – переполнение при суммирование уже сформировало выходной перенос, входной

перенос лишь увеличивает значение суммы на единицу.

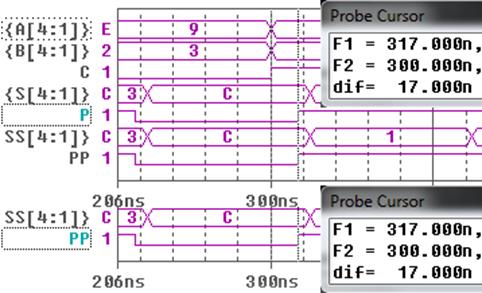

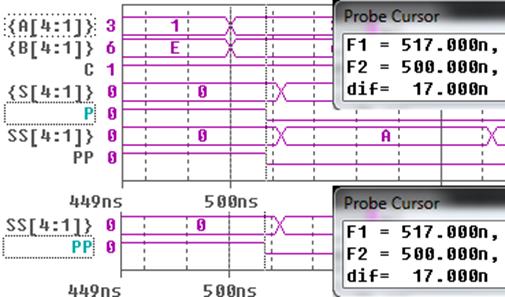

Исследовав работу проектируемого узла ИМ3, и убедившись в правильности работы схемы замещения, можно сделать вывод, что данный элемент успешно выполняет нужные функции. После прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения (рис. 8,9).

Рис. 8. Время задержки распространения сигнала при включении/выключении:

Входы А,В – выход S (SS) - 24нс.

Рис. 9. Время задержки распространения сигнала при включении/выключении:

Вход C – выход P (PP) - 17нс.

Все задержки, отображенные на временных диаграммах, совпадают с табличными, что является подтверждением правильности их имитации.

Предельная частота изменения сигналов на входах узла – величина, обратная максимальной задержке распространения сигнала от входа до выхода.

fmax = 1 / 24нс = 41,67 МГц

Временные диаграммы работы узла при изменении сигнала на входе C представлены ниже (рис. 10-11).

Рис. 10. Работа проектируемого узла при тактовой частоте 40МГц на входе С.

Рис. 11. Работа проектируемого узла при тактовой частоте 50МГц на входе С.

Сделаем вывод о работоспособности ИМ3 при заданных условиях. При уменьшении частоты до 40МГц или при ее увеличении до 50МГц начинаются многочисленные сбои и ошибки, расхождения в работе при сравнении с зарубежным аналогом, предложенным библиотекой 74ls.

Условное графическое обозначение проектируемого символа (рис. 12):

Рис. 12. Условное графическое изображение узла в виде иерархического символа..

Схема замещения выполнена на спроектированных «с нуля» элементах, в которые заложены задержки, комбинация которых приводит к корректной имитации реального узла ИМ3. VHDL-модели данных элементов представлены в приложении 2.

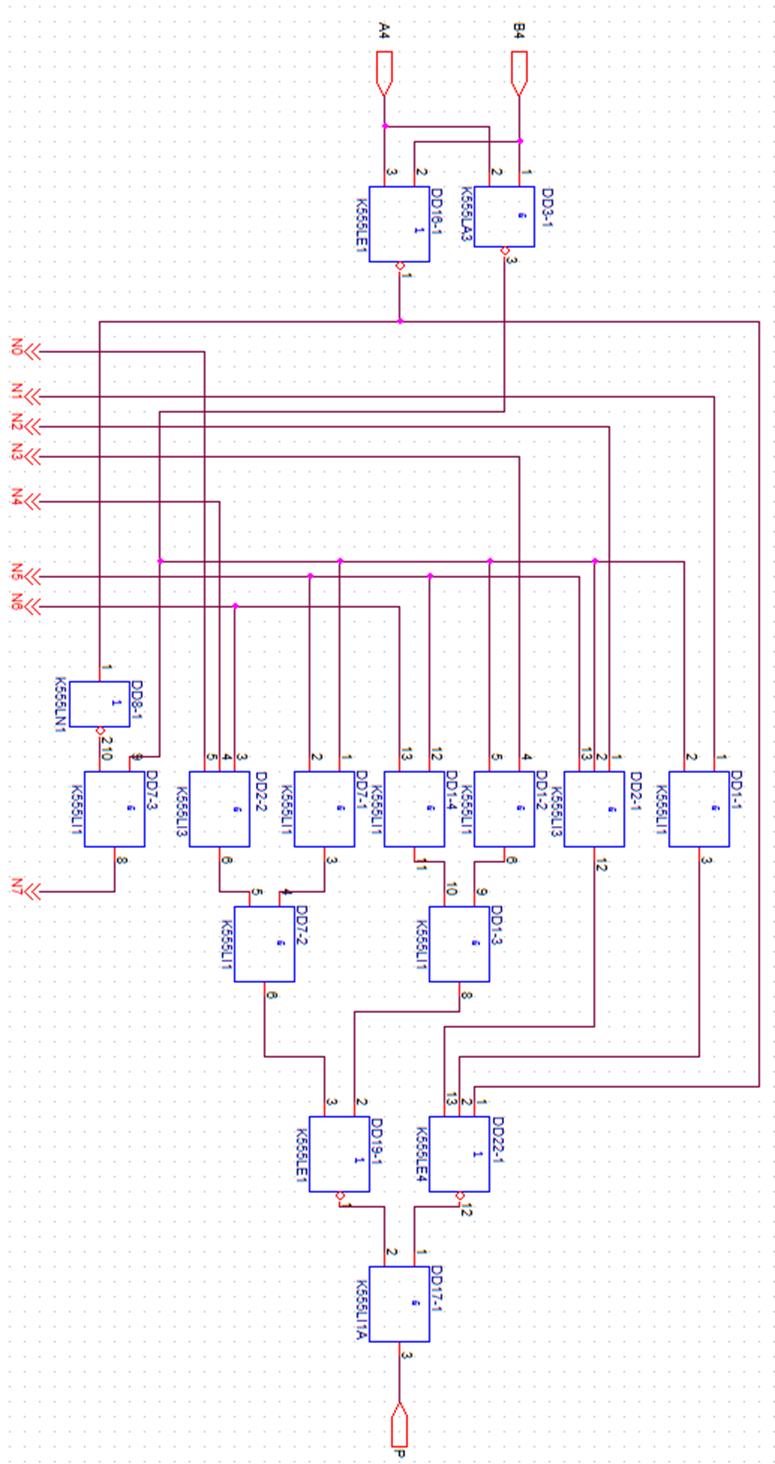

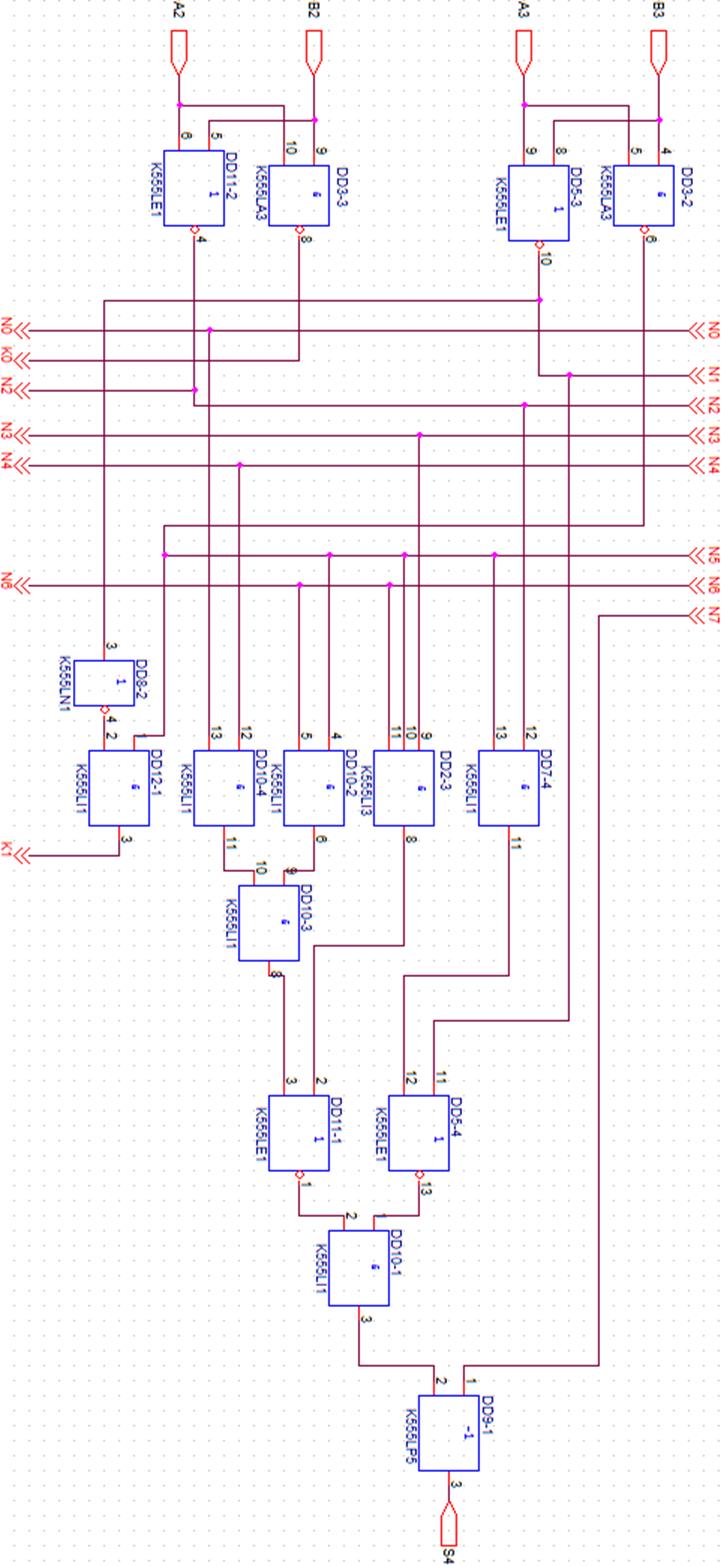

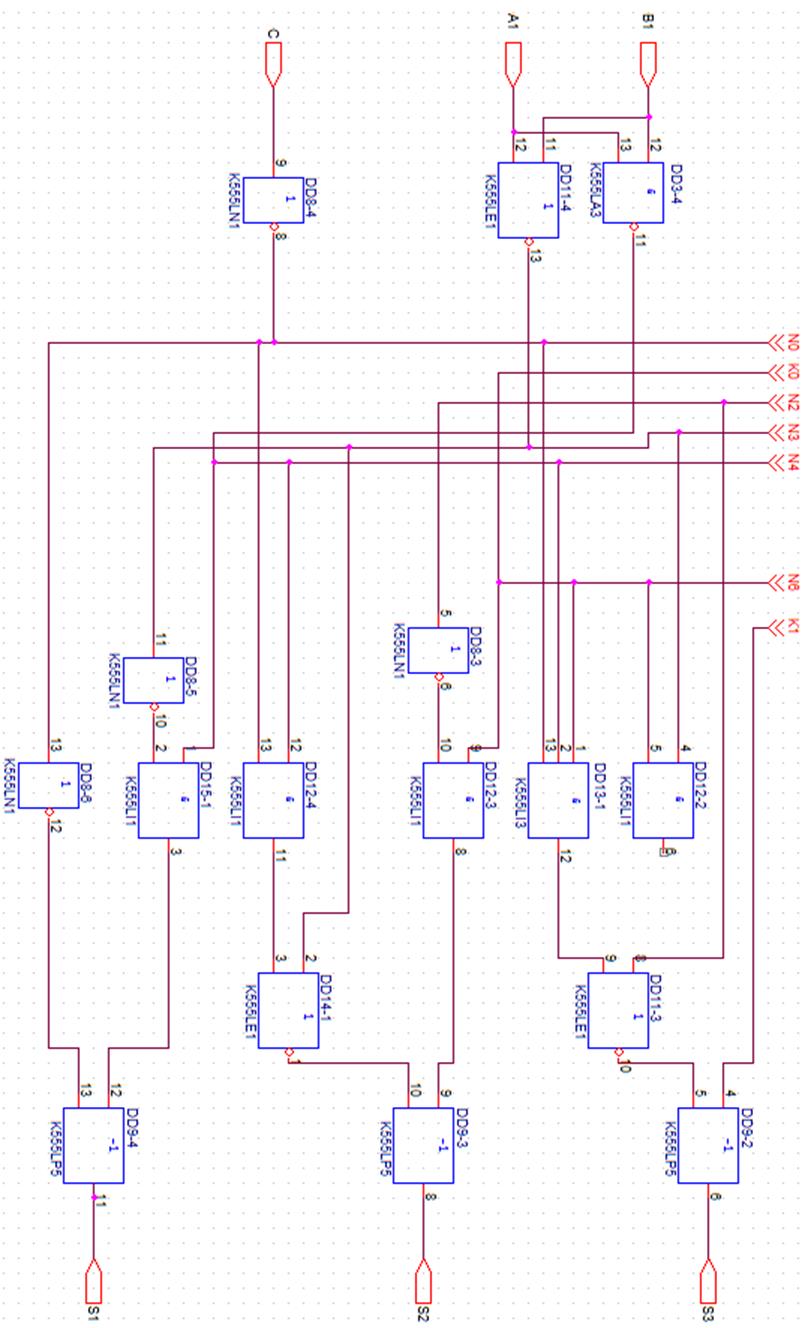

Для лучшего восприятия, принципиальная схема замещения была разбита на три страницы, которые представлены далее (стр. 16-18; рис. 13.1-13.3).

Схема верификации иерархического символа (рис. 14):

Рис. 14. Схема верификации иерархического символа, созданного в PCB Simulate – проекте.

Результаты моделирования узла:

|

Рис. 15. Временные диаграммы моделируемого узла.

Для наглядного представления временных диаграмм и их анализа, оставим только шинные сигналы и сигналы С, Р (рис. 16).

|

Рис. 16. Временные диаграммы моделируемого узла.

Пояснения к временным диаграммам моделирования узла:

режим №1 – суммирование без переносов (входного и выходного);

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.