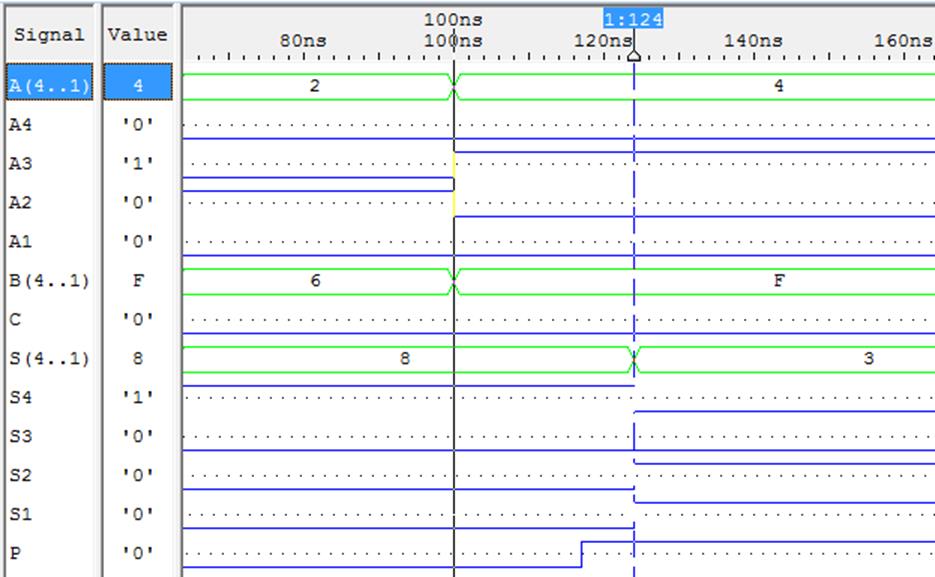

режим №2 – суммирование с формированием выходного переноса P;

режим №3 – входной перенос C увеличивает результат на единицу;

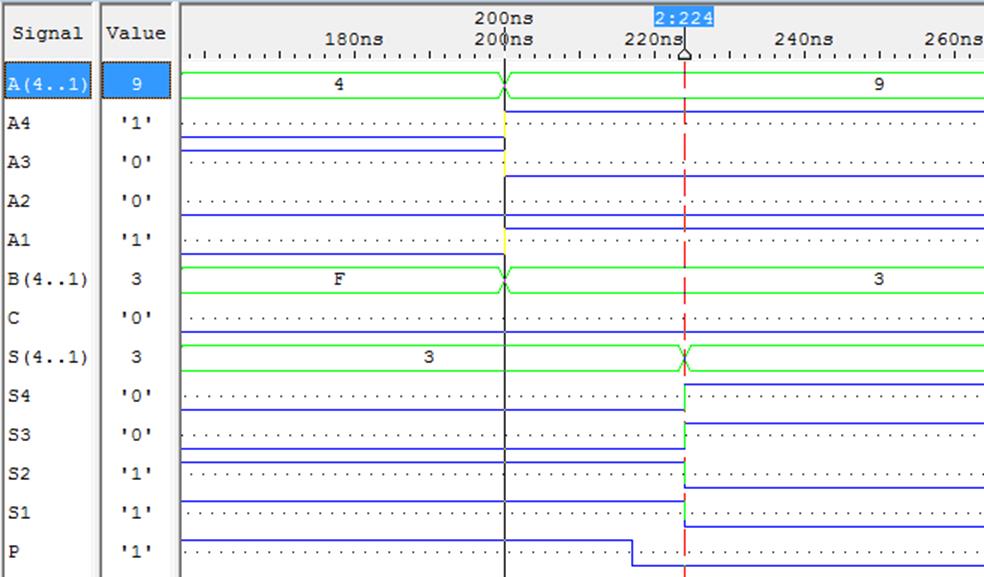

режим №4 – входной перенос увеличивает результат на единицу, что вызывает переполнение и

формирует выходной перенос;

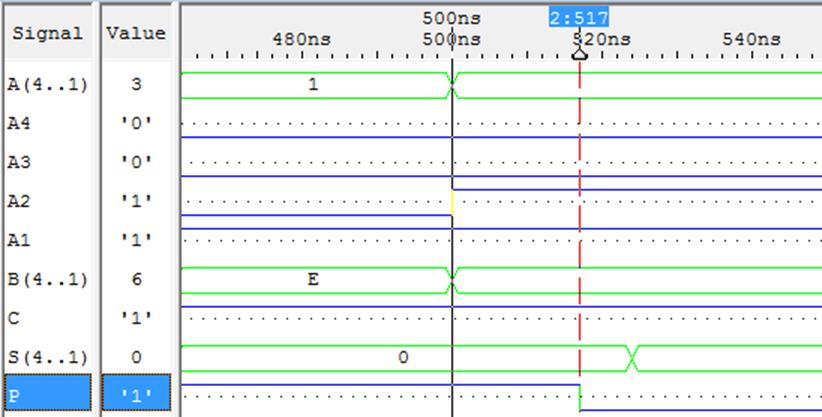

режим №5 – переполнение при суммирование уже сформировало выходной перенос, входной

перенос лишь увеличивает значение суммы на единицу.

Исследовав работу проектируемого узла ИМ3, и убедившись в правильности работы схемы замещения, можно сделать вывод, что данный элемент успешно выполняет нужные функции. После прохождения этапа проверки работы проектируемого узла мы переходим к проверке соответствия временных соотношений в схеме замещения (рис. 17-20).

Рис. 17. Время задержки распространения сигнала при включении:

Входы А,В – выход S - 24нс.

Рис. 18. Время задержки распространения сигнала при выключении:

Входы А,В – выход S - 24нс.

|

Рис. 19. Время задержки распространения сигнала при включении:

Вход C – выход P - 17нс.

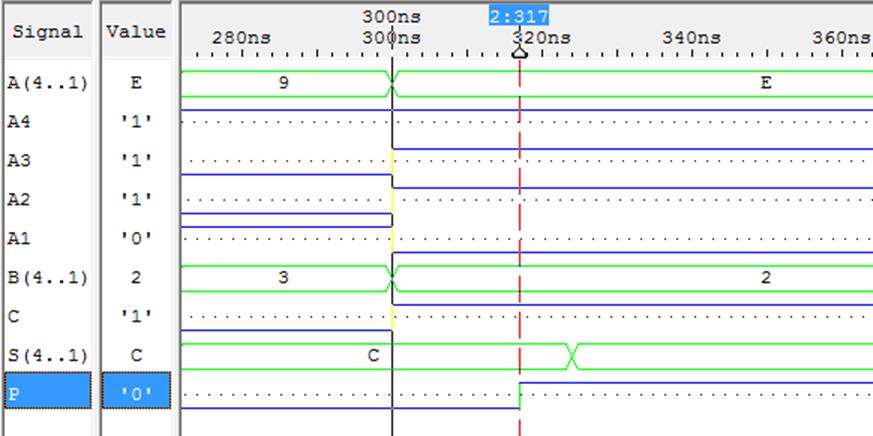

Рис. 20. Время задержки распространения сигнала при выключении:

Вход C – выход P - 17нс.

В результате проведенного эксперимента все задержки были имитированы корректно. И в полной мере совпадают с теми, которые представлены в оригинальном datasheet .

Заключение, сравнение PSPICE и PCB Simulate проектов:

По итогам работы в обоих проектах можно сказать, что PCB Simulate проект и Spice-проект показали одинаковые результаты. Задержки также идентичны в обоих проектах, так как задержки изначально заложенные в динамические PSpice-модели вентилей схемы замещения иерархического символа были полностью имитированы в PCB Simulate проекте с помощью средств универсального языка описания цифровой аппаратуры VHDL. Именно это решение привело к однозначной работе узла как в PSpice, так и в PCB Simulate. Эксперимент в обоих случаях был проведен на одних и тех же входных воздействиях. Качество проделанной работы подтверждается тем, что в обоих случаях узел ведет себя абсолютно одинаково.

По процессу проектирования можно сказать, что в обоих проектах приходилось создавать свою библиотеку символов и рисовать графическую оболочку отечественных элементов. В обоих проектах, внешне элементы одинаковы, но их модели реализованы по-разному. В PSpice у каждого элемента есть своя функциональная модель, подкрепленная динамической моделью, в которой описаны задержки, а в PCB Simulate у каждого элемента свой VHDL-код, в котором сразу же описаны задержки, на мой взгляд, VHDL-код реализован проще, чем функциональные модели в PSpice. Собирание схемы замещения в обоих проектах проходит одинаково, но, чтобы начать симуляцию схемы, в PSpice необходимо на входы устанавливать DigiStim, при этом чтобы увидеть сигналы при симуляции, нужно на входы и выходы «повесить» маркеры напряжения. В PCB Simulate этого делать не нужно, при симуляции сразу отображаются все сигналы. Кроме этого, в этих проектах разный механизм задавания «стимулов», в PSpice стимулы приходится задавать методом клика и перетягивания курсора до нужного значения, а в PCB Simulate приходится вписывать все вручную, воспользовавшись специальной формой. Я считаю, метод задания «стимулов» в PSpice удобен, если в схеме мало входных сигналов и нет закономерностей, а метод PCB Simulate удобен если есть сигналы изменяющиеся с определенной закономерностью, для этих целей в PCB Simulate предусмотрена такая вкладка как Advanced. Процесс измерения задержек в обоих проектах практически одинаков, но что примечательно, что в PSpice при измерении задержек появляется специальное окошко, в котором указаны начало, конец отрезка измерения и сама задержка, я считаю, что это более информативно, нежели в проекте PCB Simulate. Но плюсом в измерении задержек в PCB Simulate является то, что можно установить несколько курсоров, в PSpice этого сделать нельзя.

LIBRARY ieee; -- подключение необходимых библиотек;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.