|

Обозначение |

Параметр |

Значение, нс |

|

tPLH |

Время задержки распространения сигнала при включении: - входы Ai, Bi – выход Si; - входы Ai, Bi - выход переноса P; |

max |

|

24 |

||

|

17 |

||

|

tPHL |

Время задержки распространения сигнала при выключении: - входы Ai, Bi – выход Si; - входы Ai, Bi - выход переноса P; |

|

|

24 |

||

|

17 |

Примечание: информация о параметрах узла взята из технической документации, представленной фирмой Motorola (www.motorola.com).

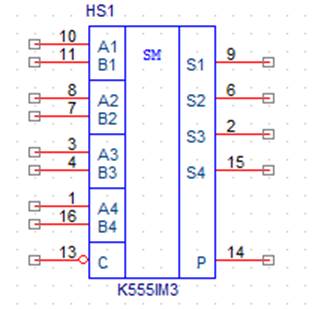

Микросхема ИМ3 представляет собой высокоскоростной четырёхразрядный двоичный полный сумматор с предварительным внутренним переносом. На вход сумматор принимает два 4-разрядных двоичных слова (А1-А4, В1-В4) и входной перенос (С). На выходе генерирует сумму (выходы S1-S4) и перенос (выход P). ИМ3 производит суммирование двух четырёхразрядных двоичных слов и входного переноса, результатом является четырёхразрядное двоичное слово и выходной перенос. При возникновении переполнения операции суммирования выход переноса устанавливается в единичное состояние.

Условное графическое изображение проектируемого узла в виде иерархического символа представлено на рис. 2.

Рис. 2. Условное графическое изображение узла в виде иерархического символа.

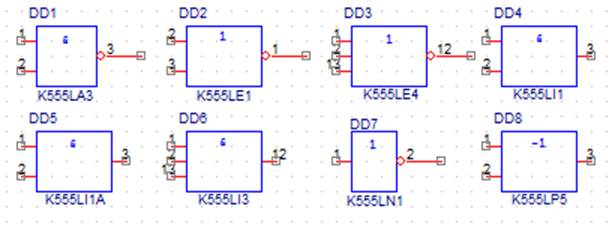

Согласно методическим указаниям к курсовой работе схема замещения проектируемого узла, в данном случае сумматора ИМ3, должна быть выполнена в отечественных графических обозначениях по ЕСКД. Для этого была создана специальная библиотека символов отечественных компонентов k555im3.olb, содержащая модифицированные аналоги из библиотеки 74ls.olb. Список заимствованных элементов представлен в таблице 4.

Таблица 4. Соответствие отечественных элементов зарубежным аналогам и их логические функции.

|

Зарубежный элемент |

Отечественный аналог |

Логическая функция |

|

74ls04 |

К555ЛН1 (K555LN1) |

НЕ |

|

74ls08 |

К555ЛИ1 (K555LI1) |

2И |

|

74ls11 |

К555ЛИ3 (K555LI3) |

3И |

|

74ls00 |

К555ЛА3 (K555LA3) |

2И-НЕ |

|

74ls02 |

К555ЛЕ1 (K555LE1) |

2ИЛИ-НЕ |

|

74ls27 |

К555ЛЕ4 (K555LE4) |

3ИЛИ-НЕ |

|

74ls86 |

К555ЛП5 (K555LP5) |

2XOR |

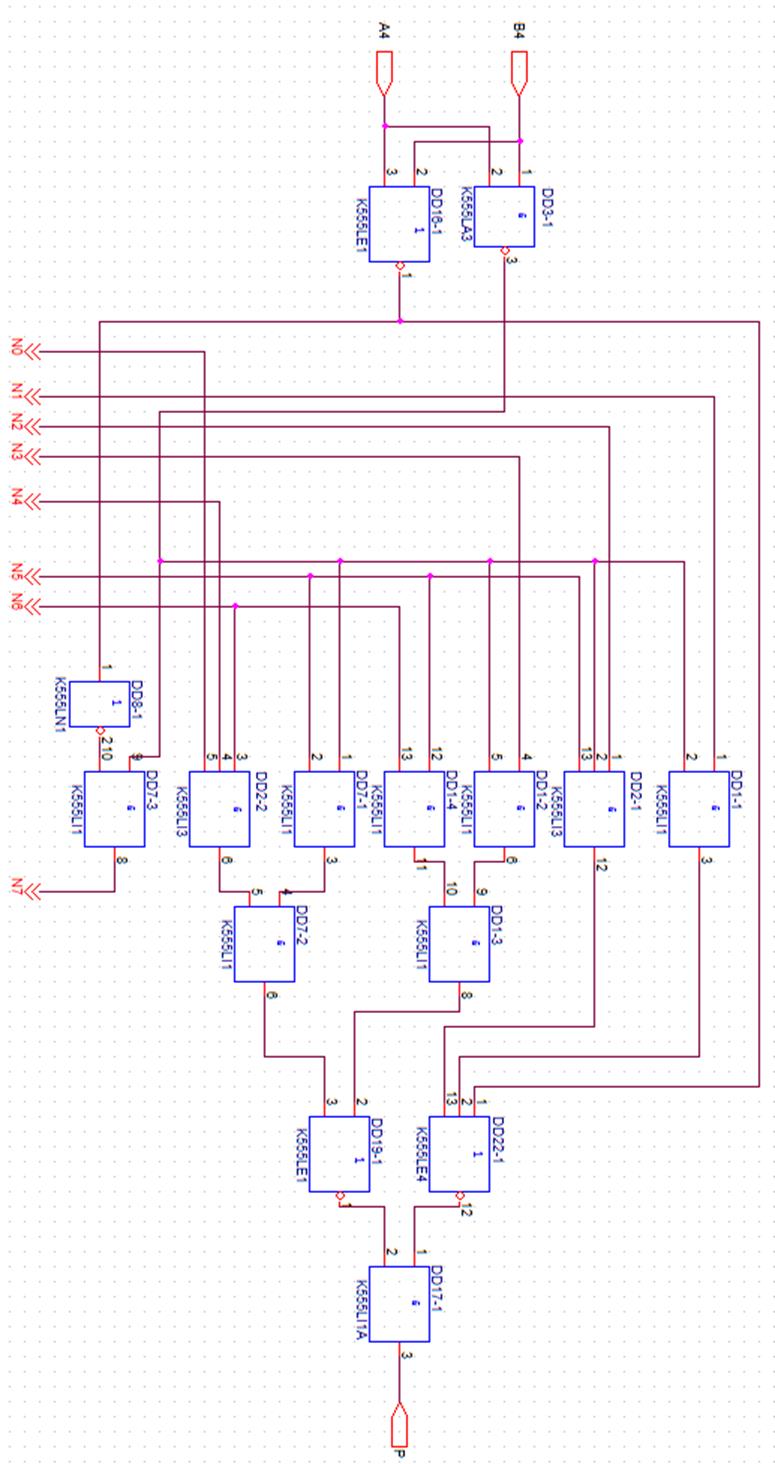

Для схемы замещения потребовались также более сложные элементы: 5ИЛИ-НЕ и 4ИЛИ-НЕ. Было принято решение не создавать для них специальных символов, а заменить комбинацией уже разработанных вентилей. Элемент 5ИЛИ-НЕ заменён тремя уже разработанными вентилями – (2ИЛИ-НЕ + 3ИЛИ-НЕ) + 2И = 5ИЛИ-НЕ, а элемент 4ИЛИ-НЕ: (2ИЛИ-НЕ + 2ИЛИ-НЕ) + 2И = 4ИЛИ-НЕ.

Рис.3. УГО символов, спроектированных для реализации схемы замещения ИМ3.

Вышеперечисленные элементы создавались путём редактирования зарубежных компонентов, что потребовало также скопировать динамические модели используемых элементов из 74ls.lib в файл k555im3.lib (функциональные модели элементов представлены в приложении 1).

Для соответствия реальных задержек распространения с задержками схемы замещения возникла необходимость создать элемент K555LI1A, задержки которого будут отличаться от элемента K555LI1.

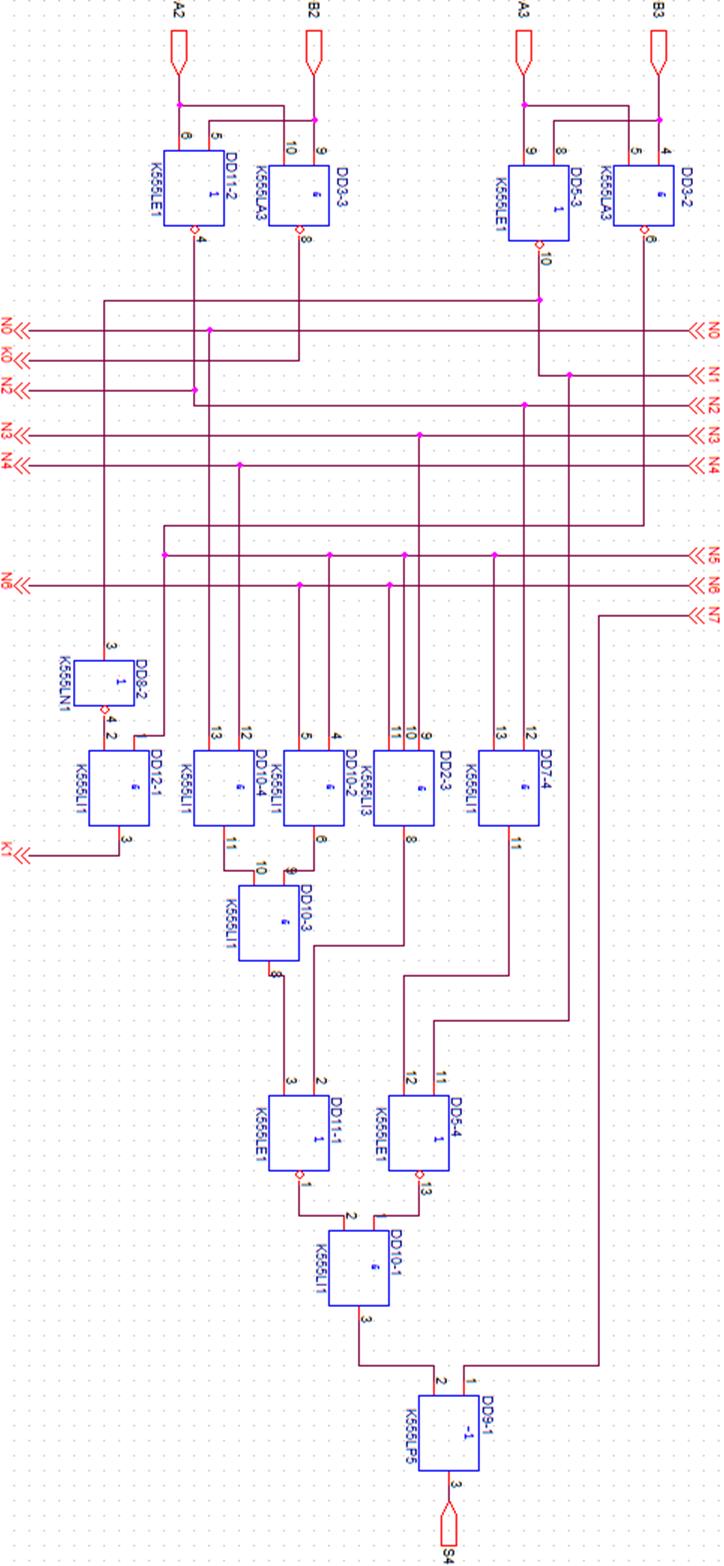

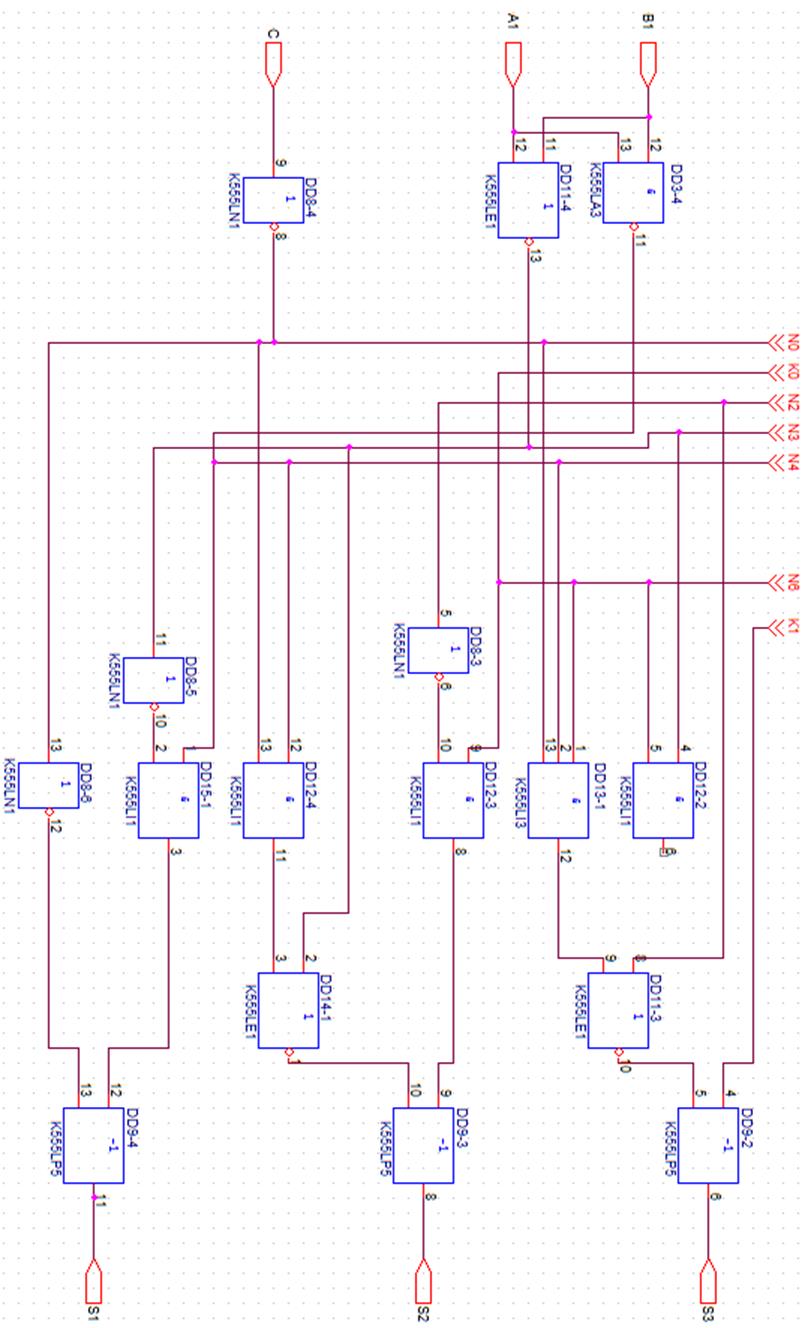

Для лучшего восприятия, принципиальная схема замещения была разбита на три страницы, которые представлены далее (стр. 8-10; рис. 4.1-4.3).

.

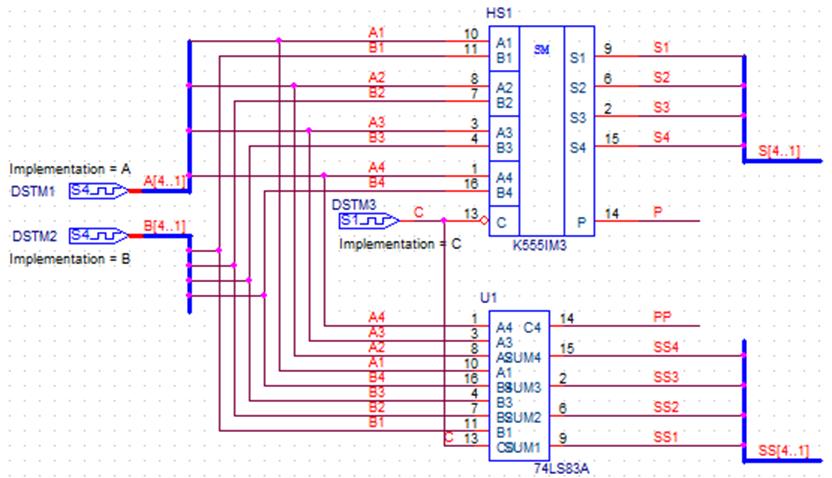

Для более наглядной верификации иерархического символа (HS1) и возможности сравнения с зарубежным аналогом было принято решение добавить в схему верификации зарубежный аналог 74ls83a (U1), взятый из библиотеки 74ls. Чтобы не засорять схему верификации, маркеры напряжения не показаны. Верификация узла проводилась для максимальных задержек.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.