Министерство образования и науки РФ

Новосибирский Государственный Технический Университет

Кафедра ВТ

Курсовая работа

по дисциплине

Факультет: АВТ

Группа: АМ-209

Студент: Клименков В.

Преподаватель: Шалагинов А. В.

Новосибирск

2005

Содержание

1. Постановка задачи.. 3

2. Условное графическое обозначение моделируемого узла.. 3

3. Назначение выводов узла.. 3

4. Режимы работы узла.. 3

5. Реальные задержки работы узла.. 4

6. Описание работы узла.. 4

7. Моделирование узла в пакете DesignLab 8. 5

7.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 5

7.2. Схема замещения узла. 5

7.3. Текстовое SPICE-описание моделируемого узла. 8

7.4. Файл описания внешних воздействий. 10

7.5. Схема верификации иерархического символа. 10

7.6. Результаты моделирования узла. 11

7.7. Оценка предельных скоростных возможностей исследуемого узла. 13

7.8. Функциональное описание проектируемого узла. 13

7.9. Схема верификации символа с подключённой макромоделью.. 15

7.10. Результаты моделирования символа с подключённой макромоделью.. 15

8. Моделирование узла в пакете OrCAD 9.1. 15

8.1. Условное графическое изображение проектируемого узла в виде иерархического символа. 15

8.2. Принципиальная схема замещения узла. 15

8.3. Схема верификации иерархического символа. 18

8.4. Результаты моделирования узла. 18

8.5. Поведенческая VHDL-модель узла. 20

8.6. Схема верификации узла с подключённой VHDL-моделью.. 21

8.7. Результаты моделирования VHDL-модели узла. 22

Выводы... 23

Список литературы... 24

Приложения.. 25

Приложение 1. Макромодели элементов схемы.. 25

Приложение 2. VHDL-модели элементов схемы.. 28

Создать структурные и поведенческие модели исследуемого цифрового узла в пакетах DesignLab 8, OrCad 9.1. Провести имитационные эксперименты с разработанным узлом, подтвердить его работоспособность и соответствие временных задержек требуемым. Провести сравнительный анализ инструментальных средств проектирования и сформулировать выводы и личные впечатления о них.

В качестве исследуемого узла взят элемент К555IM6 (двоичный 4-разрядный сумматор).

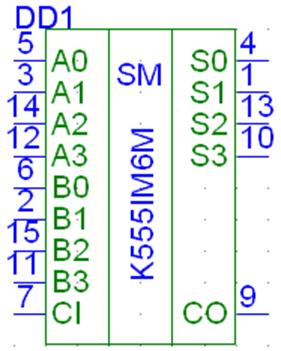

Рис 1. Условное графическое обозначение узла, выполненное в пакете DesignLab.

Таблица 1. Выводы узла и их назначения

|

Номер вывода |

Обозначение |

Назначение |

|

01 |

S1 |

Выход суммы |

|

02 |

B1 |

Вход данных |

|

03 |

A1 |

Вход данных |

|

04 |

S0 |

Выход суммы |

|

05 |

A0 |

Вход данных |

|

06 |

B0 |

Вход данных |

|

07 |

CI |

Вход переноса |

|

09 |

CO |

Выход переноса |

|

10 |

S3 |

Выход суммы |

|

11 |

B3 |

Вход данных |

|

12 |

A3 |

Вход данных |

|

13 |

S2 |

Выход суммы |

|

14 |

A2 |

Вход данных |

|

15 |

B2 |

Вход данных |

Таблица 2. Логическая таблица режимов работы узла

|

Входы |

Выходы |

Примечание |

||

|

A3-А0 |

B3-В0 |

CI |

CO, S3-S0 |

|

|

A |

B |

0 |

A + B |

Без входного переноса |

|

A |

B |

1 |

A + B + 1 |

Со входным переносом |

Таблица 3. Максимальные задержки К555ИМ6

|

Время распространения сигнала: |

Максимальное значение, нс |

|

Время задержки распространения сигнала от входов до выходов S3-S0 |

24 |

|

Время задержки распространения сигнала от входов до выхода CO |

17 |

Микросхема K555IM6 представляет собой двоичный 4-разрядный сумматор. Он производит суммирование двух четырёхразрядных двоичных слов и входного переноса. Результатом является четырёхразрядное двоичное слово и выходной перенос. При возникновении переполнения операции суммирования выход переноса устанавливается в единичное состояние.

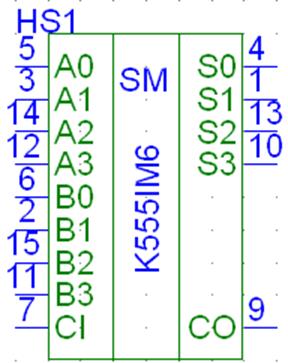

рис 2. Условное графическое изображение узла в виде иерархического символа

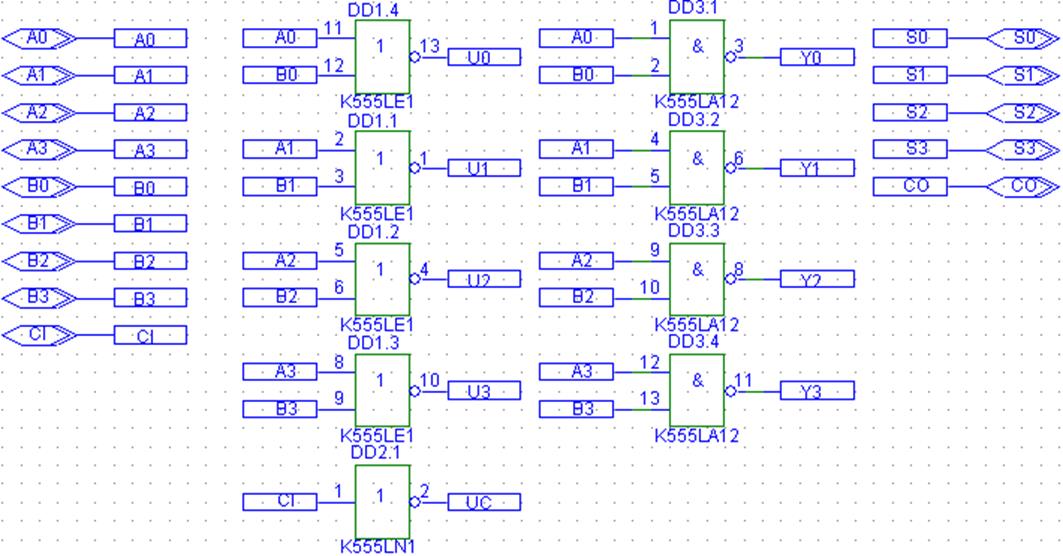

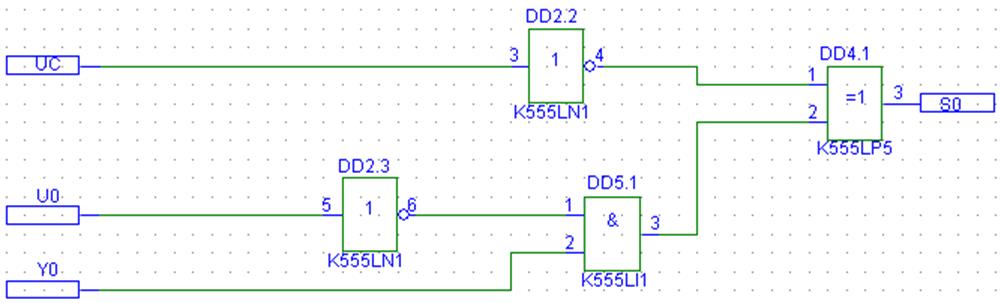

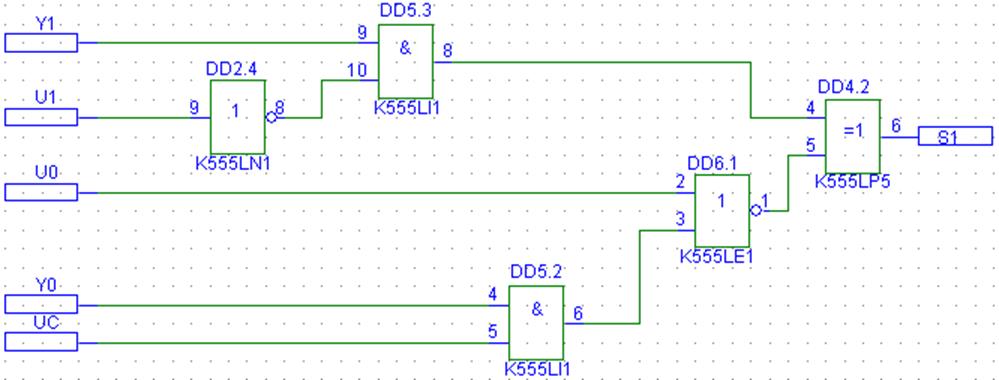

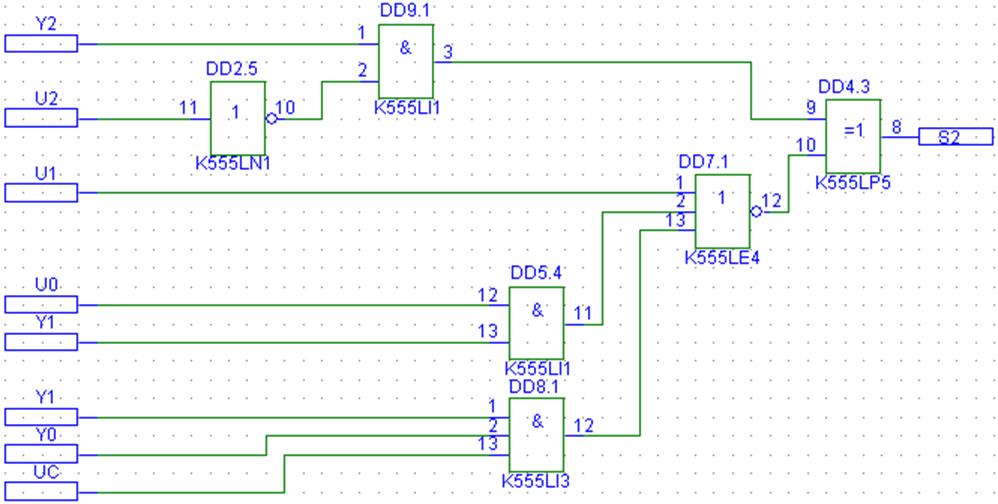

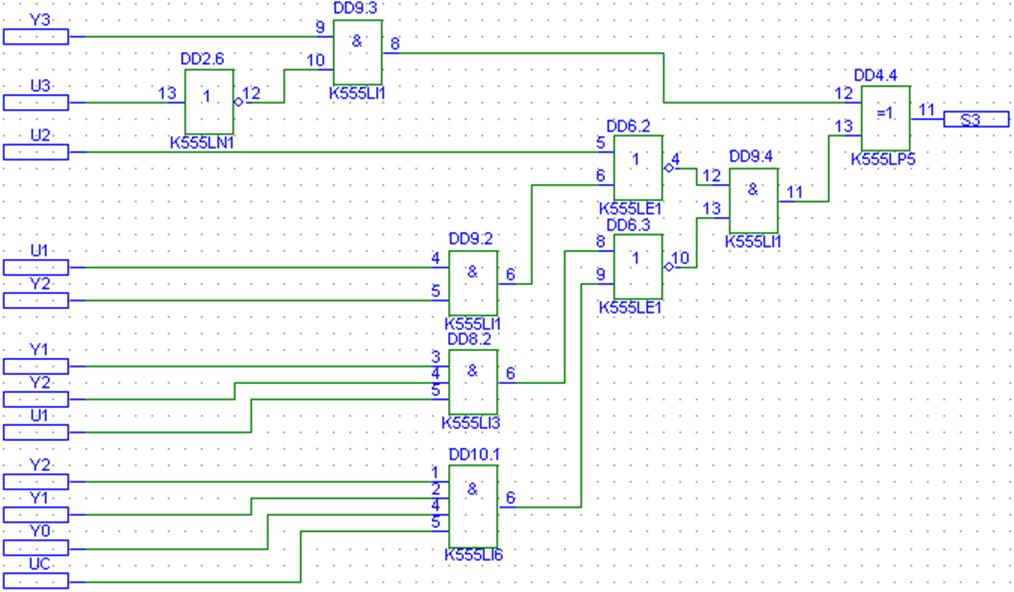

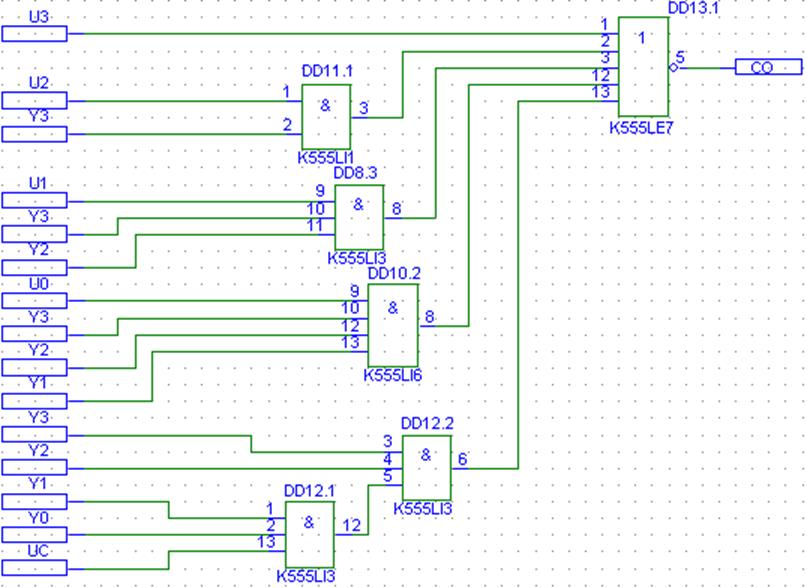

Схема замещения проектируемого узла размещена на шести страницах (рис 3-8.).

Рис 3. Схема замещения узла (Page 1)

Рис 4. Схема замещения узла (Page 2)

Рис 5. Схема замещения узла (Page 3)

Рис 6. Схема замещения узла (Page 4)

Рис 7. Схема замещения узла (Page 5)

Рис 8. Схема замещения узла (Page 6)

Все элементы данной схемы имеют реальные прототипы. Макромодели всех элементов данной схемы представлены в приложении 1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.