рис 25. Файл my_lib.lib

рис 26. Схема верификации символа с подключённой макромоделью

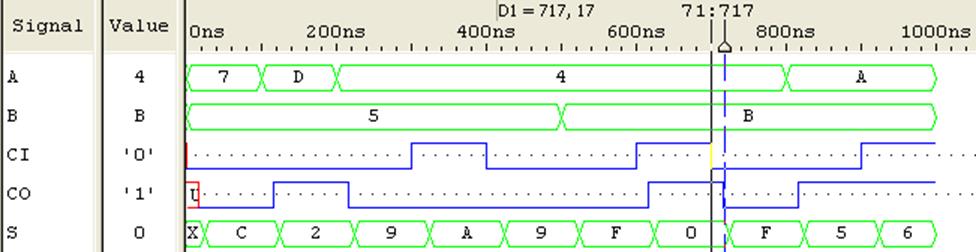

рис 27. Временные диаграммы моделирования символа с подключённой макромоделью

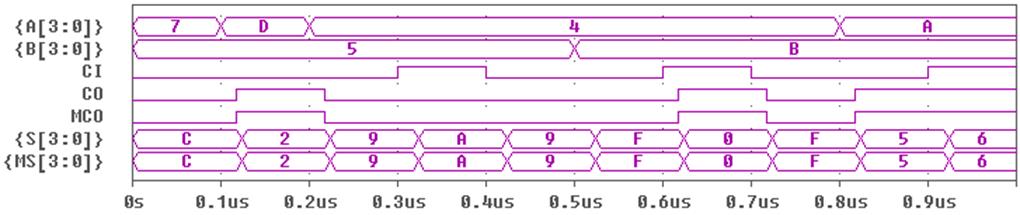

рис 28. Сравнение временных диаграмм моделирования узла со схемой замещения и макромоделью

рис 29. Условное графическое изображение узла в виде иерархического символа

Принципиальная схема замещения проектируемого узла размещена на шести страницах (рис. 28-33.).

Рис 30. Принципиальная схема замещения узла (Page 1)

Рис 31. Принципиальная схема замещения узла (Page 2)

Рис 32. Принципиальная схема замещения узла (Page 3)

Рис 33. Принципиальная схема замещения узла (Page 4)

Рис 34. Принципиальная схема замещения узла (Page 5)

Рис 35. Принципиальная схема замещения узла (Page 6)

Все элементы данной схемы имеют реальные прототипы. VHDL-модели всех элементов данной схемы представлены в приложении 2.

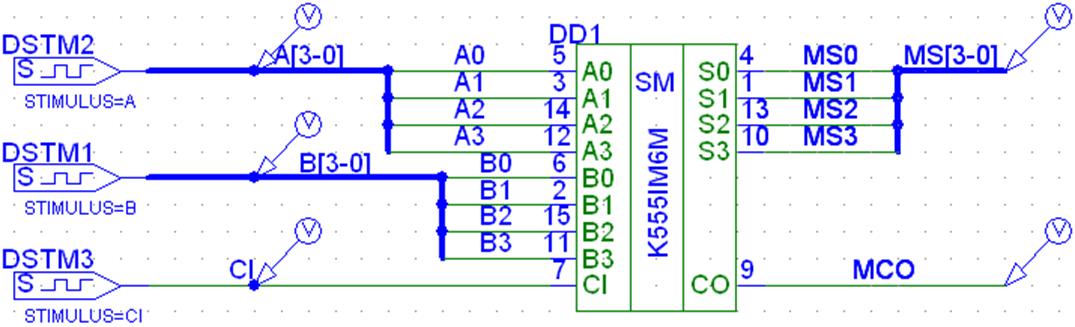

рис 36. Схема верификации иерархического символа

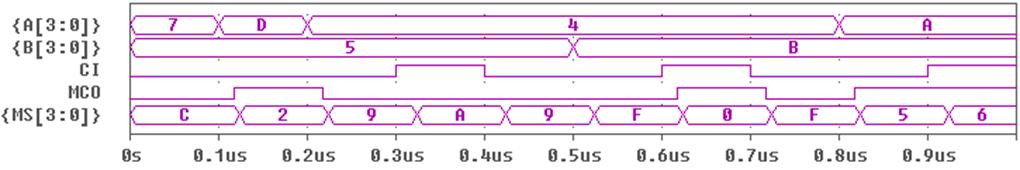

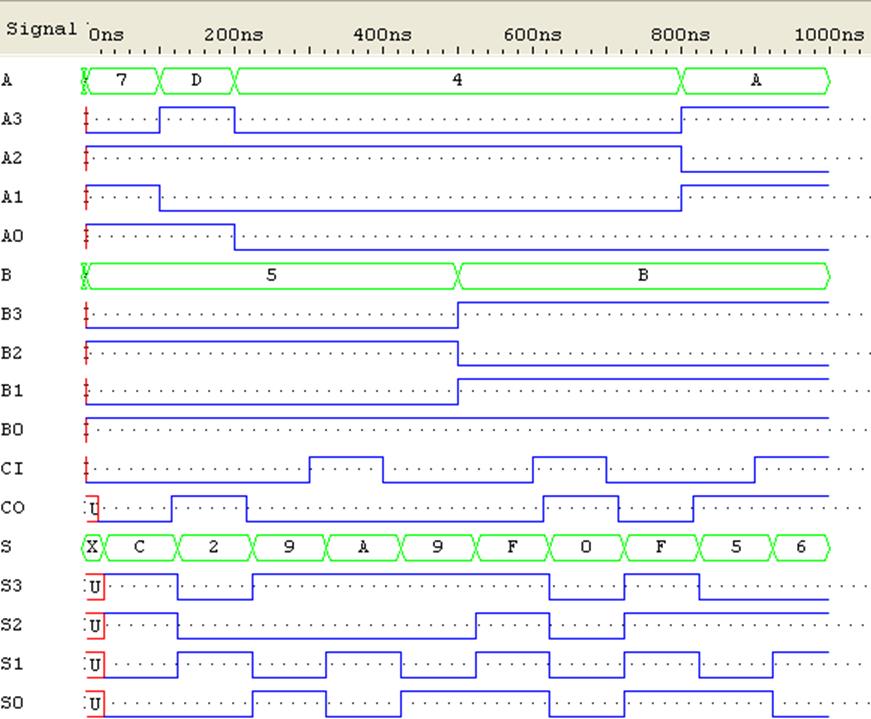

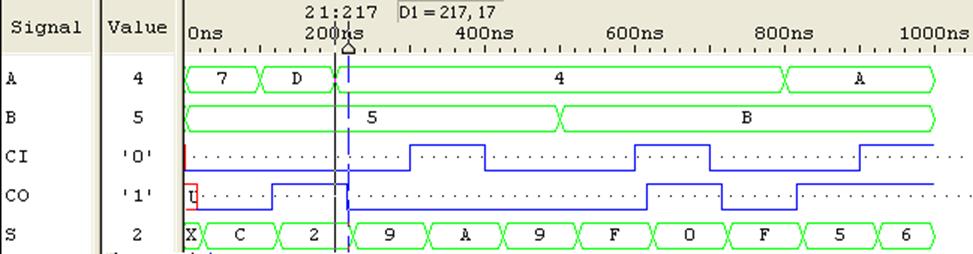

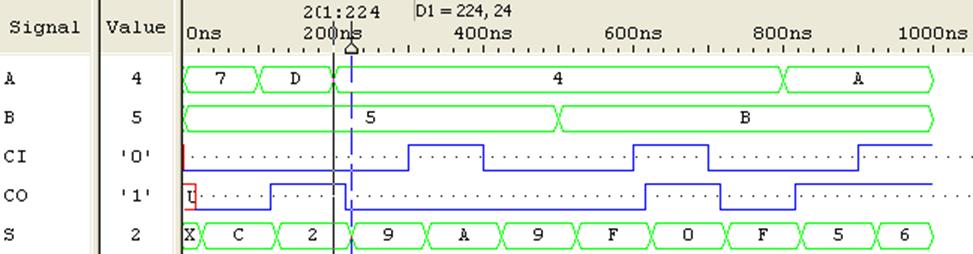

рис 37. Временные диаграммы моделирования узла

Пояснения к временным диаграммам моделирования узла:

· 0-100ns, 200-300ns, 400-600ns, 700-800ns — суммирование без переносов (входного и выходного)

· 100-200ns, 800-900ns — формируется выходной перенос

· 300-400ns — входной перенос увеличивает результат на единицу

· 600-700ns — входной перенос увеличивает результат на единицу, что вызывает переполнение и формирует выходной перенос

· 900-1000ns — переполнение при суммирование уже сформировало выходной перенос. Входной перенос лишь увеличивает значение суммы на единицу.

Измерение времени задержек распространения сигналов:

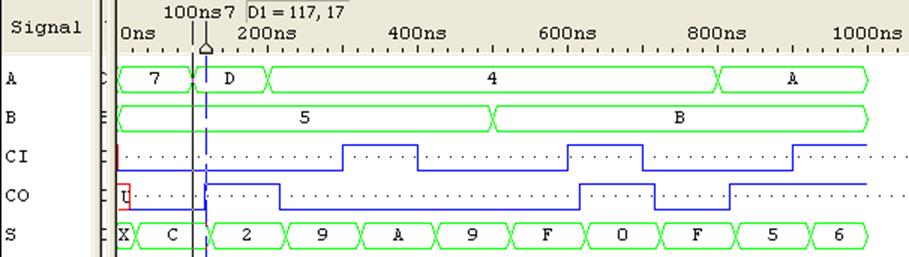

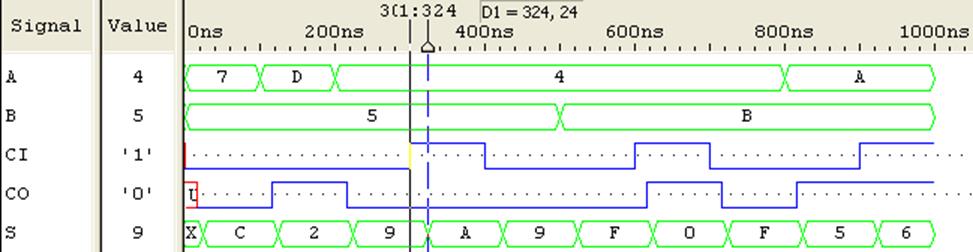

рис 38. Время задержки распространения сигнала от входов А до выхода СО (17 нс)

рис 39. Время задержки распространения сигнала от входов А до выходов S (24 нс)

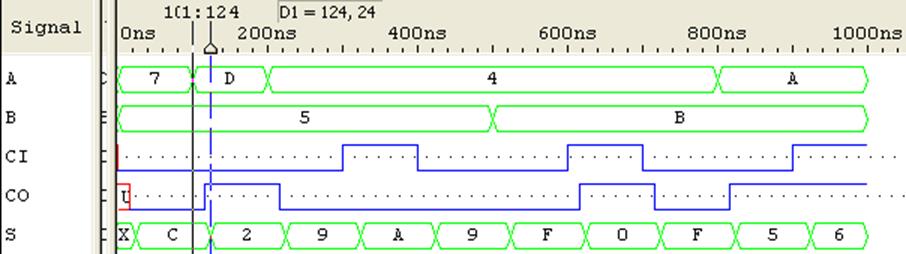

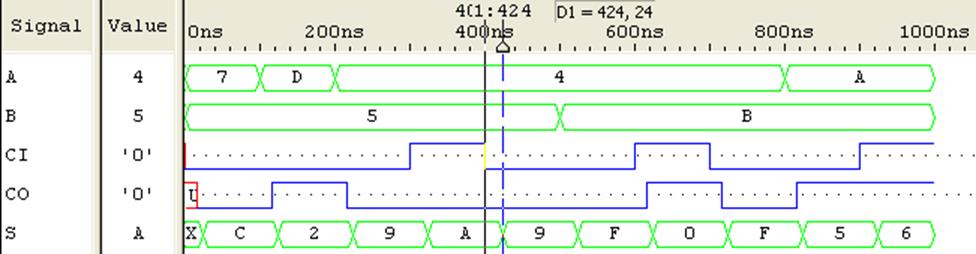

рис 40. Время задержки распространения сигнала от входов А до выхода СО (17 нс)

рис 41. Время задержки распространения сигнала от входов А до выходов S (24 нс)

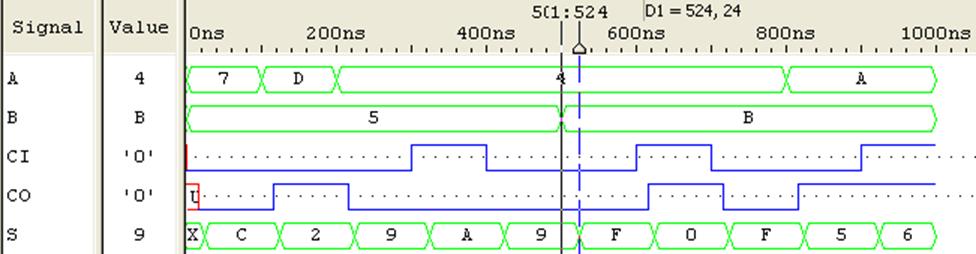

рис 42. Время задержки распространения сигнала от входа CI до выходов S (24 нс)

рис 43. Время задержки распространения сигнала от входа CI до выходов S (24 нс)

рис 44. Время задержки распространения сигнала от входов В до выходов S (24 нс)

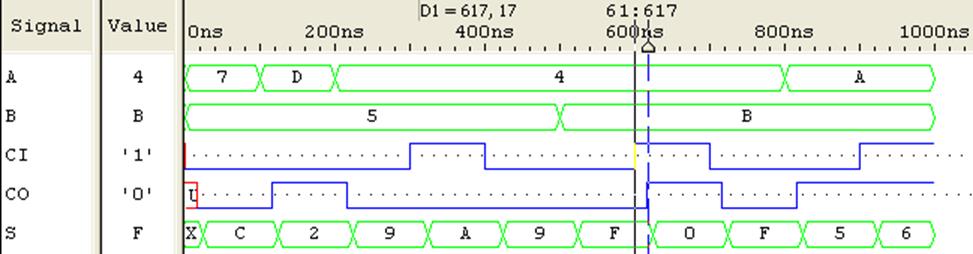

рис 45. Время задержки распространения сигнала от входа CI до выхода СО (17 нс)

рис 46. Время задержки распространения сигнала от входа CI до выхода СО (17 нс)

LIBRARY ieee; -- подключение необходимых библиотек

USE ieee.std_logic_unsigned.all;

USE ieee.std_logic_arith.all;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \K555IM6M\ IS PORT( --входы и выходы

A0 : IN std_logic;

A1 : IN std_logic;

A2 : IN std_logic;

A3 : IN std_logic;

B0 : IN std_logic;

B1 : IN std_logic;

B2 : IN std_logic;

B3 : IN std_logic;

CI : IN std_logic;

S0 : OUT std_logic;

S1 : OUT std_logic;

S2 : OUT std_logic;

S3 : OUT std_logic;

CO : OUT std_logic

);END \K555IM6M\;

ARCHITECTURE model OF \K555IM6M\ IS -- архитектура узла

BEGIN -- начало описания архитектуры

PROCESS(A0,A1,A2,A3,B0,B1,B2,B3,CI) -- процесс, который обрабатывается при

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.