--изменении сигнала на входе

variable A: std_logic_vector(3 downto 0); --вектор, для объединения данных А

variable B: std_logic_vector(3 downto 0); --вектор, для объединения данных B

variable Y: std_logic_vector(4 downto 0); --вектор, для результата суммирования

BEGIN

A := (A3,A2,A1,A0); --присвоение

B := (B3,B2,B1,B0); --входных значений

Y := ('0'&A)+('0'&B)+("0000"&CI); --вычисление суммы

S0 <=Y(0) AFTER 24NS; --передача

S1 <=Y(1) AFTER 24NS; --результата

S2 <=Y(2) AFTER 24NS; --на выходы

S3 <=Y(3) AFTER 24NS; --с соответствующими

CO <=Y(4) AFTER 17NS; --задержками

END PROCESS; -- окончание описания процесса

END model; -- окончания описания архитектуры

рис 47. Поведенческая VHDL-модель узла

рис 48. Схема верификации узла с подключенной VHDL-моделью

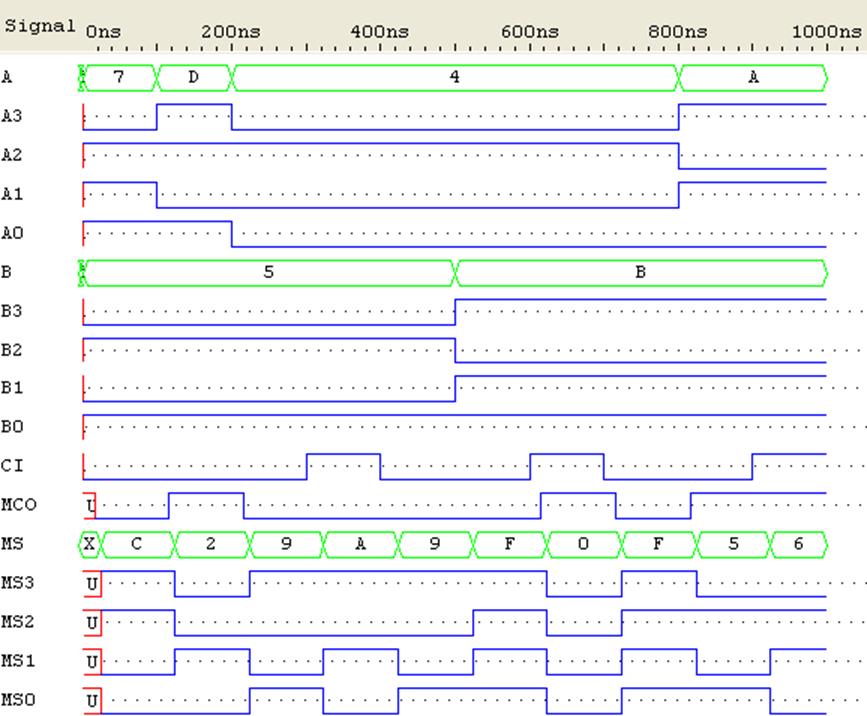

рис 49. Временные диаграммы моделирования VHDL-модели узла

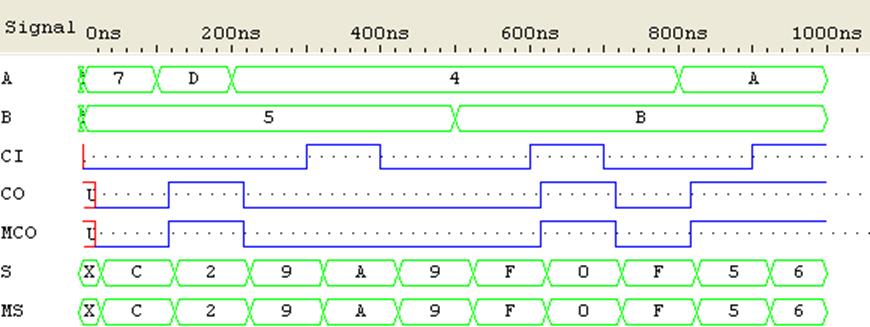

рис 50. Сравнение временных диаграмм моделирования узла со схемой замещения и VHDL-модели узла

Моделирование узла предложенного по варианту (4-разрядного двоичного сумматора K555IM6) было выполнено мною в двух пакетах (DesignLab 8.0 и OrCAD 9.1).

Структурные и поведенческие модели узла были выполнены с использованием справочных данных (задержки и схемы узла). Для обоих пакетов использовались идентичные диаграммы входных воздействий, что обеспечило идентичность работы всех созданных мною узлов. Для наглядного представления идентичности задержек, «заложенных» в макромодель (VHDL-модель) задержкам, измеренным на схеме замещения узла мною были приведены диаграммы параллельной работы обоих узлов.

При выполнении курсовой работы мне больше понравился пакет OrCAD. Его сравнение и основные превосходства над пакетом DesignLab я приведу ниже.

При запуске DesignLab’а происходит открытие порядка трёх окон приложений, а при моделировании порядка пяти окон. В OrCAD’е соответственно — одно и два. Это упрощает работу как с самим пакетом, так и с операционной средой компьютера в целом.

При создании схем в пакете OrCAD можно не соединять проводники, чтобы указать их принадлежность к одной цепи. В DesignLab’е без этого не обойтись. Оба пакета поддерживают многостраничные схемы. А так схема замещения проектируемого узла довольно громоздка, то я сразу создавал её на нескольких страницах. Это позволило не экономить место при размещении элементов, да и не вызвало путаницы в собранном.

Для задания внешних воздействий в DesignLab’е в схему должны быть включены генераторы внешних воздействий. В OrCAD’е достаточно задать цепям корректные имена.

Единственное чем уступает OrCAD DesignLab’e так это редактором внешних воздействий. Графическое задание сигналов конечно же проще. Но и к OrCAD’у можно со временем приловчиться.

Пакет OrCAD может корректно использовать буфер обмена Windows в отличии от DesignLab’а. В этом я убедился при оформлении отчёта. При попытки вставки выделенных объектов из DesignLab’а, я не получал никакого результата. Видимо буфер здесь внутренний. Вставка же объектов из OrCAD’а выполнялась успешно. Даже часть временных диаграмм включено в отчёт напрямую из OrCAD’а (общие временные диаграммы).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.