+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD10_1 HS1_Y2 HS1_Y1 HS1_Y0 HS1_UC $N_0018 $G_DPWR $G_DGND

+ K555LI6 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD6_2 HS1_U2 $N_0013 $N_0019 $G_DPWR $G_DGND K555LE1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD9_4 $N_0019 $N_0020 $N_0017 $G_DPWR $G_DGND K555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD6_3 $N_0014 $N_0018 $N_0020 $G_DPWR $G_DGND K555LE1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD11_1 HS1_U2 HS1_Y3 $N_0021 $G_DPWR $G_DGND K555LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD8_3 HS1_U1 HS1_Y3 HS1_Y2 $N_0022 $G_DPWR $G_DGND K555LI3

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD10_2 HS1_U0 HS1_Y3 HS1_Y2 HS1_Y1 $N_0023 $G_DPWR $G_DGND

+ K555LI6 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD12_1 HS1_Y1 HS1_Y0 HS1_UC $N_0024 $G_DPWR $G_DGND K555LI3

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD12_2 HS1_Y3 HS1_Y2 $N_0024 $N_0025 $G_DPWR $G_DGND K555LI3

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD13_1 HS1_U3 $N_0021 $N_0022 $N_0023 $N_0025 HS1_CO $G_DPWR

+ $G_DGND K555LE7 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Рис 10. Файл ver1.net

* D:\IM6\DL8\ver.stl written on Sun Nov 27 18:44:35 2005

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! B Digital A Digital CI Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 1us

;!AutoUniverse

;!XminRes 50ns

;!YminRes 1n

;!Ok

.STIMULUS CI STIM (1, 1)

+ +0s 0

+ 300ns 1

+ 400ns 0

+ 600ns 1

+ 700ns 0

+ 900ns 1

.STIMULUS A STIM (4, 1111) ;! Hex

+ +0s 0111

+ 100ns 1101

+ 200ns 0100

+ 800ns 1010

.STIMULUS B STIM (4, 1111) ;! Hex

+ +0s 0101

+ 500ns 1011

Рис 11. Файл ver.stl

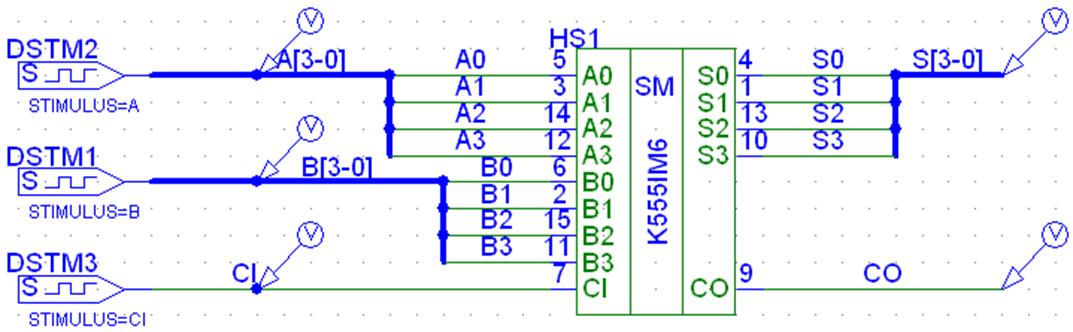

рис 12. Схема верификации иерархического символа

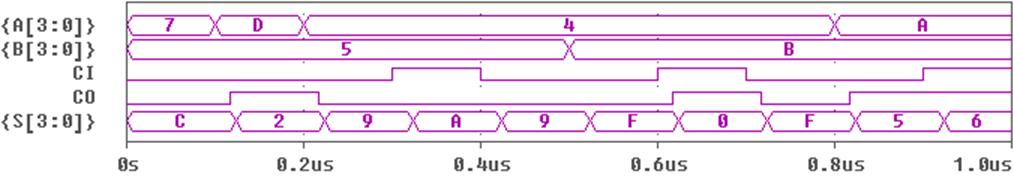

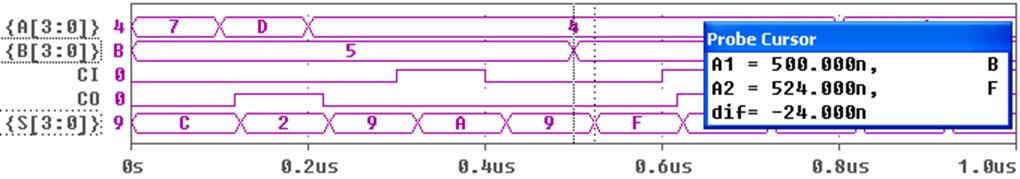

рис 13. Временные диаграммы моделирования узла

Пояснения к временным диаграммам моделирования узла:

· 0-100ns, 200-300ns, 400-600ns, 700-800ns — суммирование без переносов (входного и выходного)

· 100-200ns, 800-900ns — формируется выходной перенос

· 300-400ns — входной перенос увеличивает результат на единицу

· 600-700ns — входной перенос увеличивает результат на единицу, что вызывает переполнение и формирует выходной перенос

· 900-1000ns — переполнение при суммирование уже сформировало выходной перенос. Входной перенос лишь увеличивает значение суммы на единицу.

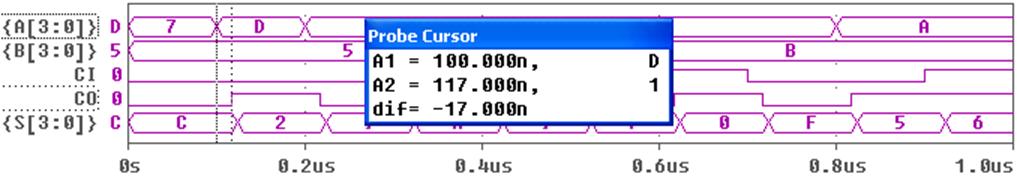

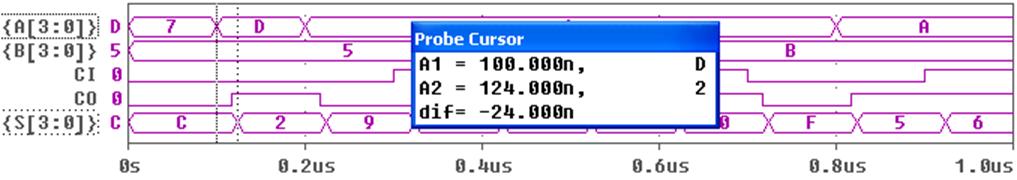

Измерение времени задержек распространения сигналов:

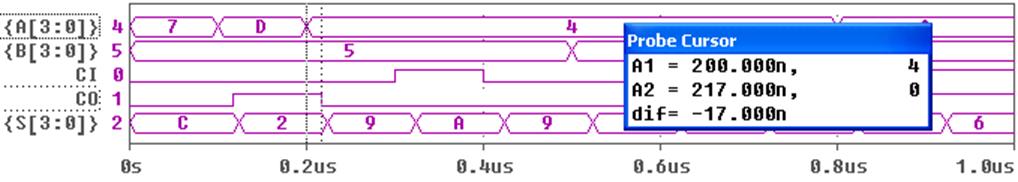

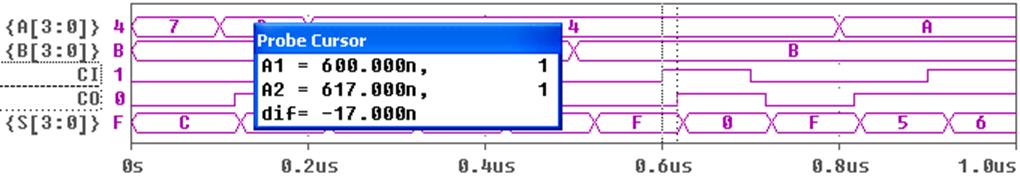

рис 14. Время задержки распространения сигнала от входов А до выхода СО (17 нс)

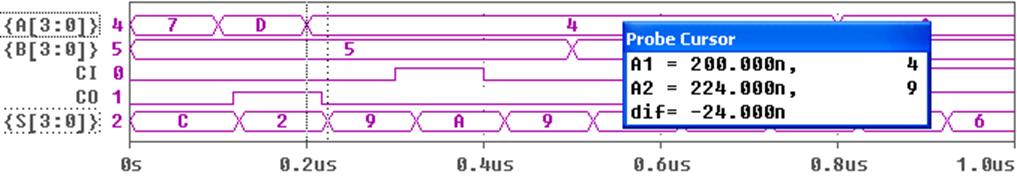

рис 15. Время задержки распространения сигнала от входов А до выходов S (24 нс)

рис 16. Время задержки распространения сигнала от входов А до выхода СО (17 нс)

рис 17. Время задержки распространения сигнала от входов А до выходов S (24 нс)

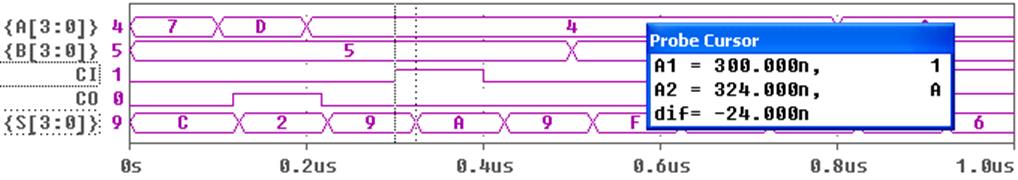

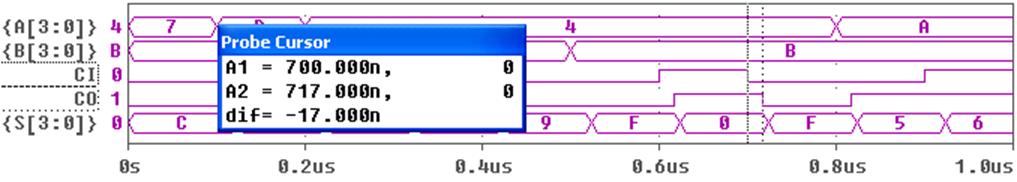

рис 18. Время задержки распространения сигнала от входа CI до выходов S (24 нс)

рис 19. Время задержки распространения сигнала от входа CI до выходов S (24 нс)

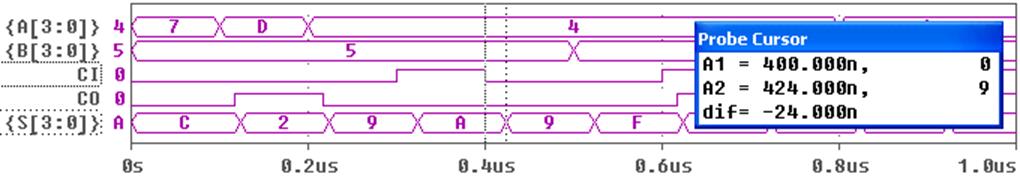

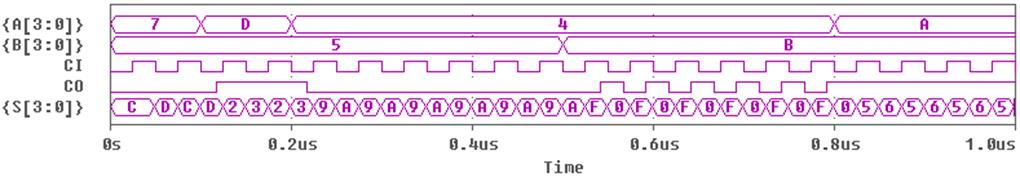

рис 20. Время задержки распространения сигнала от входов В до выходов S (24 нс)

рис 21. Время задержки распространения сигнала от входа CI до выхода СО (17 нс)

рис 22. Время задержки распространения сигнала от входа CI до выхода СО (17 нс)

Предельная частота изменения сигналов на входах узла (он является комбинационной схемой) – величина, обратная максимальной задержке распространения сигнала от входа до выхода.

fmax = 1 / 24нс = 41,67 МГц

Временная диаграмма работы узла при изменении сигнала на входе CI с частотой 40 МГц представлена на рис. 23.

Рис. 23. Временная диаграмма работы узла при изменении сигнала на входе CI с частотой 40 МГц

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.