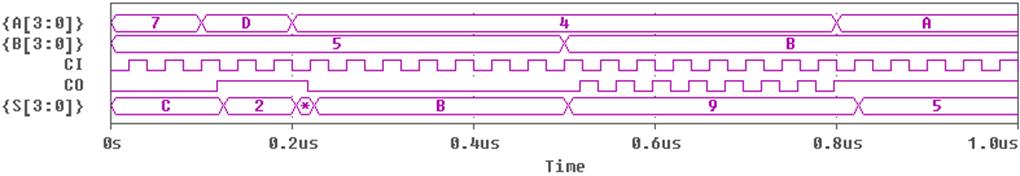

Эксперименты показали, что при увеличении частоты изменения сигнала узел работает некорректно. Это отражено на рис. 24.

Рис. 24. Временная диаграмма работы узла при изменении сигнала на входе CI с частотой 50 МГц

Потоковая модель проектируемого узла:

* K555IM6M 4-разрядный двоичный сумматор

*

* TTL LOGIC STANDARD TTL, SCHOTTKY, LOW-POWER SCHOTTKY DATA BOOK, 1988, TI

* NH 8/26/92 REMODELED USING LOGICEXP, PINDLY, CONSTRAINT DEVICES

*

.SUBCKT K555IM6M имя макромодели

+ CI A0 A1 A2 A3 B0 B1 B2 B3 C4 входы

+ S0 S1 S2 S3 выходы

+ OPTIONAL: DPWR = $G_DPWR DGND = $G_DGND

+ PARAMS: MNTYMXDLY = 0 IO_LEVEL = 0

*

U555IM6MLOG LOGICEXP(9,14) DPWR DGND блок LOGICEXP

+ CI A0 A1 A2 A3 B0 B1 B2 B3 входы

+ CI_INT A0_INT A1_INT A2_INT A3_INT B0_INT B1_INT B2_INT B3_INT C4_INT S0_INT S1_INT S2_INT S3_INT выходы

+ D0_GATE IO_LS IO_LEVEL = {IO_LEVEL}

+

+ LOGIC:

+ CI_INT= { CI }

+ A0_INT = { A0 }

+ A1_INT = { A1 }

+ A2_INT = { A2 }

+ A3_INT = { A3 }

+ B0_INT = { B0 }

+ B1_INT = { B1 }

+ B2_INT = { B2 }

+ B3_INT = { B3 }

+

+ NAND4 = { ~(A3_INT & B3_INT) }

+ NAND3 = { ~(A2_INT & B2_INT) }

+ NAND2 = { ~(A1_INT & B1_INT) }

+ NAND1 = { ~(A0_INT & B0_INT) }

+ NOR4 = { ~(A3_INT | B3_INT) }

+ NOR3 = { ~(A2_INT | B2_INT) }

+ NOR2 = { ~(A1_INT | B1_INT) }

+ NOR1 = { ~(A0_INT | B0_INT) }

+ C0BAR = { ~CI_INT}

+

+ S0_INT = { (NAND1 & ~NOR1) ^ CI_INT}

+ S1_INT = { (NAND2 & ~NOR2) ^ (~(NOR1 | (NAND1 & C0BAR))) }

+ S2_INT = { (NAND3 & ~NOR3) ^ (~(NOR2 | (NOR1 & NAND2) |

+ (NAND2 & NAND1 & C0BAR))) }

+ S3_INT = { (NAND4 & ~NOR4) ^ (~(NOR3 | (NOR2 & NAND3) |

+ (NOR1 & NAND3 & NAND2) | (NAND3 & NAND2 & NAND1 & C0BAR))) }

+ C4_INT = { ~( NOR4 | (NOR3 & NAND4) | (NOR2 & NAND4 & NAND3) |

+ (NOR1 & NAND4 & NAND3 & NAND2) |

+ (NAND4 & NAND3 & NAND2 & NAND1 & C0BAR) ) }

*

U555IM6MDLY PINDLY (5,0,9) DPWR DGND блок PINDLY

+ S0_INT S1_INT S2_INT S3_INT C4_INT входы (пути), для которых вычисляется задержка

+ CI_INT A0_INT A1_INT A2_INT A3_INT B0_INT B1_INT B2_INT B3_INT внутренние узлы, от которых зависит задержка

+ S0 S1 S2 S3 C4 выходы, для которых вычисляется задержка

+ IO_LS MNTYMXDLY = {MNTYMXDLY} IO_LEVEL = {IO_LEVEL}

+

+ BOOLEAN:

+ ANY_CH_AB = { CHANGED(A0_INT,0) | CHANGED(B0_INT,0) | CHANGED(A1_INT,0) |

+ CHANGED(B1_INT,0) | CHANGED(A2_INT,0) | CHANGED(B2_INT,0) |

+ CHANGED(A3_INT,0) | CHANGED(B3_INT,0) }

+

+ PINDLY:

+ S0 S1 S2 S3 = { *задержка до выходов S (24 ns)

+ CASE(

+ ANY_CH_AB, DELAY(-1,15NS,24NS),

+ CHANGED(CI_INT,0) & TRN_LH, DELAY(-1,16NS,24NS),

+ CHANGED(CI_INT,0) & TRN_HL, DELAY(-1,15NS,24NS),

+ DELAY(-1,17NS,24NS) ;DEFAULT

+ )

+ }

+ C4 = { *задержка до выхода CO (17 ns)

+ CASE(

+ CHANGED(CI_INT,0) & TRN_HL, DELAY(-1,11NS,17NS),

+ ANY_CH_AB & TRN_HL, DELAY(-1,12NS,17NS),

+ (ANY_CH_AB | CHANGED(CI_INT,0)) & TRN_LH, DELAY(-1,11NS,17NS),

+ DELAY(-1,16NS,17NS) ;DEFAULT

+ )

+ }

*

.ENDS

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.