Министерство образования и науки РФ

Новосибирский государственный технический университет

Кафедра ВТ

Пояснительная записка к курсовой работе

по дисциплине

“Моделирование”

Факультет: АВТ

группа: АМ-209

студенты: Феклин В.В.

преподаватель: Шалагинов А.В. Дата сдачи:

НОВОСИБИРСК 2005

Оглавление

|

1. Постановка задачи |

3 |

|

2. Описание моделируемой ИМС |

3 |

|

2.1. Условное графическое обозначение моделируемого узла |

3 |

|

2.2. Назначение выводов |

4 |

|

2.3. Режимы работы |

5 |

|

2.4. Динамические характеристики |

5 |

|

2.5. Подробное описание работы моделируемого узла |

5 |

|

3. Моделирование узла в пакете DesignLab_8 |

7 |

|

3.1. Условное графическое изображение моделируемого узла в виде иерархического символа |

7 |

|

3.2. Схема замещения моделируемого узла |

7 |

|

3.3. Текстовое SPICE-описание моделируемого узла |

8 |

|

3.3.1. Содержимое файла HS_Schem_2.cir |

8 |

|

3.3.2. Содержимое файла HS_Schem_2.net |

8 |

|

3.4. Описание диаграмм входных сигналов |

9 |

|

3.5. Тестирование разработанных моделей |

9 |

|

3.6. Оценка предельных скоростных возможностей исследуемого узла |

12 |

|

3.7. Функциональное описание моделируемого узла с помощью примитивов LOGICEXP, PINDLY и CONSTRAINT |

13 |

|

3.8. Тестирование макромодели моделируемого узла |

15 |

|

4. Моделирование узла в пакете OrCAD_9.1 |

16 |

|

4.1. Условное графическое обозначение моделируемого узла |

16 |

|

4.2. Схема замещения моделируемого узла |

16 |

|

4.3. Результаты моделирования узла в пакете OrCAD_9.1 |

17 |

|

4.4. Поведенческая VHDL-модель узла |

20 |

|

4.5. Тестирование разработанной поведенческой VHDL-модели |

22 |

|

5. Моделирование узла в пакете ACTIVE-HDL_6 |

25 |

|

5.1. Условное графическое обозначение моделируемо узла |

25 |

|

5.2. Схема замещения моделируемого узла |

26 |

|

5.3. Поведенческая VHDL-модель моделируемого узла |

26 |

|

5.4. Результаты моделирования в пакете ACTIVE-HDL |

26 |

|

Выводы |

30 |

|

Список используемой литературы |

32 |

1. Постановка задачи

Для заданной ИМС создать модели в средах проектирования DesignLab_8, OrCad_9.1 и Active-HDL_6.1. Провести эксперименты над разработанными моделями. Модели построить в двух вариантах: поведенческие и на схемах замещения. Эксперименты должны быть полными: отображать все режимы работы ИМС и соответствующие этим режимам задержки.

Провести сравнительный анализ используемых сред проектирования.

Исследуемая ИМС – КР1554ИР23.

2. Описание моделируемой ИМС

2.1. Условное графическое обозначение моделируемого узла

Микросхема КР1554ИР23 представляет собой восьмиразрядный регистр на D-триггерах с динамическим С-входом и параллельной загрузкой\выводом данных . Выходные буферные каскады микросхемы имеют третье состояние.

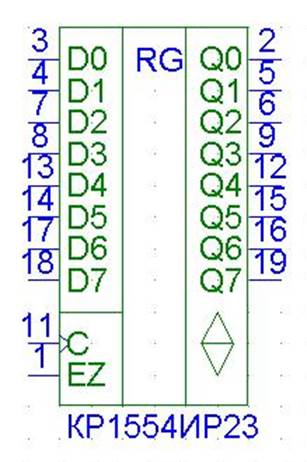

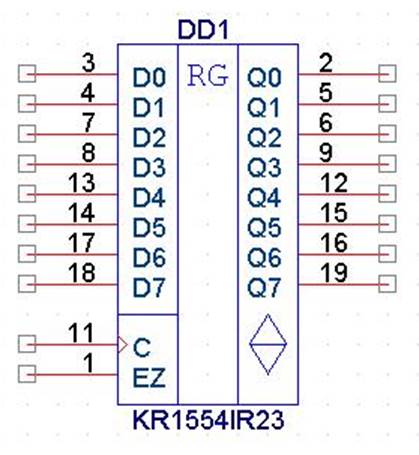

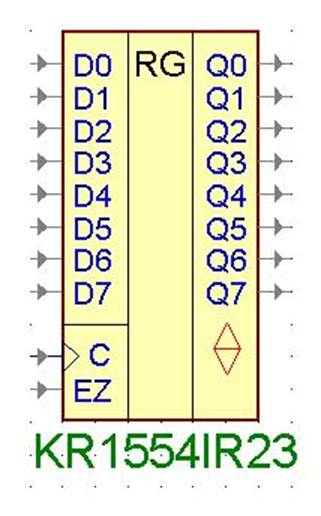

Моделируемый узел представлен тремя УГО, используемыми в различных средах проектирования (DesignLab_8, OrCad_9.1 и Active-HDL_6.1). На рисунках 1, 2 и 3 приведены УГО узла.

Рис.1 УГО моделируемого узла в пакете DesignLab 8

Рис.2 УГО моделируемого узла в пакете OrCad 9.1

Рис.3 УГО моделируемого узла в пакете ACTIVE-HDL_6.1

2.2. Назначение выводов

На УГО узел имеет 18 выводов, а реальное количество выводов моделируемой ИМС – 20 штук (на УГО скрыты выводы питания и земли).

В таблице 1 указаны назначения выводов моделируемой ИМС (данные взяты из источника №1 списка литературы, стр.393).

Таблица 1. Назначение выводов

|

№ |

Обозначение |

Назначение |

|

1 |

EZ |

Вход разрешения состояния высокого импеданса выхода (управление выходными буферами) |

|

2 |

Q0 |

Выход данных (выходы имеют третье состояние) |

|

3 |

D0 |

Вход данных (параллельная загрузка данных по фронту С) |

|

4 |

D1 |

Вход данных |

|

5 |

Q1 |

Выход данных |

|

6 |

Q2 |

Выход данных |

|

7 |

D2 |

Вход данных |

|

8 |

D3 |

Вход данных |

|

9 |

Q3 |

Выход данных |

|

10 |

GND |

Общий вывод (земля) |

|

11 |

C |

Вход тактового импульса (динамический вход загрузки данных (по фронту) со входов D0-D7) |

|

12 |

Q4 |

Выход данных |

|

13 |

D4 |

Вход данных |

|

14 |

D5 |

Вход данных |

|

15 |

Q5 |

Выход данных |

|

16 |

Q6 |

Выход данных |

|

17 |

D6 |

Вход данных |

|

18 |

D7 |

Вход данных |

|

19 |

Q7 |

Выход данных |

|

20 |

PWR |

Напряжение питания (Диапазон напряжений питания 3.3В ± 0.3В , 5В ± 0.5В) |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.