На рисунках 15-19 измерены значения режимных параметров моделируемого узла.

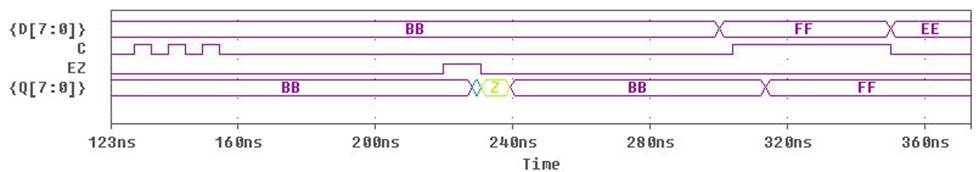

Рис.14 Предельные режимы работы проектируемого узла

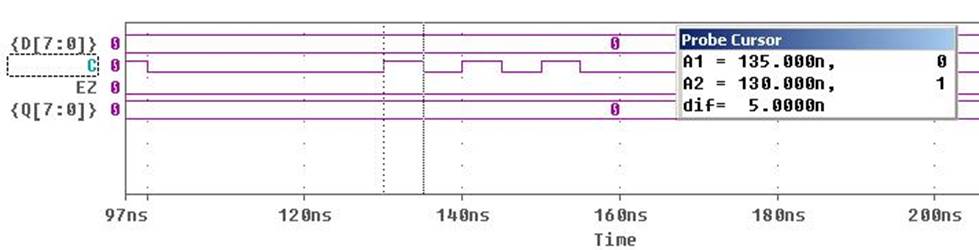

Рис.15 Минимальная длительность уровня лог. единицы на входе С

Рис.16 Минимальная длительность уровня лог. нуля на входе С

Таким образом, максимальная разрешенная частота синхросигнала, подаваемого на вход С, будет равна Fmax = 1/(Twhmn+Twlmn) = 1/(5ns + 5ns) = 100МГц.

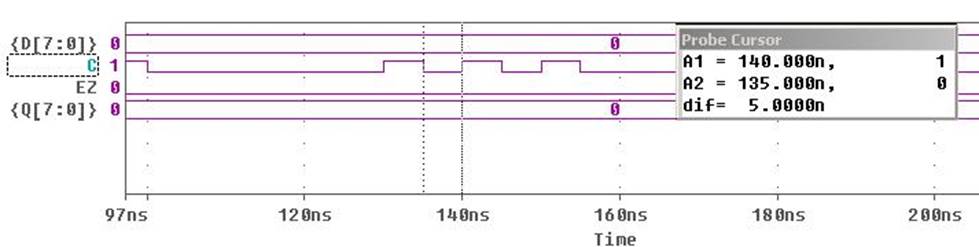

Рис.17 Минимальная длительность воспринимаемого импульса на входе EZ

При длительности импульса на входе EZ, меньше чем 11ns задержка переключения выходов Q (см. таблицу 3) из состояния логической единицы в высокоэмпедансное состояние становится больше, чем время присутствия самого импульса, а следовательно не все выходы успеют переключиться (только те, которые были в состоянии логического нуля). Таким образом, все выходы регистра перейдут в третье состояния только после прошествии 11ns после поступления сигнала запета.

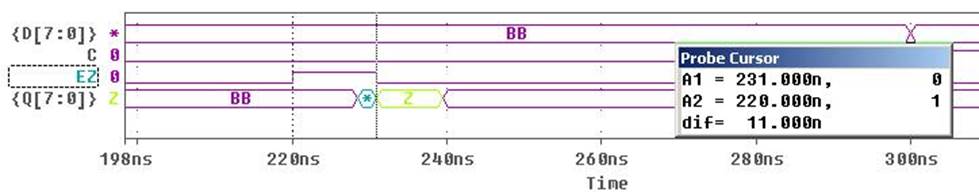

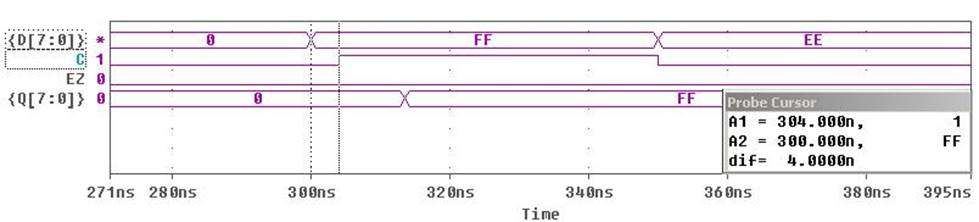

Рис.18 Минимальное время предустановки входов D относительно С

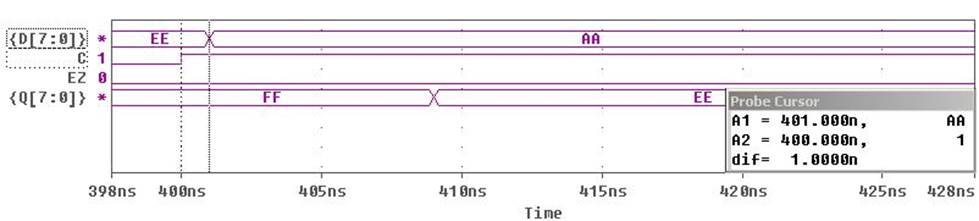

Рис.19 Минимальное время удержания входов D относительно С

Для надежного захвата данных со входов D, сигналы должны быть предустановленны минимум за 4нс до поступления фронта на вход C и удерживаться еще минимум 1нс после.

3.7. Функциональное описание моделируемого узла с помощью примитивов LOGICEXP, PINDLY и CONSTRAINT

*

.SUBCKT KR1554IR23_MM D0 D1 D2 D3 D4 D5 D6 D7 C EZ Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

U1 dff(8) DPWR DGND ;Встроенная модель D-триггера на 8 входов

+$D_HI $D_HI C

+D0 D1 D2 D3 D4 D5 D6 D7

+DD0 DD1 DD2 DD3 DD4 DD5 DD6 DD7

+$D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC

+D0_EFF IO_STD

*

U2 LOGICEXP(10,10) ;Блок логики моделируемого узла

+ DPWR DGND ;Контакты питания и земли

+ DD0 DD1 DD2 DD3 DD4 DD5 DD6 DD7 C EZ ;Входные сигналы логического блока

+ iC iEZ iQ0 iQ1 iQ2 iQ3 iQ4 iQ5 iQ6 iQ7 ;Выходные сигналы логического блока

+ D_KR1554IR23_MM IO_STD IO_LEVEL={IO_LEVEL}

+ LOGIC: ;Логическая секция

+iC={C} ;Прямая трансляция входных данных

+ iEZ={EZ} ;Прямая трансляция входных данных

+ iQ0={DD0} ;Прямая трансляция входных данных

+ iQ1={DD1} ;Прямая трансляция входных данных

+ iQ2={DD2} ;Прямая трансляция входных данных

+ iQ3={DD3} ;Прямая трансляция входных данных

+ iQ4={DD4} ;Прямая трансляция входных данных

+ iQ5={DD5} ;Прямая трансляция входных данных

+ iQ6={DD6} ;Прямая трансляция входных данных

+ iQ7={DD7} ;Прямая трансляция входных данных

*

U3 PINDLY (8,1,2) ;Начало блока задержек имеет восемь путей для которых вычисляется задержка

+ ;один сигнал разрешения и два внутренних сигнала

+ DPWR DDGND

+ iQ0 iQ1 iQ2 iQ3 iQ4 iQ5 iQ6 iQ7 ;Сигналы для которых вводим задержки

+ iEZ ;Сигнал разрешения выходных сигналов

+ iC iEZ ;Внутренние переменные (от которых отсчитываются задержки)

+ Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 ;Выходные сигналы макромодели

+ IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+ BOOLEAN: ;Секция объявления дополнительных переменных

+ Cfront = { CHANGED_LH(iC,0) } ;Переменная принимает значение логической единицы при

+ ;обнаружении фронта сигнала iC

+ TRISTATE: ;Секция контроля выходов

+ ENABLE LO=iEZ ;Сигнал iEZ разрешает выходы имея состояние логического нуля

+ ; и переводит в состояние высокого импеданса при логической единице

+ Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7={

+ CASE(

+ CHANGED(iEZ,0) & TRN_Z$, DELAY(-1, 1ns, 8.5ns), ;Задержка переключения из Z в любое

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.