|

Обозна- чение |

Параметр |

PWR (питание), В |

T=25ºC |

T=-45+85ºC |

Ед. изм. |

|

Min |

Max |

||||

|

tPHL |

Время задержки распространения сигнала при выключении от входа С к выходам Q. |

3.0 4.5 |

12.5 9.0 |

14.0 10.0 |

нс |

|

tPLH |

Время задержки распространения сигнала при включении от входа С к выходам Q. |

3.0 4.5 |

13.5 9.5 |

15.5 10.5 |

нс |

|

tPZL |

Время задержки распространения сигнала при переходе из состояния высокого импеданса в состояние низкого уровня. |

3.0 4.5 |

11.5 8.5 |

13.0 9.5 |

нс |

|

tPLZ |

Время задержки распространения сигнала при переходе из состояния низкого уровня в состояние высокого импеданса от входа EZ к выходам Q |

3.0 4.5 |

11.5 8.5 |

12.5 10.0 |

нс |

|

tPZH |

Время задержки распространения сигнала при переходе из состояния высокого импеданса в состояние высокого уровня от входа EZ к выходам Q. |

3.0 4.5 |

11.5 8.5 |

13.0 9.5 |

нс |

|

tPHZ |

Время задержки распространения сигнала при переходе из состояния высокого уровня в состояние высокого импеданса от входа EZ к выходам Q. |

3.0 4.5 |

12.5 11.0 |

14.5 12.5 |

нс |

|

tSU |

Время предустановки входов D относительно входа C |

3.0 4.5 |

5.5 4.0 |

6.0 4.5 |

нс |

|

tH |

Время удержания входов D относительно входа C |

3.0 4.5 |

1.0 1.0 |

0 0 |

нс |

|

FMAX |

Максимальная тактовая частота |

3.0 4.5 |

60 100 |

МГц |

|

3. Моделирование узла в пакете DesignLab_8

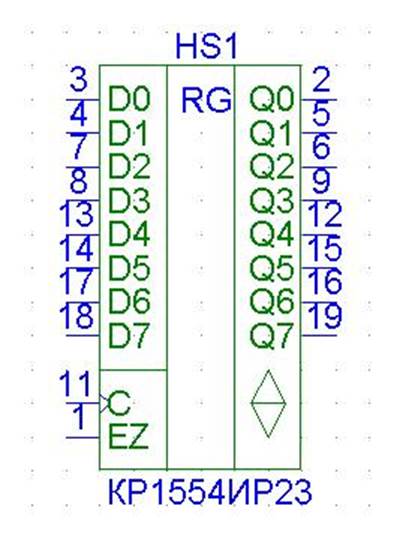

3.1. Условное графическое изображение моделируемого узла в виде иерархического символа

На рисунке 4 приведен иерархический символ моделируемого узла.

Рис. 4 УГО моделируемого узла в виде иерархического символа

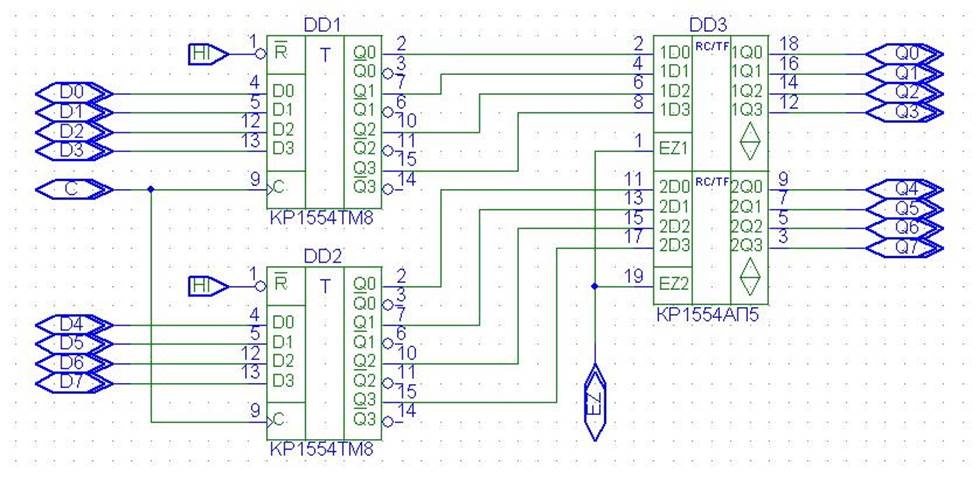

3.2. Схема замещения моделируемого узла

Схема замещения выполнена на элементной базе серии КР1554: КР1554ТМ8 – четыре D-триггера с общим выводом асинхронного сброса и синхронизации; КР1554АП5 – два четырехразрядных формирователя (буфера) с тремя состояниями на выходе. На рисунке 5 представлена полученная схема замещения.

Рис. 5 Схема замещения моделируемого узла

Динамические характеристики элементов подобраны (изменены) так, чтобы в сумме давали задержки соответствующие заданным для моделируемого узла.

3.3. Текстовое SPICE-описание моделируемого узла

3.3.1. Содержимое файла HS_Schem_2.cir

* D:\NSTU\Modelir\KURS\Design_Lab_8\HS_Schem_2.sch

* Schematics Version 8.0 - July 1997

* Sat Nov 05 17:13:39 2005

** Analysis setup **

.tran 20ns 2200ns

.OPTIONS DIGMNTYMX=3

.LIB "D:\NSTU\Modelir\KURS\Design_Lab_8\KR1554TM8.mod"

.LIB "D:\NSTU\Modelir\KURS\Design_Lab_8\KR1554AP5.mod"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "nom.lib"

.INC "HS_Schem_2.net"

.INC "HS_Schem_2.als"

.probe

.END

3.3.2. Содержимое файла HS_Schem_2.net

* Schematics Netlist *

X_HS1_DD1 $D_HI C D0 D1 D2 D3 $N_0001 $N_0003 $N_0005 $N_0007 $N_0002

+ $N_0004 $N_0006 $N_0008 $G_DPWR $G_DGND KR1554TM8 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD2 $D_HI C D4 D5 D6 D7 $N_0010 $N_0012 $N_0014 $N_0016 $N_0011

+ $N_0013 $N_0015 $N_0017 $G_DPWR $G_DGND KR1554TM8 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD3 $N_0001 $N_0003 $N_0005 $N_0007 $N_0010 $N_0012 $N_0014

+ $N_0016 EZ EZ Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 $G_DPWR $G_DGND KR1554AP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

U_DSTM1 STIM(8,44)

+ $G_DPWR $G_DGND

+ D7 D6 D5 D4 D3 D2 D1 D0

+ IO_STM

+ IO_LEVEL=0

+ TIMESTEP=100ns

+ 0c 00

+ 3c FF

+ 6c 2E

+ 9c AA

+ 16c BB

U_DSTM2 STIM(1,1)

+ $G_DPWR $G_DGND

+ C

+ IO_STM

+ IO_LEVEL=0

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.