+ 0s 0

+ 100ns 1

+ repeat 2 times

+ +100ns 0

+ +200ns 1

+ endrepeat

+ +100ns 0

+ +600ns 1

+ +100ns 0

+ +300ns 1

+ +100ns 0

U_DSTM3 STIM(1,1)

+ $G_DPWR $G_DGND

+ EZ

+ IO_STM

+ IO_LEVEL=0

+ 0s 0

+ 1us 1

+ 1.2us 0

+ 1.7us 1

+ 2us 0

3.4. Описание диаграмм входных сигналов

Для задания входных воздействий на моделируемый узел были использованы генераторы STIM1 (для задания одиночных сигналов C и EZ) и STIM8 (для задания восьмиразрядного шинного сигнала). Текстовое описание генерируемых сигналов находится в net файле, содержимое которого приведено выше.

3.5. Тестирование разработанных моделей

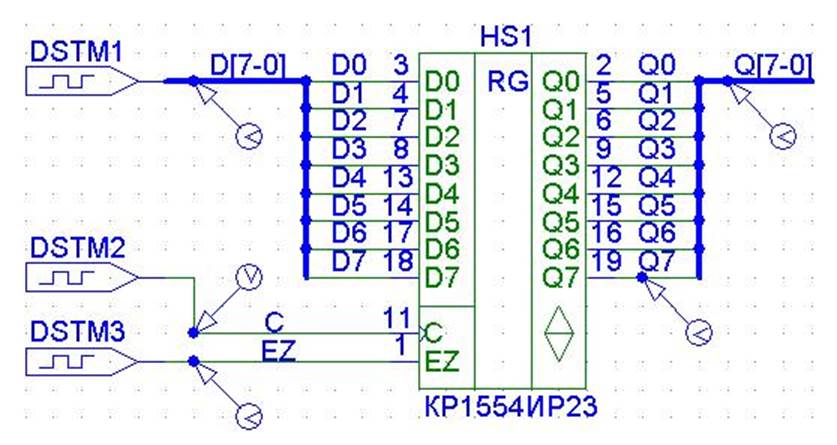

На рисунке 6 представлена схема тестирования полученной модели. Испытания проводятся для максимальных задержек. Сравнение производится с максимальными задержками, указанными в таблице 3 для входной емкости Сl=50пФ и температуры окружающей среды T=25ºC. Напряжение питания VCC=5В.

Рис.6 Схема верификации иерархического символа с внутренним представлением в виде принципиальной схемы замещения

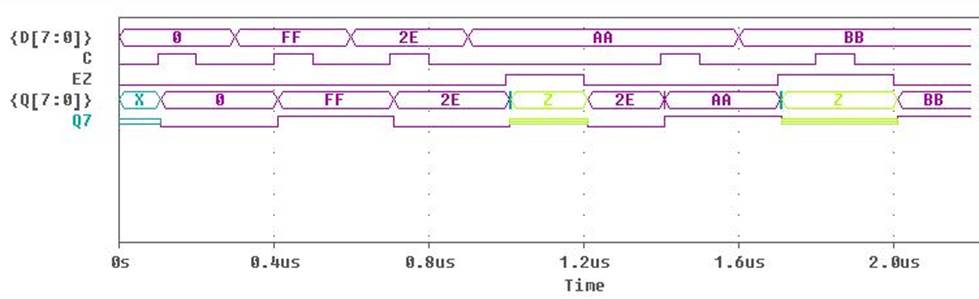

Входные воздействия заданы так, чтобы показать все возможные режимы работы узла и соответствующие этим режимам задержки. На рисунке 7 представлена тестовая диаграмма.

Рис.7 Диаграмма тестирования разработанной модели

В начальный момент времени состояние триггеров не определено. При поступлении первого синхроимпульса происходит захват данных с шины D. При смене сигналов на входах Di их значения не передаются на выход. Только при поступлении фронта синхросигнала спустя задержку прохождения через триггеры и выходные буферы сигналы поступают на выходы узла. При поступлении высокого уровня на вход EZ спустя задержку переключения буферов выходы переводятся в высокоимпедансное состояние. При этом, после снятия высокого уровня со входа EZ спустя задержку переключения буферов, на выходах узла появятся данные, хранимые в D-триггерах. На следующем промежутке времени, где EZ принимает значение логической единицы, на вход C поступает фронт, и триггеры захватывают новые данные с шины D. После снятия высокоимпедансного состояния на выходах появятся уже новые данные.

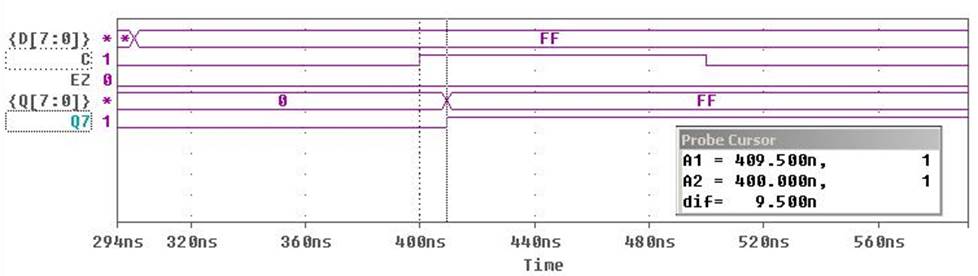

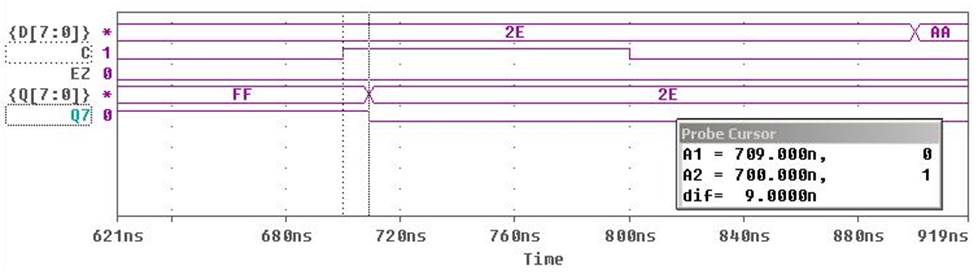

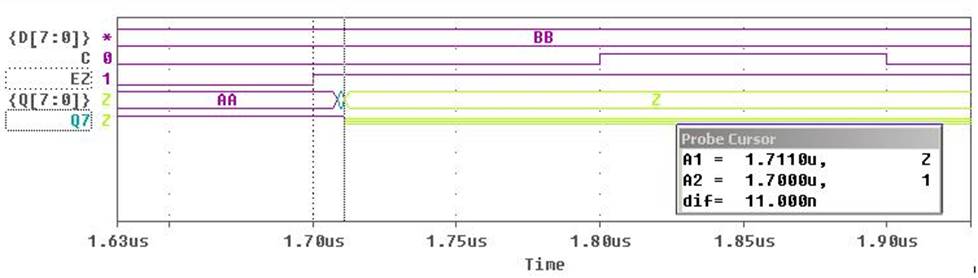

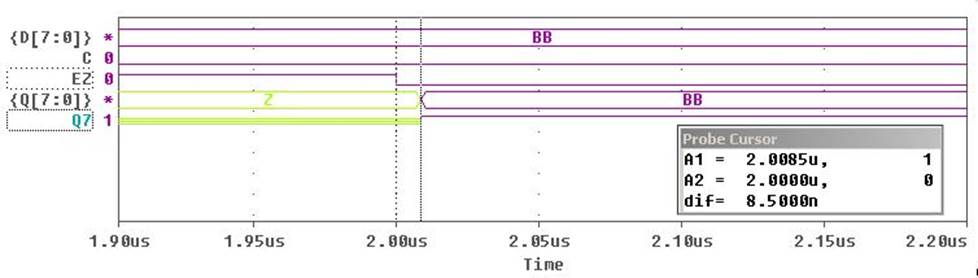

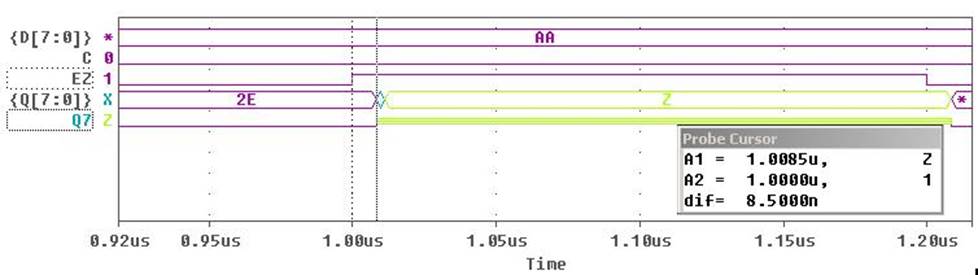

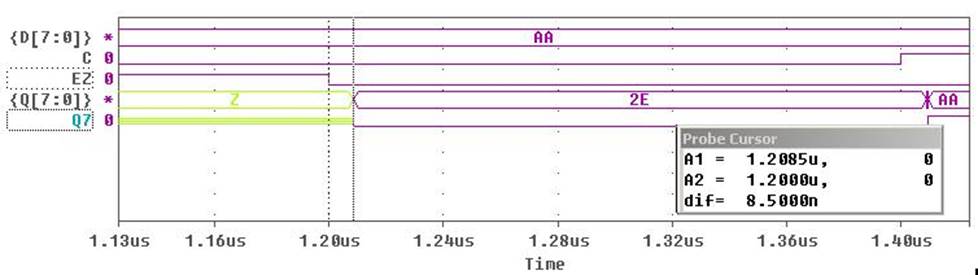

На рисунках 8-13 приведены результаты изменения динамических характеристик имитируемых моделью узла.

Рис.8 Время задержки распространения сигнала при включении от входа С к выходам Q

Рис.9 Время задержки распространения сигнала при выключении от входа С к выходам Q

Рис.10 Время задержки распространения сигнала при переходе из состояния высокого уровня в состояние высокого импеданса от входа EZ к выходам Q

Рис.11 Время задержки распространения сигнала при переходе из состояния высокого импеданса в состояние высокого уровня от входа EZ к выходам Q

Рис.12 Время задержки распространения сигнала при переходе из состояния низкого уровня в состояние высокого импеданса от входа EZ к выходам Q

Рис.13 Время задержки распространения сигнала при переходе из состояния высокого импеданса в состояние низкого уровня

По проведенным измерениям видно, что разработанная модель адекватно имитирует работу узла во всех режимах, с соответствующими временными задержками.

3.6. Оценка предельных скоростных возможностей исследуемого узла

Исследуемый узел содержит элементы памяти (построен на D-триггерах), соответственно должен иметь ограничение на максимальную тактовую частоту сигнала, подаваемого на вход С. Так как входы данных синхронизированы – захват данных происходит только по фронту синхросигнала, то имеет смысл говорить только о режимных параметрах, таких как предустановка и удержание данных на входах Di относительно фронта синхросигнала.

Вход EZ является асинхронным и для него можно определить длительность минимального импульса, под воздействием которого выходы успеют переключиться в высокоимпедансное состояние.

На рисунке 14 приведена диаграмма моделирования предельных режимов работы уза (максимальная тактовая частота, минимальное время предустановки входов D относительно C, минимальное время удержания сигналов на входах D и минимальный воспринимаемый импульс на входе EZ).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.