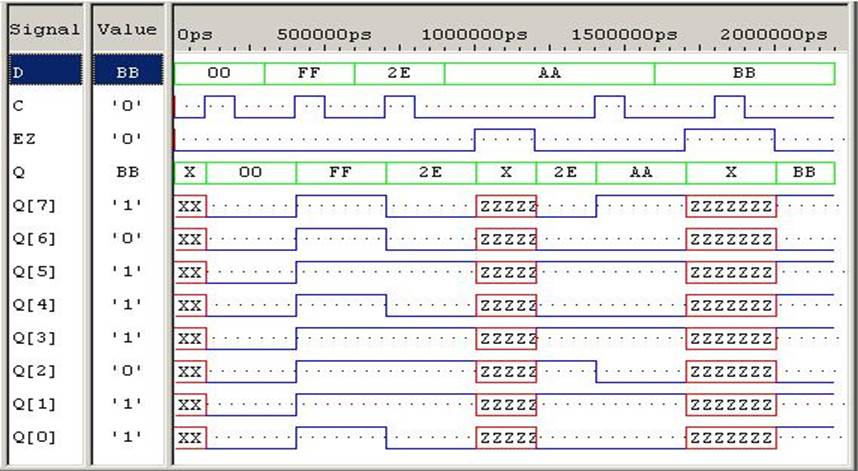

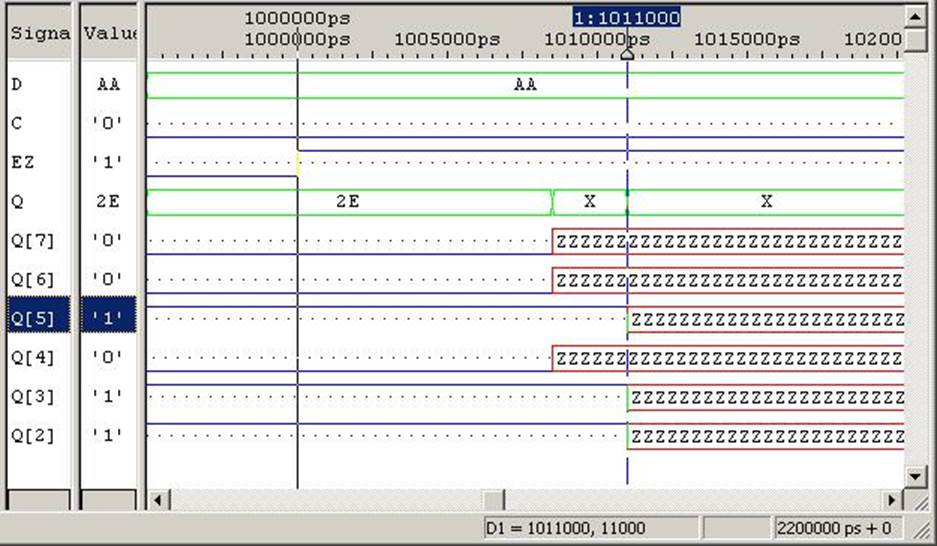

Рис.25 Диаграмма тестирования работы иерархического символа с внутренним описанием представленным в виде принципиальной схемы замещения

Необходимо отметить выявленную особенность моделирования: по приведенной диаграмме видно, что моделирование производится не в наносекундах, а в пикосекундах. Причина – при моделировании в наносекундах (режим задается в Options/Project) происходит округление дробной части задержки, что приводит к большой погрешности (задержка величиной 8.5ns приравнивается к 9ns). Так как в моделируемом узле присутствуют дробные задержки, то моделирование проводилось с меньшим шагом (в пикосекундах).

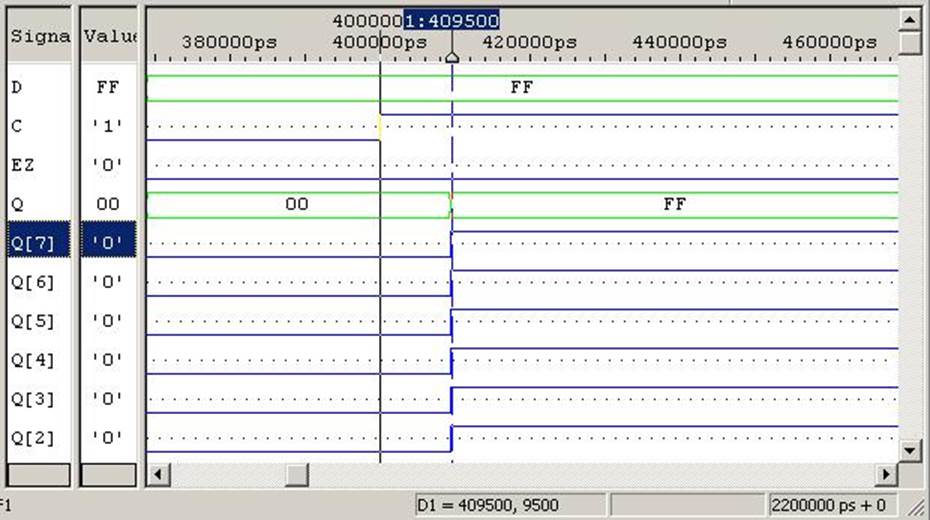

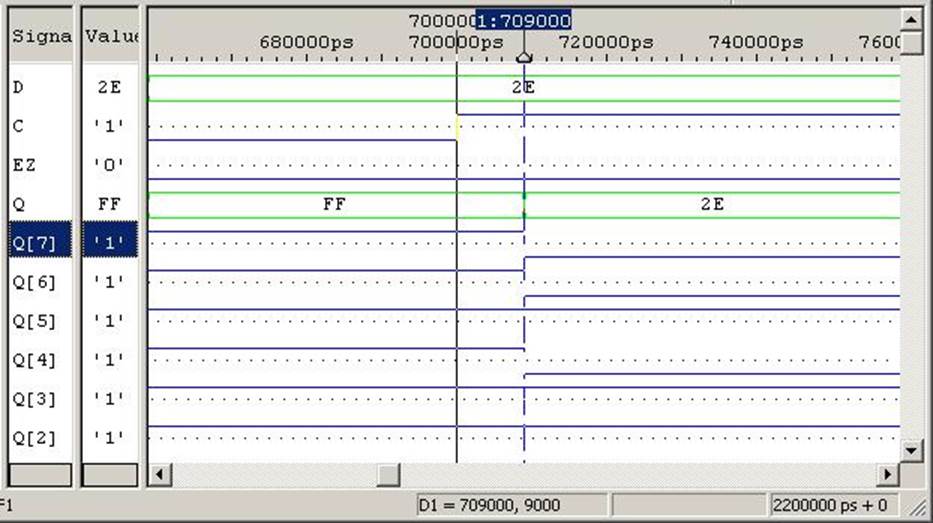

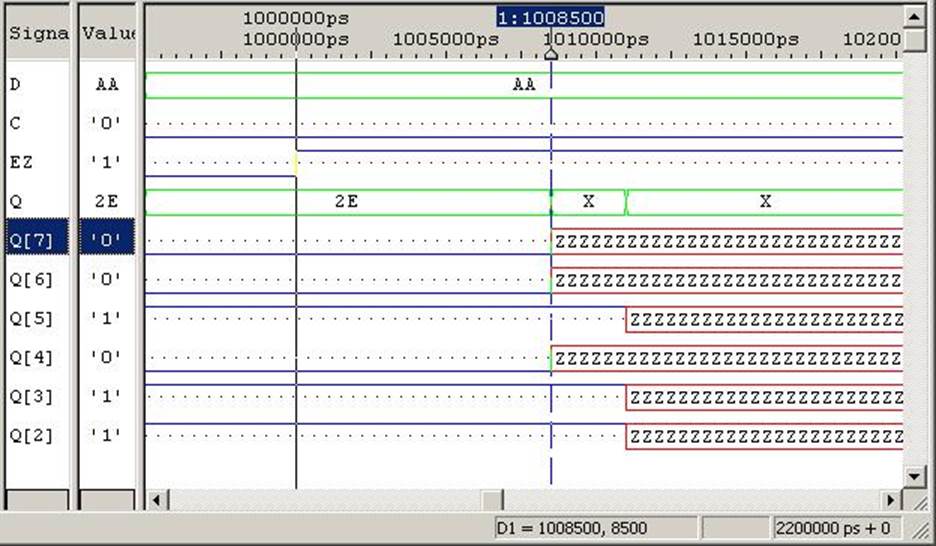

Тесовый эксперимент идентичен проведенному в пакете DesignLab_8 и описанному в пункте 3.5. На рисунках 26-30 приведены результаты изменения динамических характеристик воспроизводимых моделью узла.

Рис.26 Время задержки распространения сигнала при включении от входа С к выходам Q

Рис.27 Время задержки распространения сигнала при выключении от входа С к выходам Q

Рис.28 Время задержки распространения сигнала при переходе из состояния логического нуля в состояние высокого импеданса от входа EZ к выходам Q

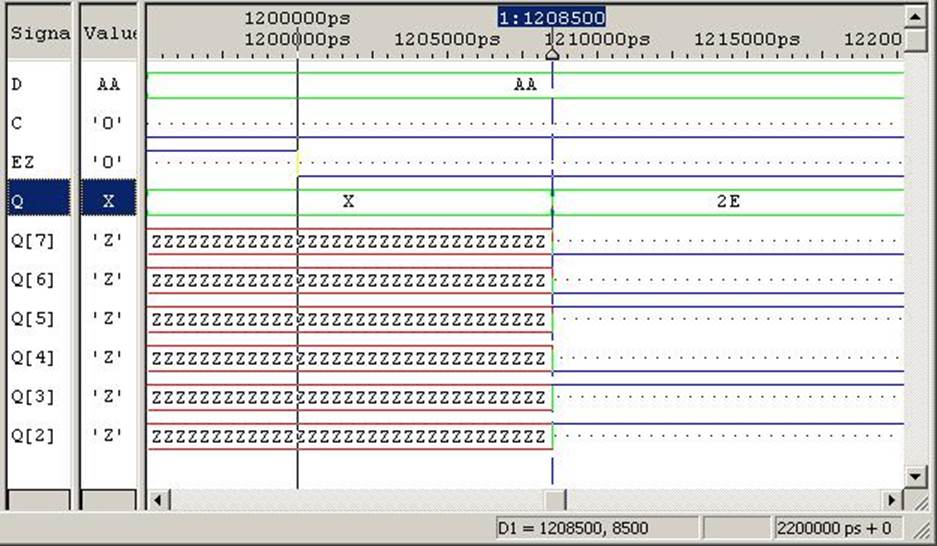

Рис.29 Время задержки распространения сигнала при переходе из состояния логической единицы в состояние высокого импеданса от входа EZ к выходам Q

Рис.30 Время задержки распространения сигнала при переходе из состояния высокого импеданса в состояние низкого или высокого уровня от входа EZ к выходам Q

Проведенные измерения показывают, что модель адекватно воспроизводит все временные задержки прохождения сигналов заданные в соответствии с динамическими характеристиками реальной ИМС.

4.4. Поведенческая VHDL-модель узла

Разработанная VHDL-модель узла отображает временные задержки распространения сигналов от входов ИМС к ее выходам для всех возможных режимов работы. Временные характеристики соответствуют режиму работы: температура окружающей среды T=25ºC. Напряжение питания VCC=5В. Входная емкость Сl=50пФ.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY KR1554IR23_VHDL IS PORT(--Описание входных и выходных контактов символа

D0 : IN std_logic;

D1 : IN std_logic;

D2 : IN std_logic;

D3 : IN std_logic;

D4 : IN std_logic;

D5 : IN std_logic;

D6 : IN std_logic;

D7 : IN std_logic;

C : IN std_logic;

EZ : IN std_logic;

Q0 : OUT std_logic;

Q1 : OUT std_logic;

Q2 : OUT std_logic;

Q3 : OUT std_logic;

Q4 : OUT std_logic;

Q5 : OUT std_logic;

Q6 : OUT std_logic;

Q7 : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END KR1554IR23_VHDL;

ARCHITECTURE model OF KR1554IR23_VHDL IS—Тело поведенческой модели

BEGIN

PROCESS(D0, D1, D2, D3, D4, D5, D6, D7, C, EZ)

variable iQ0 : std_logic;--Дополнительные переменные для хранения данных

variable iQ1 : std_logic;--на выходах триггеров (внутри регистра), а не на

variable iQ2 : std_logic;--выходах буферов

variable iQ3 : std_logic;

variable iQ4 : std_logic;

variable iQ5 : std_logic;

variable iQ6 : std_logic;

variable iQ7 : std_logic;

BEGIN

IF C='1' AND C'EVENT

THEN—Если поступил фронт синхросигнала

iQ0:=D0;--Триггеры захватывают данные в любом случае

iQ1:=D1;

iQ2:=D2;

iQ3:=D3;

iQ4:=D4;

iQ5:=D5;

iQ6:=D6;

iQ7:=D7;

IF EZ='0'

THEN—-Если выходные буферы открыты то сигналы появляются на выходах

--спустя задержку распространения, которая будет разной для перехода

--из 0 в 1 и из 1 в 0

IF D0='1' THEN Q0<='1' AFTER 9.5ns; ELSE Q0<='0' AFTER 9ns; END IF;

IF D1='1' THEN Q1<='1' AFTER 9.5ns; ELSE Q1<='0' AFTER 9ns; END IF;

IF D2='1' THEN Q2<='1' AFTER 9.5ns; ELSE Q2<='0' AFTER 9ns; END IF;

IF D3='1' THEN Q3<='1' AFTER 9.5ns; ELSE Q3<='0' AFTER 9ns; END IF;

IF D4='1' THEN Q4<='1' AFTER 9.5ns; ELSE Q4<='0' AFTER 9ns; END IF;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.