Министерство образования и науки Российской Федерации

Новосибирский государственный технический университет

Кафедра вычислительной техники

Курсовая работа

по дисциплине «Моделирование»

Проектирование цифрового узла 155КП1

Факультет: АВТ Преподаватель:

Группа: АМ-710 Шалагинов А.В.

Студент: Малахов С.А.

Новосибирск, 2010

Общее задание:

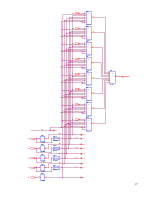

Спроектировать схему замещения цифрового узла, представляющего собой существующую микросхему в пакетах OrCad 9.1 (SPICE и PСB Simulate проекты), Active-HDL 8.1. Создать поведенческую модель исследуемого цифрового узла на языке VHDL. Провести верификацию разработанной схемы, целью которых является подтверждение работоспособности узла на всех режимах работы и проверка на соответствие его временных задержек требуемым.

Индивидуальное задание:

Разработать 16-разрядный инверсный мультиплексор со стробом КП1: зарубежный аналог - 150. Реальный элемент 155КП1 разрабатывается на базе серии 155: зарубежный аналог – SN74150, на базе серии SN74.

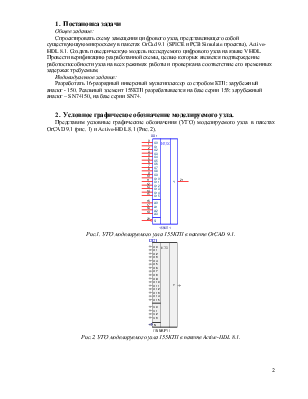

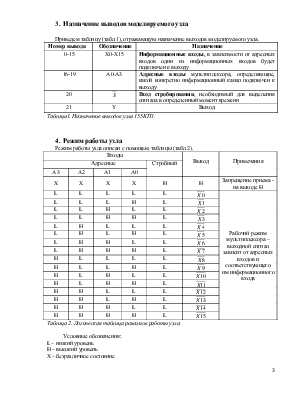

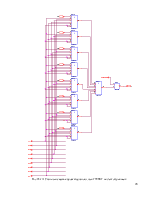

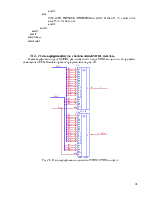

Представим условные графические обозначения (УГО) моделируемого узла в пакетах OrCAD 9.1 (рис. 1) и Active-HDL 8.1 (Рис. 2).

Рис.1. УГО моделируемого узла 155КП1 в пакете OrCAD 9.1.

Рис.2. УГО моделируемого узла 155КП1 в пакете Active-HDL 8.1.

Приведем таблицу (табл.1), отражающую назначение выходов моделируемого узла.

|

Номер вывода |

Обозначение |

Назначение |

|

|

0-15 |

X0-X15 |

Информационные входы, в зависимости от адресных входов один из информационных входов будет подключен к выходу |

|

|

16-19 |

A0-A3 |

Адресные входы мультиплексора, определяющие, какой конкретно информационный канал подключен к выходу |

|

|

20 |

|

Вход стробирования, необходимый для выделения сигнала в определенный момент времени |

|

|

21 |

Y |

Выход |

|

Таблица1. Назначение выводов узла 155КП1.

Режим работы узла описан с помощью таблицы (табл.2).

|

Входы |

Выход |

Примечания |

||||

|

Адресные |

Стробный |

|||||

|

A3 |

A2 |

A1 |

A0 |

|||

|

X |

X |

X |

X |

H |

H |

Запрещение приема - на выходе H |

|

L |

L |

L |

L |

L |

|

Рабочий режим мультиплексора – выходной сигнал зависит от адресных входов и соответствующего им информационного входа |

|

L |

L |

L |

H |

L |

|

|

|

L |

L |

H |

L |

L |

|

|

|

L |

L |

H |

H |

L |

|

|

|

L |

H |

L |

L |

L |

|

|

|

L |

H |

L |

H |

L |

|

|

|

L |

H |

H |

L |

L |

|

|

|

L |

H |

H |

H |

L |

|

|

|

H |

L |

L |

L |

L |

|

|

|

H |

L |

L |

H |

L |

|

|

|

H |

L |

H |

L |

L |

|

|

|

H |

L |

H |

H |

L |

|

|

|

H |

H |

L |

L |

L |

|

|

|

H |

H |

L |

H |

L |

|

|

|

H |

H |

H |

L |

L |

|

|

|

H |

H |

H |

H |

L |

|

|

Таблица 2. Логическая таблица режимов работы узла.

Условные обозначения:

L – низкий уровень

H – высокий уровень

X – безразличное состояние

![]() –

инверсные информационные входы

–

инверсные информационные входы

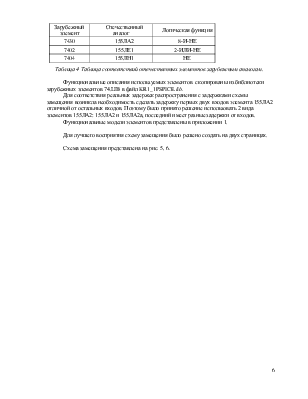

Приведем таблицу (табл. 3) с информацией о задержках для элемента 155КП1, аналога SN74150, построенную на основе соответствующей документации [источник 1].

|

Параметр |

От входа |

MAX |

UNIT |

|

tPLH |

X0-X15 |

14 |

ns |

|

tPHL |

20 |

ns |

|

|

tPLH |

A0-A3 |

35 |

ns |

|

tPHL |

33 |

ns |

|

|

tPLH |

|

24 |

ns |

|

tPHL |

30 |

ns |

Таблица 3. Задержки для элемента 155КП1.

Микросхема 155КП1 представляет собой 16-разрядный инверсный мультиплексор со стробированием. Мультиплексор позволяет передать инверсию сигнала с одного из входов на выход; при этом выбор входа осуществляется подачей соответствующей комбинации управляющих сигналов на адресные входы.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.