Вход стробирования необходим для выделения сигнала в определенный момент времени (при высоком уровне на выходе Y всегда 1, вне зависимости от остальных входов; при низком уровне мультиплексор работает в обычном режиме).

Вход стробирования предназначен для выделения информационного сигнала, во избежание влияния помех. На входы А0, А1, А2, A3 подается код, определяющий номер информационного входа (X), который будет передан на выход (Y). Н.п.: Если двоичный код A3 A2 A1 A0 образует число 13, то на выход будет передан сигнал с X13.

Условное графическое изображение проектируемого узла в виде иерархического символа представлено на Рис.3.

Рис.3. УГО моделируемого узла 155КП1 в виде иерархического символа.

В соответствии с отечественными УГО по ЕСКД создана схема замещения проектируемого узла на базе собственных элементов (Рис. 4).

Так как библиотеки пакета Orcad 9.1 не содержат необходимых элементов серии SN было решено за аналоги взять элементы серии 74, по временным характеристикам идентичной SN74. Элементы созданы путем модификации элементов серии 74 и сохранены в библиотеке kr1_1PSPICE.olb. Соответствия элементов серии 74 элементам серии 155 приведены в таблице 6.

Рис.4. УГО символов, спроектированных для реализации схемы замещения цифрового автомата.

|

Зарубежный элемент |

Отечественный аналог |

Логическая функция |

|

7430 |

155ЛА2 |

8-И-НЕ |

|

7402 |

155ЛЕ1 |

2-ИЛИ-НЕ |

|

7404 |

155ЛН1 |

НЕ |

Таблица 4 Таблица соответствий отечественных элементов зарубежным аналогам.

Функциональные описания используемых элементов скопированы из библиотеки зарубежных элементов 74.LIB в файл KR1_1PSPICE.lib.

Для соответствия реальных задержек распространения с задержками схемы замещения возникла необходимость сделать задержку первых двух входов элемента 155ЛА2 отличной от остальных входов. Поэтому было принято решение использовать 2 вида элементов 155ЛА2: 155ЛА2 и 155ЛА2а, последний имеет разные задержки от входов.

Функциональные модели элементов представлены в приложении 1.

Для лучшего восприятия схему замещения было решено создать на двух страницах.

Схема замещения представлена на рис. 5, 6.

Рис.5,6. Схема замещения проектируемого узла 155КП1 на двух страницах.

Схема верификации узла 155КП1 показана на рис. 7. Для большей наглядности маркеры напряжения не показаны.

Рис.7. Схема верификации проектируемого узла 155КП1.

Верификация узла проводилась для максимальных задержек.

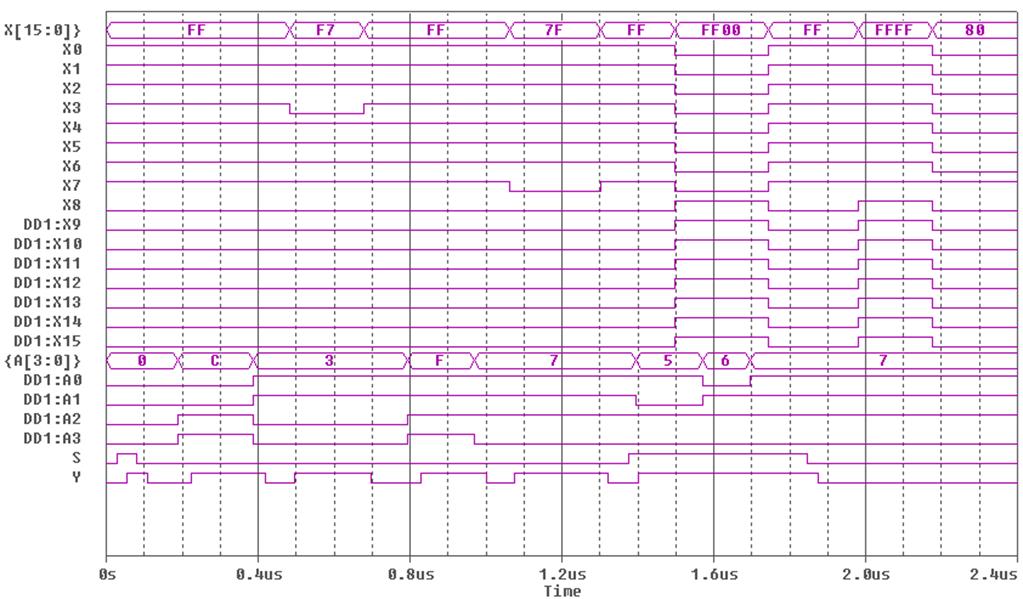

Результаты моделирования узла во всех режимах работы показаны на рис. 8.

Рабочий режим Рабочий режим

Прием данных

запрещен

Рис.8. Временная диаграмма работы проектируемого узла

Полученная временная диаграмма отражает все режимы работы проектируемого узла. Задержки распространения от входов к выходу, совпадают с реальными (см. таблицу 3).

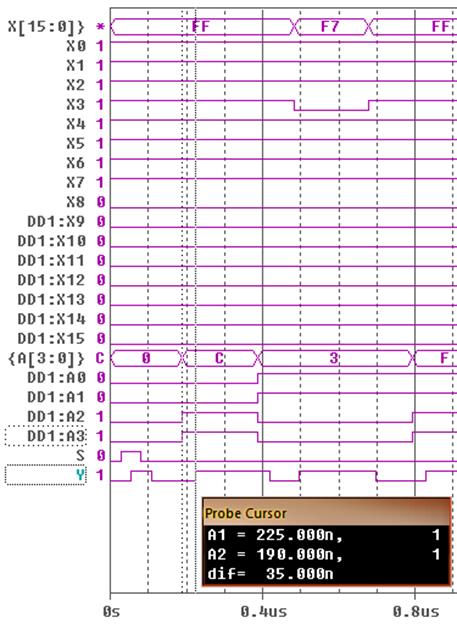

Для того чтобы убедиться в том что задержки подобраны верно, рассмотрены временнее диаграммы моделируемого узла (рис.9-14).

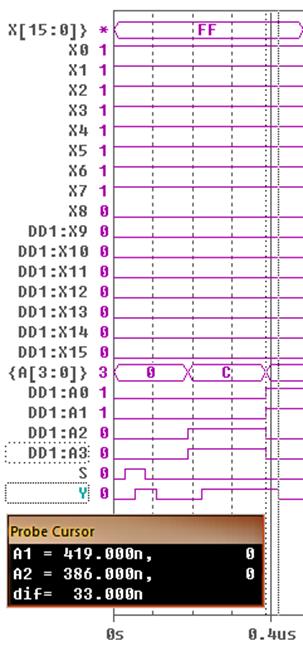

Рис.9. Задержка распространения сигнала от адресного входа до выхода при переключении входа из 0 в 1 (tPLH =35 нс).

Рис.10. Задержка распространения сигнала от адресного входа до выхода при переключении входа из 1 в 0 (tPHL =33 нс).

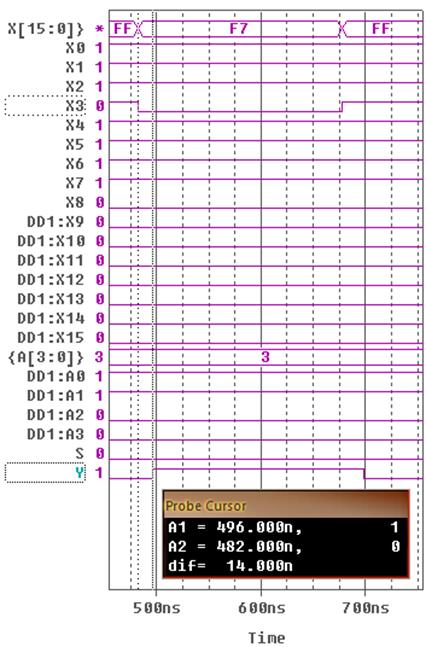

Рис.11. Задержка распространения сигнала от информационного входа до выхода при переключении входа из 0 в 1 (tPLH =14 нс).

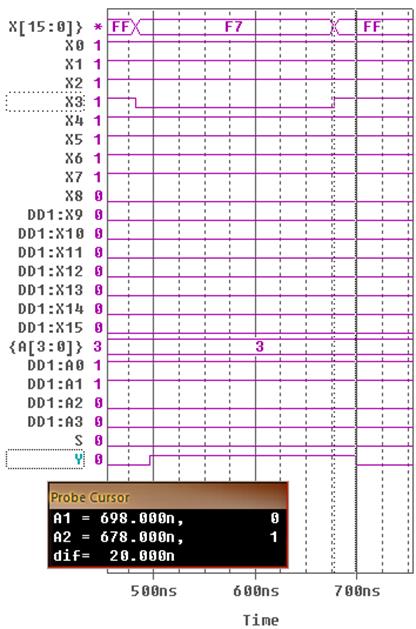

Рис.12. Задержка распространения сигнала от информационного входа до выхода при переключении входа из 1 в 0 (tPHL=20 нс).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.