Также в проектах по-разному задаются входные воздействия. PSPICE-проект в этом плане удобнее: сигналы можно изменять и задавать “кликом” по диаграмме. В PCB Simulate проекте нужно прописывать все сигналы вручную.

Задержки в PSPICE также удобней измерять – оба маркера привязаны к правой и левой кнопке мыши.

Поведенческая модель описывает все режимы работы проектируемого узла.

library IEEE;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.std_logic_unsigned.all;

entity \155KP1\ is

port( S,A0,A1,A2,A3,X0,X1,X2,X3,X4,X5,X6,X7,X8,X9,X10,X11,X12,X13,X14,X15

: in STD_LOGIC;--входы

Y : out STD_LOGIC); --выход

end \155KP1\;

architecture model of \155KP1\ is

begin

PROCESS (S,A0,A1,A2,A3,X0,X1,X2,X3,X4,X5,X6,X7,X8,X9,X10,X11,X12,X13,X14,X15)

--поведенческая модель - описание процессом

variable Xvar : std_logic_vector(15 downto 0);

--внутренняя переменная - виртуальная шина для информационных входов

variable Avar : std_logic_vector(3 downto 0);

--внутренняя переменная - виртуальная шина для адресных входов

BEGIN

Avar := A3&A2&A1&A0; -- конкатенация - объединение входов в шину

Xvar := X15&X14&X13&X12&X11&X10&X9&X8&X7&X6&X5&X4&X3&X2&X1&X0;

-- конкатенация - объединение входов в шину

if S='1' then Y<='1' after 24 ns; -- при стробирующем входе на Y всегда подается 1

else

if (X0'event or X1'event or X2'event or X3'event Or X4'event or X5'event or X6'event

or X7'event or X8'event or X9'event or X10'event or X11'event

or X12'event or X13'event or X14'event or X15'event) then

if(Xvar(TO_INTEGER (UNSIGNED(Avar))) ='0') then Y <= '1' after 14 ns;

elsif(Xvar(TO_INTEGER (UNSIGNED(Avar))) ='1') then Y <= '0' after 20 ns;

end if;

else

if (S'event) then

if(Xvar(TO_INTEGER (UNSIGNED(Avar))) ='0') then Y <= '1' after 30 ns;

else Y <= '0' after 30 ns;

end if;

else

if(Xvar(TO_INTEGER (UNSIGNED(Avar))) ='0') then Y <= '1' after 35 ns;

else Y <= '0' after 33 ns;

end if;

end if;

end if;

end if;

end process;

end model;

Схема верификации узла 155КП1, реализованного в виде VHDL модели и в виде схемы замещения в PCB-Simulate-проекте представлена на рис. 28.

Рис.28. Схема верификации элемента 155KП1 (VHDL-модель).

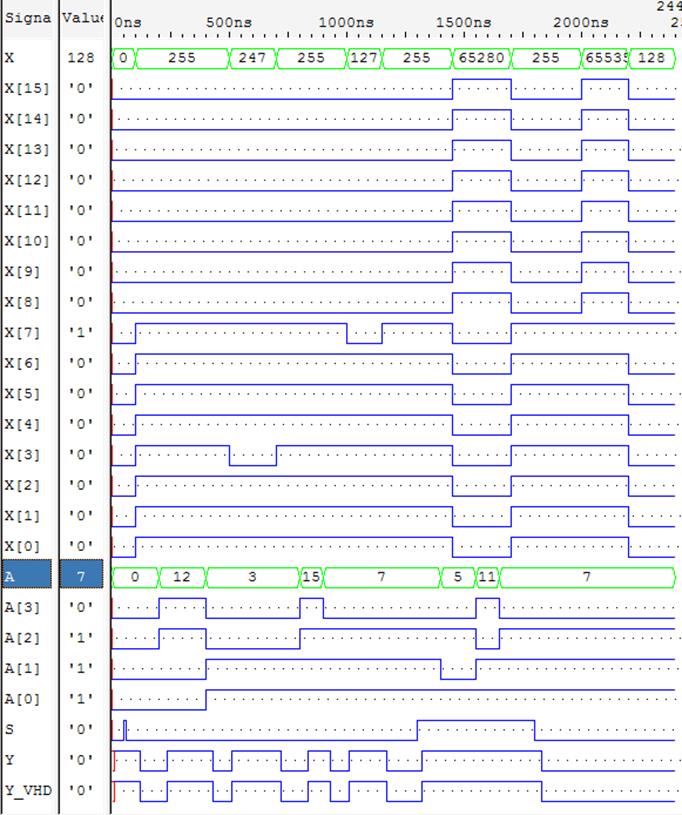

Режимы работы элемента в PCB Simulate – проекте полностью соответствуют режимам работы VHDL – модели (рис.29).

Для того чтобы убедиться в том, что задержки подобраны верно, рассмотрены временнее диаграммы моделируемого узла для проверки идентичности VHDL модели со схемой замещения из пункта 8 диаграммы показаны в одном окне.

Рис.29.Результат моделирования узла 155KП1 (VHDL-модель)

.

Как видно из рис.29 выходной сигнал VHDL-модели полностью соответствует выходному сигналу схемы замещения – с абсолютно теми же задержками.

Внешнее описание узла в виде графического изображения представлено на рис. 30.

.

.

Рис. 30. Внешнее описание макромодели узла — в виде графического изображения.

В схеме замещения используются элементы из таблицы 4, УГО элементов представлено на рисунке 31.

Рис. 31. УГО исользуемых элементов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.