Внутреннее описание макромодели узла в виде принципиальной схемы замещения представлено на рис. 32 и 33 (схема реализована на 2 страницах).

Рис. 32, 33. Внутренне описание макромодели узла — в виде принципиальной схемы замещения.

VHDL-модели элементов данной схемы аналогичны VHDL-моделям, использовавшимся в пакете OrCAD 9.1, и представлены в приложении 2.

Схема верификации иерархического символа представлена на рисунке 34.

Рис. 34. Схема верификации иерархического символа

![]()

![]()

![]()

![]()

![]()

Рабочий режим Прием данных Рабочий режим

запрещен

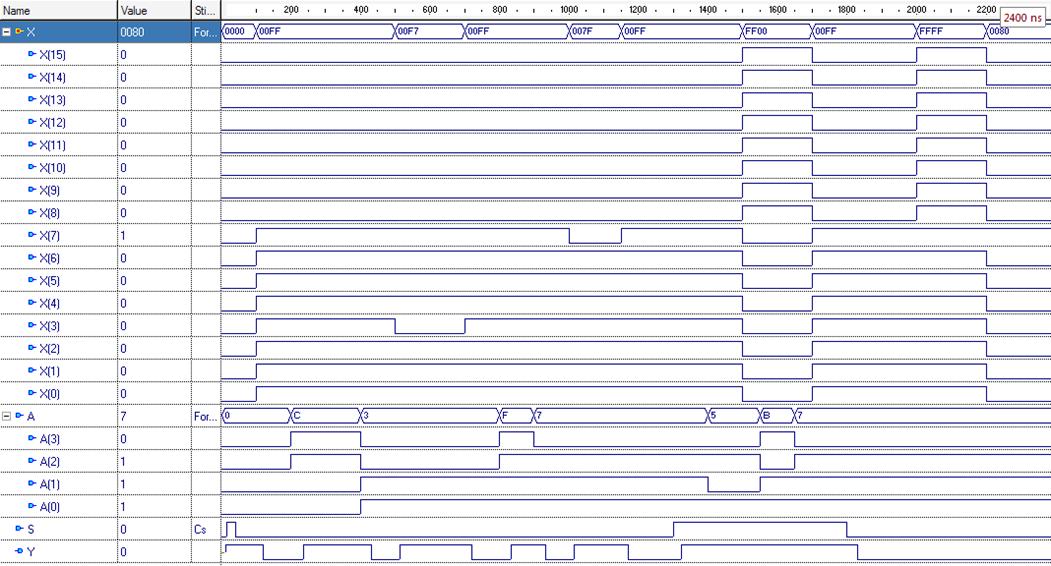

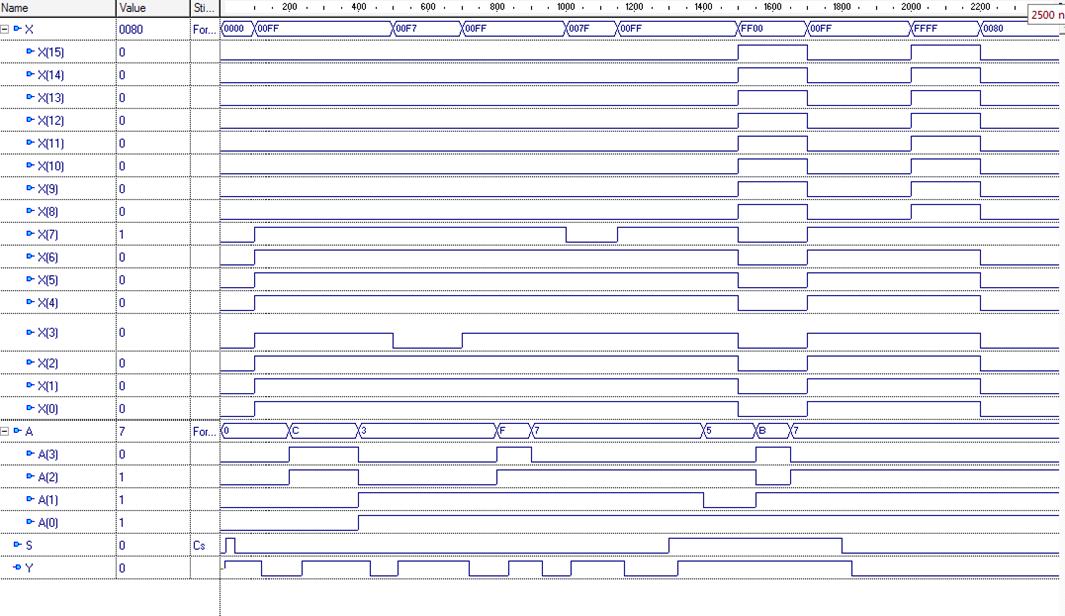

Рис.35. Результаты моделирования проектируемого узла.

Режимы работы проектируемого в Active-HDL 8.1. узла совпадают с режимами работы узла, проектируемого в пакете OrCad 9.1. Следовательно, спроектированный узел работает верно.

Проверим узел на соответствие реальным задержкам (рис. 36-42)

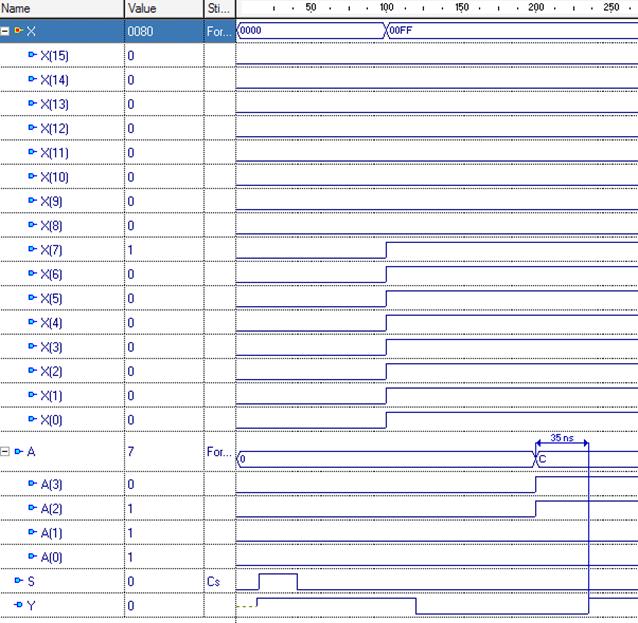

Рис.36. Задержка распространения сигнала от адресного входа до выхода при переключении входа из 0 в 1 (tPLH =35 нс).

Рис.37 Задержка распространения сигнала от адресного входа до выхода при переключении входа из 1 в 0 (tPHL =33 нс).

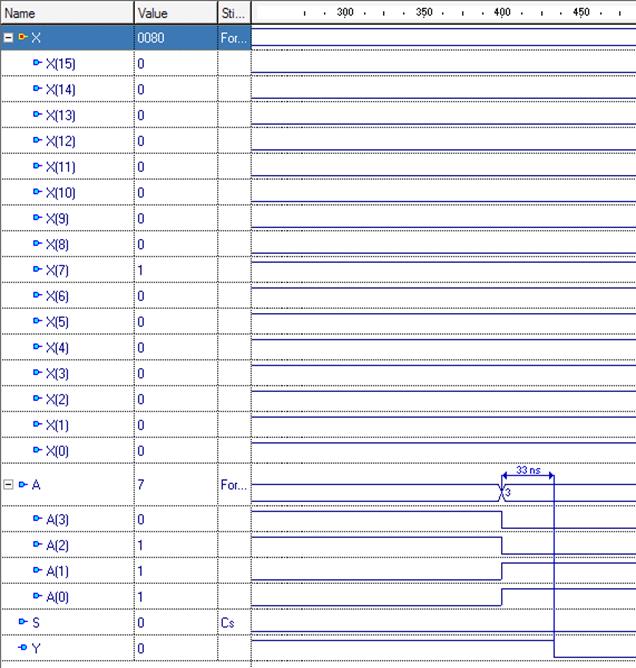

Рис.38. Задержка распространения сигнала от информационного входа до выхода при переключении входа из 0 в 1 (tPLH =14 нс).

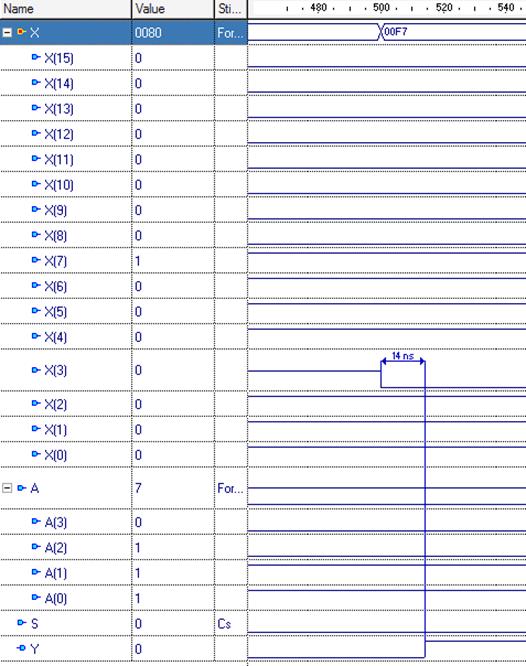

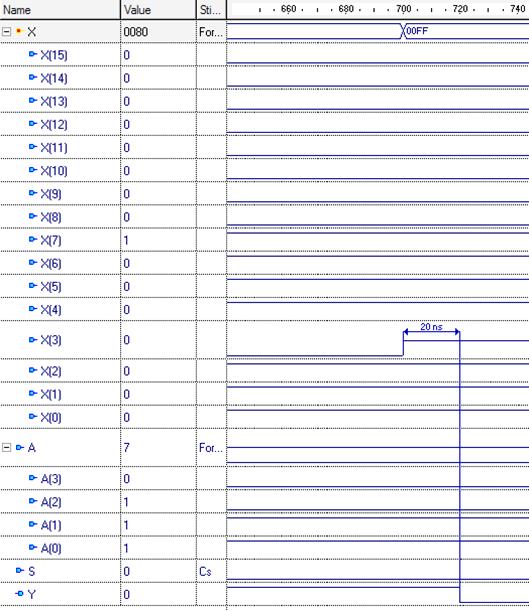

Рис.39. Задержка распространения сигнала от информационного входа до выхода при переключении входа из 1 в 0 (tPHL=20 нс).

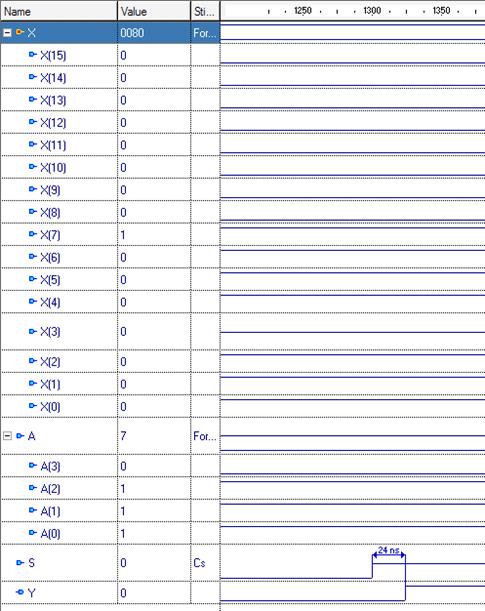

Рис.40. Задержка распространения сигнала от стробирующего входа до выхода при переключении входа из 0 в 1 (tPLH =24 нс).

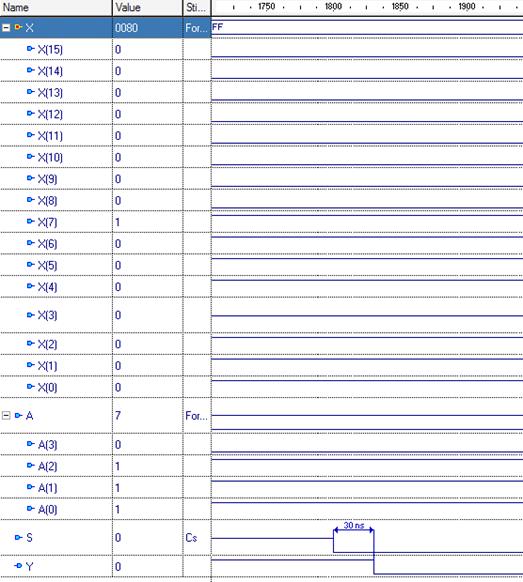

Рис.41. Задержка распространения сигнала от стробирующего входа до выхода при переключении входа из 1 в 0 (tPHL =30 нс).

Поведенческая VHDL-модель узла представлена в разделе 7.11.

Рис.42.Схема верификации иерархического символа с подключенной vhdl-моделью.

Рис.43. Результаты моделирования проектируемого узла.

Как видно из рис. 43 VHDL-модель работает корректно на всех режимах.

В курсе “Моделирование” данная курсовая работа является обобщением опыта, накопленного в 6 семестре. При написании работы использовались навыки, полученные в ходе выполнения лабораторных работ и РГР: работа в пакетах САПР Orcad 9.1 и Active-HDL 8.1, а также навыки программирования на языке VHDL.

Целью данной курсовой работы было проектирование схемы замещения цифрового узла, представляющего собой существующую микросхему 16-разрядного инверсного мультиплексора со стробированием 155КП1. Были проведены имитационные эксперименты с разработанным узлом, целью которых являлось подтверждение работоспособности узла.

В ходе работы я использовал уже знакомые мне методы: разработку схем замещения в PSPICE, PCB Simulate-проектах и в Active-HDL 8.1 на собственноручно сделанных элементах, создание VHDL-моделей элементов и самой микросхемы. Единственным новшеством для меня стало создание собственной математической модели элемента в PSPICE-проекте, в котором необходимо было сделать различные задержки от разных входов.

Выполняя курсовую работу, я использовал два различных пакета САПР: Orcad 9.1 и Active-HDL 8.1 и имел возможность непосредственно сравнить их. По моему мнению, при этом сравнении с большим отрывом победил Active-HDL 8.1. Этот пакет отличается современным, эргономичным интерфесом, надежностью работы (при работе в Orcad 9.1 у меня несколько раз случались неожиданные “вылеты” и иногда приходилось перезагружать компьютер для дальнейшей работы) и содержит множество удобнейших функций: инструменты работы с диаграммами и т.д. Также стоит отдельно отметить, что в Active-HDL 8.1 функция возврата к предыдущему шагу (Ctrl+Z) возможна более одного раза, в отличие от OrCad 9.1. В OrCad 9.1 из-за этого недостатка мне приходилось постоянно сохранять результаты работы перед внесением новых изменений, ведь я знал, что не смогу вернуться на несколько шагов назад.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.