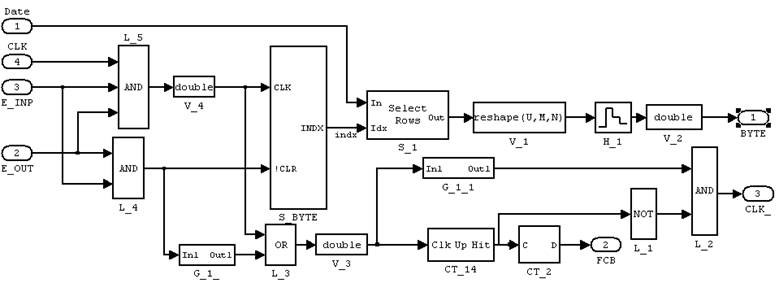

Рис. 40. Схема выборки номера байта BYTE_

![]() С

частотой определяемой сигналом входного порта CLK в

блоке S_BYTE вырабатывается

последовательность индексов (INDEX), которые

используются для выбора очередного байта из кадра, поступившего на входной порт

Date. Байты выставляются на порт BYTE.

Блок СТ_14 осуществляет счет выданных байт и в конце кадра (после 14-го байта)

выдает сигнал на порт CLK_, блок СТ_2 определяет бит с

номером кадра (FCB).

С

частотой определяемой сигналом входного порта CLK в

блоке S_BYTE вырабатывается

последовательность индексов (INDEX), которые

используются для выбора очередного байта из кадра, поступившего на входной порт

Date. Байты выставляются на порт BYTE.

Блок СТ_14 осуществляет счет выданных байт и в конце кадра (после 14-го байта)

выдает сигнал на порт CLK_, блок СТ_2 определяет бит с

номером кадра (FCB).

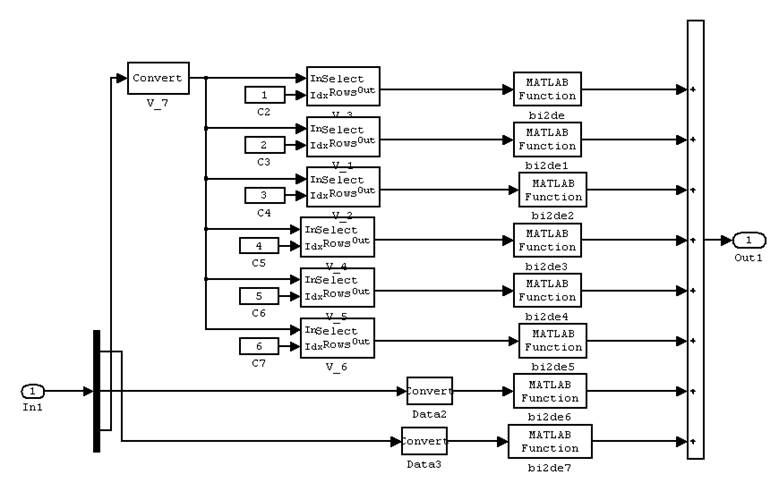

Вычисление суммы по модулю 256 показано на рис. 41. Входные данные данного блока вычисляются путем перевода бинарного представления каждого контролируемого байта кадра в десятичное исчисление и суммирования полученных результатов. Для выполнения приведенных вычислений применяются функции MATLAB bi2de. Одна из возможных схем вычислений приведена на рис. 42

Рис. 42. Вычисление суммы байт

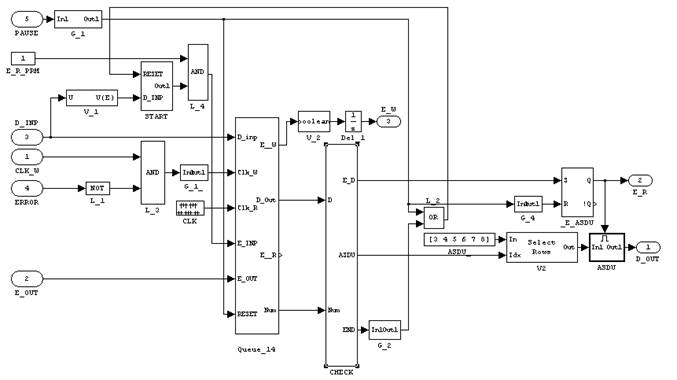

Канальный уровень приемной станции. Модель канального уровня приведена на рис. 43. Канальный уровень получает от физического уровня байты, формирует из них кадр, проверяет его на отсутствие искажений, выделяет из кадра блок ASDU и передает его прикладному уровню. От физического уровня блок получает тактовые импульсы записи CLK_W, входные байты D_INP, сигналы ошибки приема байта ERROR, состояния паузы в линии PAUSE. Кроме того на вход поступают разрешение прикладного уровня на запись в него данных E_OUT. Прикладному уровню блок передает через порт D_OUT блок ASDU и сигнал разрешения считывания данных E_R. Для физического уровня вырабатывается сигнал разрешения записи данных в канальный уровень E_W.

![]() Схема

модели канального уровня приведена рис. 44. Блок START

осуществляет проверку принятых байт на соответствие их шаблону START2. При обнаружении такого байта дается разрешение на

заполнение очереди принимаемого кадра Queue_14.

Схема

модели канального уровня приведена рис. 44. Блок START

осуществляет проверку принятых байт на соответствие их шаблону START2. При обнаружении такого байта дается разрешение на

заполнение очереди принимаемого кадра Queue_14.

Рис. 44. Схема модели канального уровня приемника

Ввод данных в очередь осуществляется при отсутствии активного сигнала ERROR от физического уровня. Частота записи данных соответствует частоте приема символов физическим уровнем. При получении сигнала PAUSE осуществляется дополнительное разрешение на очистку очереди, что необходимо при получении такого сигнала до полного приема кадра. Сброс схемы START осуществляется после приема последнего байта кадра или после получения сигнала PAUSE.

Регистр входных данных после заполнения очереди выставляет на порт E_W сигнал разрешения чтения данных, а сами данные поставляются через порт D_out. Кроме того на порт Num выставляются данные о номере считываемого из регистра байта. Блок CHECK осуществляет проверку принятого кадра на отсутствие искажений. При приеме неискаженного кадра блок данных прикладного уровня выставляется на порт ASDU, одновременно переводится в активное состояние порт разрешения выдачи данных E_D. На порт END активный сигнал выставляется при приеме последнего байта кадра. Элемент V2 осуществляет выборку блока ASDU из принятого кадра и при наличии разрешения выставляет на выходной порт схемы D_OUT. Одновременно выставляется разрешающий сигнал, разрешающий чтение блока данных ASDU прикладным уровнем (порт E_R).

Схема блока проверки кадра дана на рис. 45. Схема получает вводимые в регистр хранения данные через порт D. Одновременно через порт Num поступает номер байта в регистре. На основании этой информации блок START_2_1 осуществляет поиск первого байт со значением START2. При получении этого значения запоминается номер принятого байта в блоке N_0. Полученные данные используются для вычисления номера текущего байта относительно первого полученного байта (с кодом START2). Срабатывание блока START2_1 разрешает работу всех схем проверки элементов кадра. Кроме того, срабатывание блока START_2_1 выставляет логическую единицу на схему проверки отсутствия искажения кадра Е_R1. Второй и третий байт кадра должны содержать длину кадра и быть равными друг другу. Проверку осуществляет блок «L_1=L_2». При этом второй байт запоминается в регистре RG1 и выдается для проверки при приеме третьего байта.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.