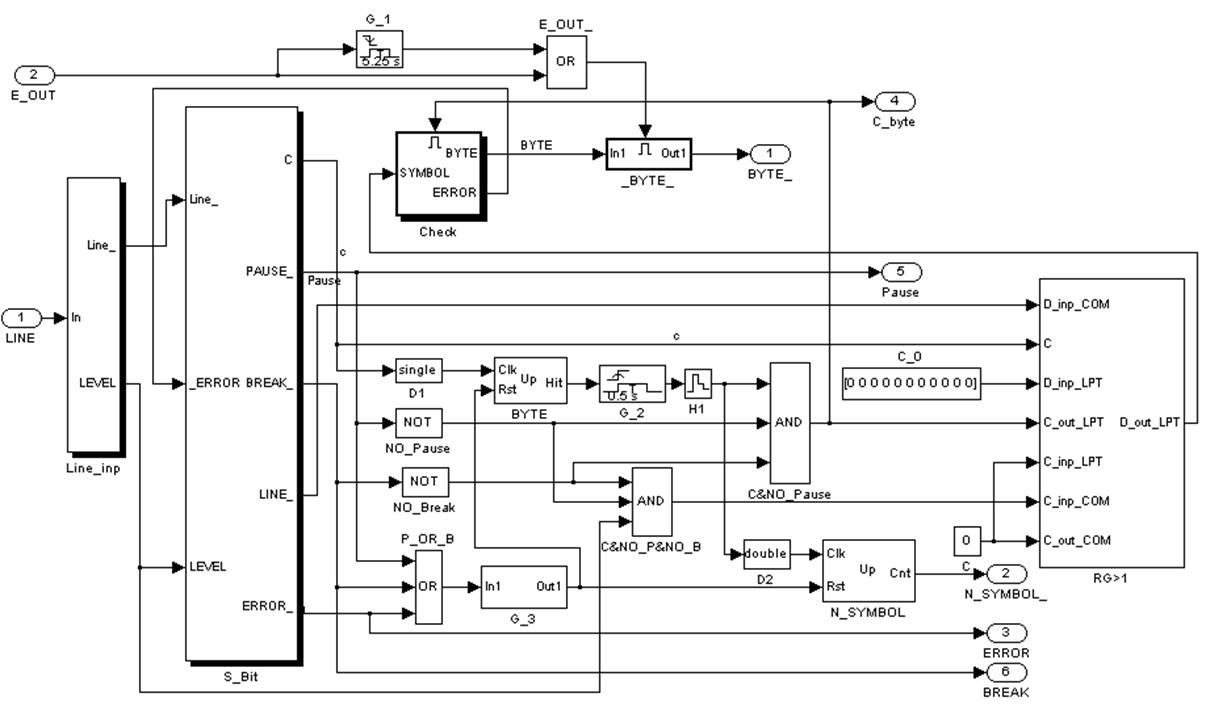

Схема модели физического уровня приемника дана на рис.33. Входной сигнал с линии поступает на линейный приемник Line_inp, где осуществляется измерение уровня сигнала и формирование логических значений 1 и 0. Логические значения поступают на его выходной порт Line_. Второй порт signal_ вырабатывает логическую 1 при нахождении уровня входного сигнала в допустимом пределе и разрешает ввод данных в сдвигающий регистр RG>.

Селектор бит S_Bit осуществляет определение значения бита на каждом бодовом интервале. Определяемые биты выставляются на его выходной порт LINE. Порты PAUSE, BREAK селектора бит активизируются при определении соответствующего состояния линии. Сигнал ERROR_ транслируется селектором со своего входного порта _ERROR. Порт С активизируется на каждом бодовом интервале во время проверки значения текущего бита и вырабатывает строб-сигнал (на 5-м импульсе внутреннего тактового генератора).

Подсистема Check осуществляет проверку текущего символа на корректность и выделяет из символа байт данных. Сформированный регистром сдвига RG< символ поступает на входной порт SYMBOL. Работа подсистемы разрешается элементом C&NO_Pause при условии, что линия связи не находится ни в состоянии «пауза», ни в состоянии «обрыв» и принимаемый бит является 11-м в текущем символе (стоп-битом).

Выделенный байт данных выставляется на порт BYTE, а при обнаружении ошибки активный сигнал вырабатывает порт ERROR

Счетчик символов кадра N_SYMBOL увеличивает свои показания при каждом принятом символе и сбрасывается в исходное состояние при возникновении активного значения одного из сигналов «ошибка», «пауза» или «обрыв» (логическая схема P_OR_B).

Регистр сдвига RG> осуществляет прием бит по входу D_inp_COM и выдачу символов по выходу D_out_LPT. Его вход C принимает строб-сигнал интервала идентификации текущего бита, который используется в качестве тактового сигнала сдвига регистра. Порт С_inp_COM разрешает ввод очередного бита, а порт C_out_LPT разрешает выдачу символа по выходу D_out_LPT. Остальные порты блокированы соответствующими элементами схемы.

Генераторы импульсов G_1, G_2, G_3 обеспечивают согласование работы элементов по времени, а преобразователи D1 и D2 – по типу данных модели.

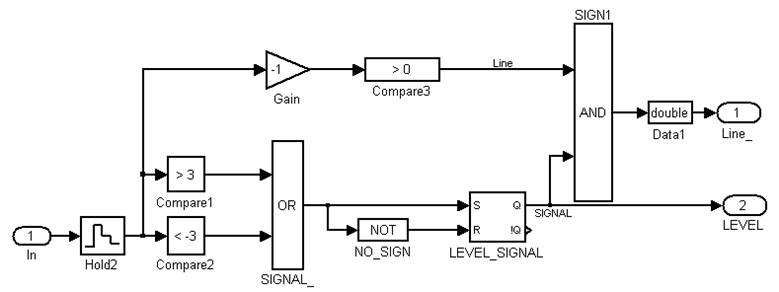

Модель линейного блока физического уровня представлена на рис. 34. Блок преобразует уровни сигналов интерфейса RS-232 в логические уровни (Compare3) и проверяет допустимость принятого сигнала по амплитуде (Compare1, Compare2, SIGNAL_, LEVEL_SIGNAL). При допустимом уровне принимаемого сигнала его логическое значение выставляется на выходной порт Line_. Результат проверки выдается на выходной порт LEVEL.

Рис. 34. Схема линейного блока физического уровня приемника (Line_inp)

Рис. 33. Схема модели физического уровня приемника.

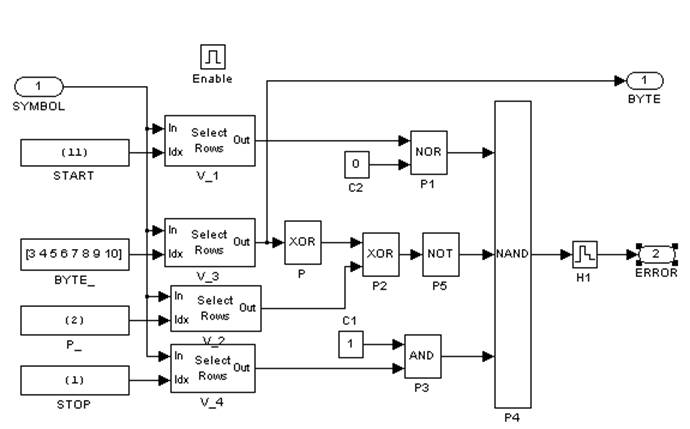

Схема модели контроля правильности полученного символа Check дана на рис. 35. При активизации блока Check блоки селекции V_1…V_4 выделяют элементы символа с учетом приема символа младшим битом вперед. Логические блоки P1, P3 осуществляют сравнение контролируемых бит с шаблонами. Блок P вычисляет признак четности байта символа, блоки P2, P5 сравнивают вычисленное значение с битом четности символа. Результаты проверок обрабатываются и выставляются на порт ERROR. Выделенный из принятого символа байт передается на порт BYTE.

Рис.35. Схема контроля символа (Сheck)

Схема модели селектора бит приведена на рис. 36. Тактовый генератор GT выдает импульсы с частотой в 16 раз превышающую бодовую. В схемы его сигналы поступают после срабатывания триггера START. Этот триггер возбуждается при получении из линии связи перепада 1/0 через генератор одиночного импульса G1.Сброс триггера START производится при одном из следующих условий: получен стоп-бит, обнаружено состояние «пауза», обнаружено состояние «обрыв» через логический блок L3.

Элемент задержки Del3 на выходе триггера START обеспечивает разрыв алгебраической петли. Тактовые сигналы GT поступают на счетчика S_BIT, который на 5-ом импульсе выдает с его выхода Hit логическую единицу (строб). Выделенный интервал времени используется для проверки значения принимаемого бита. Бит данных, поступивший через порт Line_, обрабатывается компараторами Comp1, Comp2 и поступает на схемы выделения сигналов высокого H или низкого L состояния. Выделенные сигналы переключают триггер _LINE_ который и выдает принимаемые биты на порт LINE_.

Одновременно производится определение длительностей высокого и низкого состояний, которое затем сравнивается с пороговыми значениями признаков паузы T_P и обрыва T_B. Элементы сравнения R1 и R2 при превышении установленных порогов возбуждают соответствующие триггеры PAUSE или BREAK. Триггер фиксации ошибки _ERROR возбуждается от входного порта _ERROR, а сбрасывается при возникновении состояния «пауза». Выход этого триггера поступает на выходной порт ERROR_. Стробы проверки уровня бит при возбужденном состоянии триггера START выдаются на выходной порт C.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.