Рис.17. Схема модели D-триггера

а – внутренняя схема, б – организация синхронизируемых R-S-входов

Подключение внешних информационных входов к R_S_D триггеру и образование ячейки регистра приведено на рис. 18 а). На рис. 18 б) показан фрагмент внутренней схемы регистра сдвига, построенного из полученных ячеек памяти. На входы !CLR всех ячеек подается постоянный разрешающий сигнал. Этот сигнал поступает на управляющий вход «С» модели D-триггера (см. рис. 17 а). Параллельные данные поступают на вход D_inp_LPT и демультиплексором распределяются по входам ячеек D_inp_LPT. Последовательные данные поступают на вход D_inp_COM первой ячейки регистра. Все последующие ячейки получают последовательные данные с Q-выходов предыдущих ячеек. Параллельный выход D_out_LPT образуется мультиплексором, подключенным к Q-выходам всех ячеек. Последовательный выход D_out_COM представляется Q-выходом последней ячейки. Управляющие входы регистра через логические схемы И (AND) контролируют прохождение информационных сигналов.

![]() а) б)

а) б)

![]()

Рис. 18. Сдвигающий регистр

а – внутренняя схема ячейки регистра, б – фрагмент внутренней схемы регистра сдвига,

Для получения регистра, преобразующего параллельный код на входе, в последовательность бит на выходе, часть управляющих и информационных входов внутри схемы регистра подключаются к постоянным логическим сигналам 1 и 0. Таким образом, получен внешний вид модели регистра сдвига, примененного в модели физического уровня передающей станции.

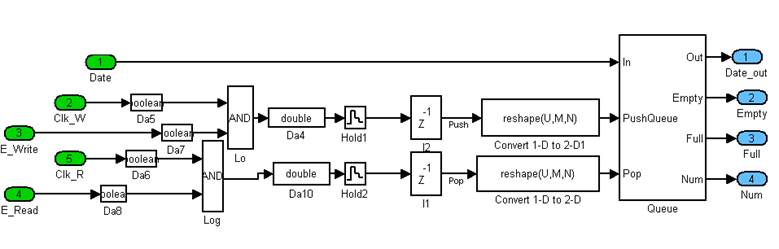

Очередь (Queue). Очередь может быть применена для организации взаимодействия двух частей модели функционирующих с различными частотами синхронизации (в общем случае не кратными друг другу). Библиотечный элемент Queue дополняется управляющими портами разрешения на запись E_Write и разрешения на чтение E_Read (рис. 19). Дополнительные преобразования типов данных потребовались для согласования управляющих сигналов с данными. Задержка на один такт введена для обеспечения считывания и записи в очередь после установления входных данных Date. Выходные порты с предупреждающими сигналами об опустошении очереди (Empty) и ее заполнении (Full) предусмотрены для последующей организации управления очередью. Порт с показаниями количества записей в очереди (Num) установлен для наблюдения за состоянием очереди в процессе отладки.

Рис. 19. Управляющие входы блока очередь

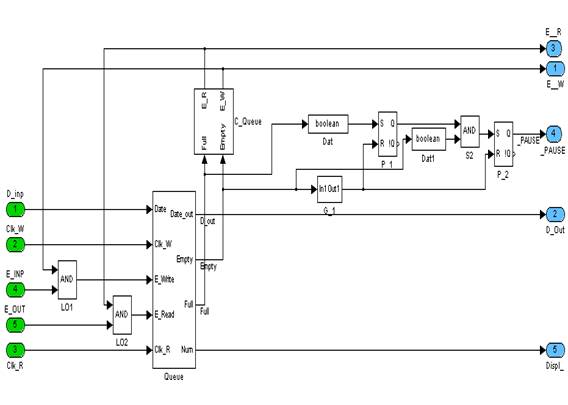

На рис. 20 показано использование очереди для организации следующего алгоритма. Входные данные записываются в очередь с частотой, определяемой портом clk_W. Разрешение на запись дается лишь при условии, что перед началом записи очередь опустошена. После заполнения очереди разрешение на запись снимается и выставляется разрешение на чтение E_R. Чтение из очереди производится с частотой, задаваемой портом clk_R. После опустошения очереди разрешение на чтение снимается и выставляется разрешение на запись E_W. Указанный алгоритм обеспечен блоком управления очередью C_Queue и логическими схемами LO1, LO2. Дополнительный порт _Pause выдает активный сигнал после завершения цикла запись-чтение очереди, что может использоваться для генерации сигнала паузы в линию связи.

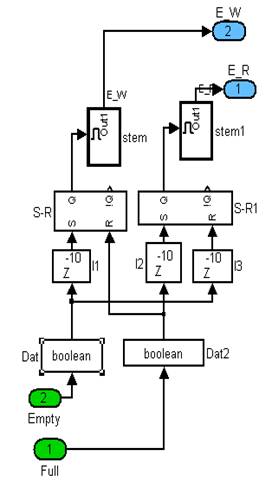

Блок управления очередью приведен на рис.21 а). Он представляет собой триггерные схемы, фиксирующие моменты опустошения и заполнения очереди. Временные задержки I1, I2, I3 введены для согласования работы блока с внешней схемой. Внешний вид построенной системы очередь приведен на рис. 21 б).

Рис. 20. Управление последовательностью записи-чтения очереди а) б)

Рис. 21 Подсистема очередь

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.