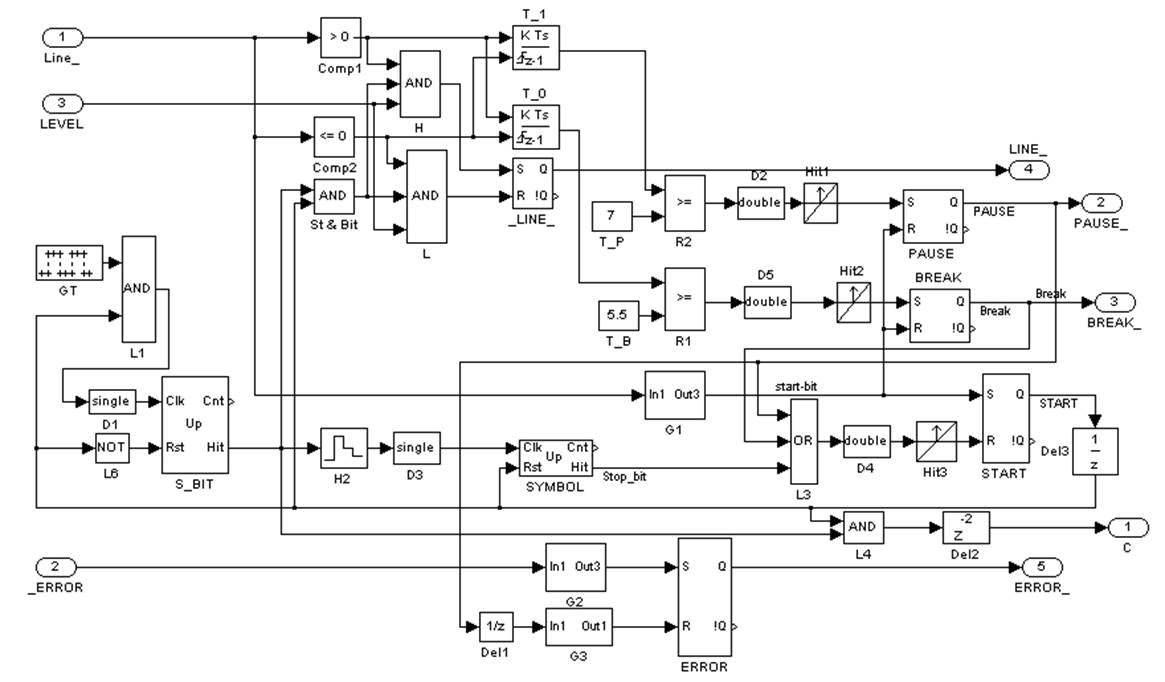

Рис. 36. Схема модели селектора бит физического уровня приемника

Канальный уровень обеспечивает передачу и прием кадров. Этот уровень взаимодействует с прикладным и физическим уровнями, являясь посредником между ними. Протокол обмена между канальными уровнями передающей и приемной стороны включает в себя средства защиты от искажения, потери или дублирования кадра. Рассмотрим канальные уровни передающей и приемной станций при работе телеуправления.

![]() Канальный

уровень передающей станции. Канальный уровень приведен на рис. 37. Он

получает от прикладного уровня блоки данных ASDU и

количество попыток посылки кадра приемной стороне. Уровень формирует заголовок

кадра, подсчитывает контрольную сумму и оформляет окончание кадра. Формат кадра

зависит от типа передаваемого сообщения. Ограничимся рассмотрением процедуры

передачи приказа. Сформированный кадр в виде последовательности байт

предоставляется физическому уровню, который осуществляет выборку

последовательность байт в соответствии со скоростью передачи в линии связи. Для

согласования скоростей формирования кадра и выборки его байт используется

очередь.

Канальный

уровень передающей станции. Канальный уровень приведен на рис. 37. Он

получает от прикладного уровня блоки данных ASDU и

количество попыток посылки кадра приемной стороне. Уровень формирует заголовок

кадра, подсчитывает контрольную сумму и оформляет окончание кадра. Формат кадра

зависит от типа передаваемого сообщения. Ограничимся рассмотрением процедуры

передачи приказа. Сформированный кадр в виде последовательности байт

предоставляется физическому уровню, который осуществляет выборку

последовательность байт в соответствии со скоростью передачи в линии связи. Для

согласования скоростей формирования кадра и выборки его байт используется

очередь.

Рассмотрим формирование кадра переменной длины (формат L). Схема модели канального уровня приведена на рис.38. Полученный от прикладного уровня блок ASDU оформляется в кадр блоком FRAME и записывается (при наличии разрешения от прикладного уровня на входе E_INP) в регистр хранения Queue_1. Регистр хранения выполнен на основе очереди размером в одну запись. После записи данных регистр хранения выставляет активный сигнал на порт E_R, а данные - на порт D_Out. Блок BYTE_ с частотой, определяемой генератором CLK, осуществляет последовательное считывание байт кадра и запись их в выходную очередь Queue_14. Разрешение на запись в эту очередь вырабатывается после ее опустошения (считывание всех ранее записанных данных) и выставляется на порт E_W. Разрешение на чтение очереди Queue_14 выставляется на порт E_R после заполнения очереди входными данными, сами данные выставляются на порт D_Out. Номер кадра FCB вычисляется в блоке BYTE_ и записывается в командный байт кадра блоком FRAME. Данные поступают на выходной порт схемы D_OUT только при совпадении трех условий (блок L_5): наличие синхросигнала считывания (это сигнал, совпадающий с моментом времени выдачи физическим уровнем стоп-бита, порт CLK_R), разрешение на прием данных физическим уровнем (порт Е_OUT схемы) разрешение на выдачу данных регистром Queue_14 (порт E_R регистра).

Триггер Pause_ вырабатывает сигнал «пауза» при условии получения сигнала о начале паузы от блока Queue_14, синхронизируя его со стоп-битом. Сброс триггера Pause_ осуществляется после отсчета требуемого интервала времени (блоки G_1, G_2). Сигнал «пауза» останавливает запись в блок Queue_14, запрещает считывание данных из блока BYTE_ и снимает разрешение чтения данных физическим уровнем (порт E_R).

Счетчик посылок кадров ST_SEND сравнивает число разрешенных попыток посылки одного и того же кадра с количеством выполненных посылок и при достижении установленного лимита (порт N_r) выставляет отрицательное сообщение для прикладного уровня.

Рис. 38. Схема модели канального уровня передатчика

На рис. 39 приведена схема формирования кадра. Кадр формируется путем вертикальной конкатенации байт заголовка кадра (START2, L, L, START2), командного байта С, байта адреса приемной станции А, блока данных ASDU, байт контрольной суммы (КС) и окончания кадра (END). Командный байт формируется путем включения в него бита номера кадра FCB, и кода команды FC. Код команды выбирается из таблицы возможных кодов селектором S_1.

Рис. 39. Схема формирования кадра блоком FRAME

Адрес приемной станции копируется из блока ASDU элементом S_2. Контрольная сумма вычисляется по данным командного байта С, байта адреса А и байт блока ASDU путем суммирования по модулю 256 в блоке КС и записывается в состав кадра.

На рис. 40. приведена схема выборки байта из регистра хранения.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.