Таблица 5.16 Назначение событий внешних прерываний, когда объединяются две последовательности команд Pи Q

|

cycle |

ev[j] JISR |

full.3 full.4 |

M WB |

|

T - 1 |

0 0 |

1 |

Ip |

T = ţ |

1 1 |

1 1 |

Ip+1 Ip |

|

T + 1 |

1 0 |

0 0 |

- - |

|

1 0 |

0 0 |

- - |

|

|

t - 1 |

1 0 |

1 0 |

J0 - |

|

t |

1 0 |

1 |

J0 |

Доказательства, работающие с допустимостью ISR (раздел 5.4) рассуждают только о сигнале JISRи значениях регистров и памяти, видимых программисту на ассемблере, т.е., файлах регистров общего и специального назначения, двух PC и двух памятях IM и DM:

C = {GPR[0],...GPR[31], SPR[0],..., SPR[5], PC', DPC, DM, IM}.

Поэтому для моделирования сигнал JISRи содержание хранилища Cимеет повышенный интерес.

|

Теорема 5.11 |

Пусть P = I0 ,..., Ip ,..., Ip+δ и P' = I0 ,..., Ip – две последовательности команд расширенные последовательностью внешних событий, как определено выше. Последовательность P выполняется конвейерной конструкцией DLXП а P' последовательной конструкцией DLX∑. Пусть команда I0 предшествует JISR

JISR∑-1 = 1 и JISRП0 = 1,

и пусть обе конструкции стартуют в одинаковой конфигурации, т.е.,

VR € CR∑0 = R1П .

Пусть Tp и Tp' означают циклы, в которых Ip обрабатывается на этапе обратной записи

IП(4, Tp) = I∑(4, Tp') = p /\ ue.4ПTp = 1.

Тогда проинициализированные PC имеют значения PC'∑0 = SISR + 4 и DPC∑0 = SISR. Для любой команды Ii € P', любого этапа k, и любых двух циклов T, T ' при

IП(k,T)=I∑(k, T ') = i /\ ue.kПT = 1

должны выполняться следующие два требования:

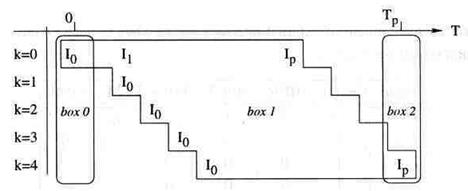

Рисунок 5.20 Пары (k, T) конвейерного выполнения. Поле 0 покрывается по гипотезе моделирующей теоремы, поля 1 и 2 соответствуют требованиям 1 и 2.

1. (a) для всех сигналов S этапа k, которые являются входами регистра R€ out(k) обновляемого в конце циклаT:

SПT = S∑T ',

(b) для всех регистров R € out(k), которые видимы или обновляются в конце цикла T:

(c) для любой ячейки M памяти данных DM и k = 3:

mпt+1 = m∑t '+1 = mi,

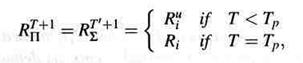

2. и для любых R € C и T = Tp

RПT+1 = R∑T '+1 = Rp .

Что касается конвейерного выполнения, существует три типа пар (k, T) для которых значения STи RT+1сигналов Sи выходных регистров Rэтапа kпредставляют интерес (рисунок 5.20):

• Для первого цикла теорема делает предположение о содержимом всех регистров и памяти R € Cнезависимо от этапа, которому они принадлежат (поле 0).

• Требование 1 покрывает все пары (k, T), для которых IП(k, T) определен и лежит между 0 и p(поле 1).

Таблица 5.17 Начало выполнения после сброса или JISR соответственно

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.