Dmw.3 := Dmw.2 /\ CA.2[2].

Как и прежде, обновление памяти запрещено, если этап памяти пуст

Dmw'.3 = Dmw.3 /\ full.3.

Сигнал Dmw'.3 используется контроллером памяти DMC для генерирования сигналов записи в банки.

Остальные синхроимпульсы и сигналы записи, разрешены как и прежде. С этим механизмом останова, сброс воспитывает конструкцию DLX∑независимо от того, в каком состоянии аппаратура была прежде:

|

Лемма 5.8 |

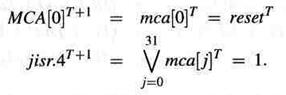

Пусть T – последний машинный цикл, в котором активен сигнал сброса. Тогда в следующем машинном цикле конструкция DLX∑ сигнализирует о прерывании вызванном сбросом и выполняет переход на ISR:

resetT = 1 /\ resetT+1 = 0 -> JISRT+1 = 1 and MCA[0]T+1 = 1.

|

PROOF |

Так как сигнал глобальной синхронизации генерируется как

CE = (Ibusy NOR Dbusy) \/ reset,

конструкция DLXΣсинхронизируется всякий раз, когда сигнал сброса активен, и особенно в цикле T. Из-за сброса флаги full[4 : 0] инициализируются

full[4 : 0]T+1 = 10000,

и сигнал разрешения синхронизации для выходных регистров CApro

CA4ceT = ue.3T \/ resetT = 1.

Следовательно, выходные регистры схемы обработки причин обновляются в конце цикла Tзначениями

|

QED |

Следовательно,

JISRT+1= jisr.4T+1 /\ full.4T+1 = 1,

и ISR(0) вызывается в цикле T + 1.

Управляющий автоматis конструируется как для конструкции DLXσбез обработки прерываний (раздел 4.2.3). Автомат моделируется последовательной FSD, который тогда преобразуется в вычисляемое заранее управление:

• Управляющие сигналы этапа IF и сигналы Мура этапа ID всегда активны, тогда как сигналы Mealy этапа ID вычисляются в каждом цикле.

• Управляющие сигналы остальных этапов – вычисляются заранее в течении ID. Это возможно потому, что все их состояния имеют выход степени один. Существует три типа сигналов: сигналы xиспользуются только на этапе EX, сигналы yиспользуются на этапах EX и M, и сигналы zиспользуются на всех трех этапах.

Однако, есть три изменения. Автомат должен просчитывать 8 новых команд (таблица 5.4). Он должен выполнять проверку на неверный код операции, т.е., кодирует слово команды команду DLX или нет. В отличие от конструкции DLXσ , все регистры путей данных невидимые для программиста на ассемблере (т.е., все регистры за исключением PC', DPC, и двух файлов регистров) теперь обновляются каждой командой. Для всех этих регистров автомат просто обеспечивает простой сигнал запроса синхронизации 1.

Невидимые регистры этапа выполнения включают регистры данных MAR и MDRw и буферизированные IR.3, Cad.3, Sad.3, PC.3, DPC.3, и DDPC.3. По умолчанию, эти регистры обновляются так

(IR.3, Cad.3, Sad.3) := (IR.2, Cad.2, Sad.2)

(PC.3, DPC.3, DDPC.3) := (PC.2,DPC.2,DDPC.2)

(MAR, MDRw) := (A,shift(A, co[4:0]))

Помимо буферов, невидимые регистры этапа памяти включают регистры данных C.4 и MDRr. По умолчанию они обновляются следующим образом:

(IR.4, Cad.4, Sad.4) := (IR.3, Cad.3, Sad.3)

(PC.4, DPC.4, DDPC.4) := (PC.3, DPC.3, DDPC.3)

(C.4, MDRr) := (MAR, DMdefault).

Автомат моделирует FSD на рисунке 5.12. Таблицы 5.6 и 5.7 перечисляют RTL команды; обновление невидимых регистров перечислено, только если оно отличается от ‘по умолчанию’. Обратите внимание, что на этапах M и WB, rfe обрабатывается подобно специальному перемещению movi2s. Таблица 5.8 перечисляет сложные дезьюктивные нормальные формы а таблица 5.10 перечисляет параметры автомата.

На этапе ID расширен только выбор программных счетчиков и констант. Это вычисление требует двух дополнительных сигналов Mealy rfe.1 и Jimm. На этапе EX автомат теперь также выполняет проверку на неверные команды; в случае неопределенного кода операции автомат переходит в состояние I11. Так как это состояние имеет наибольший indegree, I11 служит новым начальным состоянием. Состояние noEX используется для всех верных команд, которые уже закончили свое фактическое выполнение на этапе ID, т.е., ветвления beqz и bnez и два перехода jr и j.

|

|

Рисунок 5.12 FSD конструкции DLX∑ с обработкой прерываний

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.