чтение, поскольку контроллер DMC генерирует четыре сигнала записи в банки Dmbw[3 : 0] и проверку на нарушение границ.

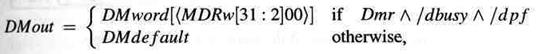

За исключением выхода данных DMoutи дополнительного флага dpf, функциональность памяти данных DM остается той же. Флаг dpfпоказывает, что память не в состоянии выполнить требуемый доступ из-за отсутствия страницы. Если память DM обнаружит отсутствие страницы (dpf= 1), она отменит продолжение доступа. Таким образом, память сама гарантирует, что она не изменится командой записи, которая является причиной page fault. Флаги dpfи dbusyнеактивны, если память не выполняет доступ (Dmr.3 = Dmw.3 = 0). При успешном доступе по чтению, память данных DM обеспечивает требуемое слово памяти, иначе, она предоставляет фиксированное значение DMdefault:

Контроллер памяти DMC В дополнение к сигналам записи в банк, контроллер памяти DMC теперь обеспечивает сигнал dmal, который указывает на доступ с нарушением границ.

Сигналы записи банков Dmbw[3:0] генерируются, как и раньше. Кроме того, схема DMbwпредоставляет сигналы B(byte), H(half word) и W(word), которые указывают размер обращения к памяти и сигналы B[3:0], удовлетворяющие

B[j] = 1 <-> (s[1:0]) = j.

Байтовый доступ всегда выровнен правильно. Доступ по слову выровнен, только если он начинается с адреса 0, т.е., если B[0] = 1. Доступ по полуслову расположен с нарушением границ, если он начинается с байта 1 или 3. Флаг dmalсигнализирует, что требуется доступ к памяти данных, и что этот доступ – с нарушением границ (malAc=1):

dmal = (Dmr.3 \/ Dmw.3) /\ malAc

malAc = W /\ ![]() \/ H /\ (B[l] \/ B[3])

\/ H /\ (B[l] \/ B[3])

Стоимость cdmcконтроллера памяти увеличивается на несколько вентилей, но задержка ddmcконтроллера остается неизменной:

cdmc = CDMbw + Cinv + 3 • Cand + 3 • Cor

= Cdec(2) + 3 • Cinv + 15 • Cand + 8 • Cor.

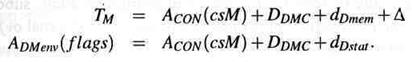

Пусть acon(csm) означает накопленную задержку сигналов Dmrи Dmw, время цикла окружения памяти данных и задержка этих флагов может быть выражена как

|

|

Рисунок 5.9 Схемотехника окружения причины CAenv

5.5.5 Окружение причины CAenv

Окружение причины CAenv (рисунок 5.9) выполняет две основных задачи:

• Его схема CAcol собирает события, вызывающие прерывания и синхронизирует их в регистр причин.

• Оно обрабатывает перехваченные события, вызывающие прерывания и инициирует переход на ISR. По этой причине обрабатывающая схема CApro генерирует флаги jisrи repeat, и обеспечивает причину маскируемого прерывания MCA.

Сбор причин

Внутренние события, вызывающие прерываний генерируются путями данных и блоком управления, но этап, в котором конкретное событие обнаруживается, зависит от самого события (таблица 5.5).

Память команд и ее контроллер IMC обеспечивают флаги ipfи imal, которые указывают на отсутствие страницы или нарушение границы при выборке. Флаг dmal, генерируемый контроллером DMC сигнализирует о доступе к памяти данных с нарушением границ. Флаги dmalи imalобъединены с флагом событий mal. На этапе памяти (memory), флаг dpfпамяти данных сигнализирует об отсутствии страницы при чтении/записи.

Ловушка и неверная команда illобнаруживаются модулем управления. Это будет сделано на этапе EX, чтобы сохранить автомат простым (см. стр. 208). ALU предоставляет флаг переполнения ovf, но арифметическое переполнение должно быть сообщено только в случае команд addo, subo, addio или subio. Такие команды указывают управляющим сигналом ovf? когда активизирована проверка переполнения.

Таблица 5.5 Назначение Внутренних Событий, вызывающих прерывания. Перечислено, на каком этапе и каким блоком генерируется сигнал события.

|

событие |

сигнал |

этап |

блок |

|

ill |

ill |

EX |

блок управления |

|

mal |

imal |

IF |

управление памятью команд IMC |

|

dmal |

M |

управление памятью данных DMC |

|

|

pff |

ipf |

IF |

окружение памяти команд IMenv |

|

pfls |

dpf |

M |

окружение памяти данных DMenv |

|

trap |

trap |

EX |

блок управления |

|

ovf |

ovf A ovf? |

EX |

окружение ALU, блок управления |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.