Так как сигналы событий вызывающих прерывания обеспечиваются несколькими конвейерными этапами, регистр причины CAне может присваиваться на единственном этапе. Следовательно регистр CA с конвейерной организацией: CA.iсобирает события, которые команда включает до этапа i. Это требует осторожности от внутренних событий. Внешние события могут быть отловлены на любом этапе, но для сокращения времени ответа они присваиваются этапу памяти.

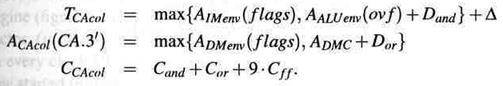

Управляющие сигналы этапа EX - вычисляемые заранее. Время цикла сбора причин CAcol, накопленная задержка выхода CA.3' и стоимость могут быть выражены как:

Обработка причин

|

|

|

Повторение прерывания сигнализируется, если отсутствие страницы - событие наивысшего приоритета среди всех прерывающих событий jс mca[j] = 1: |

|

repeat = |

(рисунок 5.10) Маскируемая причина mcaполучена маскированием событий маскируемых прерываний CA.3' соответствующими битами регистра состояний SR. Флаг jisrустановлен, если mcaотличен от нуля, т.е., если по крайней мере один бит mca[i] равен единице.

|

|

Рисунок 5.10 Обработка причин схемой CApro.

Схема CAtypeгенерирует флаг repeatсогласно этому уравнению. В конце цикла маскируемая причина и два флага jisrи repeatсинхронизируются с регистром. Стоимость и время цикла схемы обработки причин CApro может быть вычислена как

Стоимость и время цикла всего окружения причин CAenv равно

CCAenv = CCAcol + CCApro TCAenv = max{TCAcol , TCApro}.

5.5.6 Блок управления

Как в предыдущей конструкции, блок управления в основном включает две схемы:

• Управляющий автомат, генерирующий сигналы управления путями данных основываясь на FSD. Эти сигналы включают: сигналы запроса синхронизации и записи в регистры и RAM.

• Механизм останова управляет выполнением команд. Он определяет этап, который в настоящее время выполняет команду и разрешает обновление регистров и RAM.

управляющий автомат должен быть адаптирован к расширенному набору команд, но новые команды не влияют на механизм останова. Тем не менее, конструкция DLX∑ требует нового механизма останова из-за механизма вызова ISR.

|

|

Рисунок 5.11 Механизм останова конструкции последовательной DLX с аппаратурой прерываний

Механизм останова конструкции DLX∑

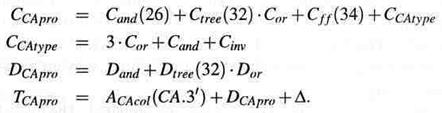

Все еще есть центральная синхронизация CEдля всей конструкции DLX∑. Механизм останова (рисунок 5.11) синхронизирует этапы в round robin fashion основываясь на векторе full[4 : 0]. Этот вектор инициализируется при сбросе и циклически сдвигается по каждому синхроимпульсу CE. Однако, в первом после сброса цикле, выполнение теперь начинается на этапе WB:

Бит разрешения обновления ue.iразрешает обновление выходных регистров этапа i. В течение сброса все флаги разрешения обновления неактивны

ue[4 : 0] = full[4 : 0] /\ CE /\![]() .

.

Переход на процедуру обработки прерываний инициализируется только если флаг jisr.4 установлен и если этап обратной записи полон:

JISR = jisr.4 /\ full[4].

Таким образом, фиктивная команда никогда не может инициализировать переход на ISR.

При сбросе устанавливаются флаги CA.3'[0] и jisr. Однако, переход на ISR может быть инициализирован только в следующем цикле, если глобальные синхроимпульсы CE и синхроимпульсы CA4ce схемы обработки причин также активны при сбросе

CE = (Ibusy NOR Dbusy) \/ reset CA4ce = ue.3 \/ reset.

Как и прежде, синхроимпульсы CEостанавливаются, если одна из памятей занята. Чтобы избежать ненужных остановок флаги занятости рассматриваются только в случае успешного доступа к памяти. Так как блоки памяти никогда не устанавливают эти флаги когда они простаивают, флаги Ibusyи Dbusyмогут быть сгенерированы как

Ibusy = ibusy /\ full.0 /\ (imal NOR ipf) Dbusy = dbusy /\ full.3 /\ (dmal NOR dpf).

Механизм прерываний требует, чтобы стандартная запись в файл регистров или в память отменилась при повторении прерывания. Так как файлы регистров GPR и SPR принадлежат этапу WB, их защита проста. Таким образом, сигналы записи этих двух файлов регистров устанавливаются

GPRw' = GPRw /\ ue.4 /\ (JISR NAND repeat) SPRw' = SPRw /\ ue.4 /\ (JISR NAND repeat).

Для памяти данных защита более сложна, поскольку память DM доступна до обработки причины. Есть только два вида повторных прерываний, а именно два page faults pffи pfls; оба прерывания - немаскируемые. Так как событие, вызывающее прерывание pflsобеспечивается памятью DM, система памяти DM сама должна отменить обновление, если обнаружит отсутствие страницы. Другой тип отсутствия страницы (ev[2] = pff) обнаруживается уже в течение выборки. Поэтому мы переопределяем сигнал записи Dmwкак

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.