|

fanin of the states |

# and length of monomials |

||||

|

fansum |

fanmax |

#M |

lsum |

lmax |

|

|

ex |

26 |

3 |

26 |

189 |

12 |

|

id |

- |

- |

4 |

17 |

10 |

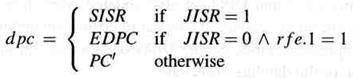

Этапы EX, M и WB управляются только сигналами Мура, которые вычисляются заранее в течение декодирования. Все эти этапы имеют outdegree равное единице. Следовательно, достаточно рассмотреть состояния этапа EX для генерации всех этих управляющих сигналов. Для любого из этих сигналов таблица 5.9 перечисляет их типы (т.е., x, y, или z) и состояния EX в которых они становятся активны.

По строкам раздела 3.4 можно показать, что конструкция DLXΣинтерпретирует расширенный набор команд DLX раздела 5.2 с семантикой задержанного PC. В последовательной конструкции DLX без обработки прерываний любая команда, которая проходит этап k, обновляет только выходные регистры этапов k' > k(лемма 4.3). В конструкции DLX∑, этот dateline критерий применим только для непрерывного выполнения. Если команда Ii прерывается, два программных счетчика PC' и DPC также обновляются, когда Ii находится на этапе обратной записи. Кроме того, в случае прерывания типа repeat обновление памяти данных подавляется. Таким образом, для конструкции DLX∑ мы можем просто сформулировать слабую версию dateline критерия:

|

Лемма 5.9 |

Пусть I∑(k, T') = i. Для любой ячейки памяти или регистра R € out(t) отличного от PC' и DPC, мы имеем

|

|

Если R € {PC', DPC}, тогда R – выходной регистр этапа t= 1 и

|

|

Если выполнение команды Ii не прервано, т.е., если JISRT ' = 0 с I∑(4,T ' ) = i, тогда ri = Riu для любого регистра R.

Если I∑(4, T ' ) = i, тогда IΣ(0, T ' + 1) = i + 1 и лемма 5.9 подразумевает для всех R

RT ' + 1 =Ri.

5.6 Аппаратные средства прерываний с конвейеризацией

Как и в основной конструкции DLX (глава 4), тех же трех изменений достаточно для трансформации подготовленной последовательной конструкции DLX∑в конвейерную конструкцию DLXП. За исключением

• измененной среды PC,

• расширенных аппаратных средств для пересылки результата и обнаружения опасностей, и

• другого механизма останова,

аппаратура DLX∑может быть использована без изменений. Рисунок 5.13 изображает схемотехнику верхнего уровня путей данных DLXП. Теперь подробно рассмотрим измененные окружения.

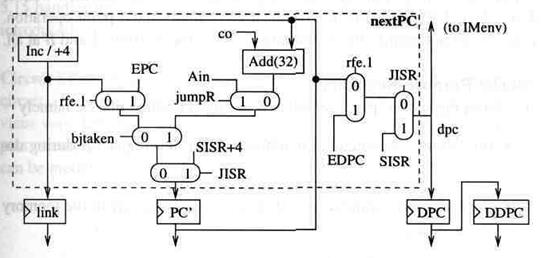

5.6.1 Окружение PC

Рисунок 5.14 изображает окружение PC конструкции DLXП. Единственное изменение в конструкции DLX∑- адрес предоставляемый памяти команд IM. Как и для изменений из главы 4, память IM теперь адресуется входом dpcрегистра DPC а не его выходом.

Однако, задержанный программный счетчик должен быть буферизирован для дальнейшего использования, и таким образом, регистр DPC не может быть отвергнут. Стоимость окружения PCenv и и большинство ее задержек остаются теми же. Два exception PC теперь обеспечиваются схемой пересылки FORW. Таким образом,

|

|

|

|

Рисунок 5 13 Пути данных конвейерной конструкции DLXПс поддержкой прерываний

Рисунок 5.14 Окружение PCenv конструкции DLXП

Изменение окружения PC также влияет на функциональность и задержку окружения памяти команд. Теперь при успешном обращении по чтению память команд обеспечивает слово памяти

IMout = IMword[(dpc[31 : 2]00}].

Время цикла IMenv и накопленная задержка его флагов

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.