6. отсылка результата сложения.

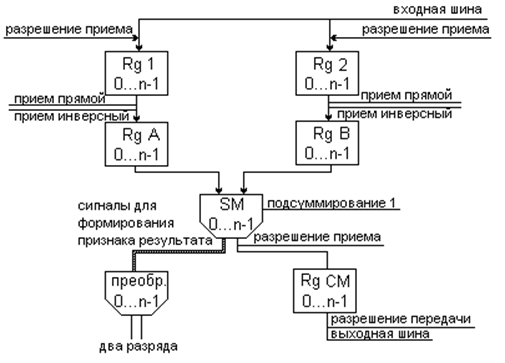

* Состав процессора:

1. устройство управления;

2. арифметико-логическое устройство;

3. блок управляющих регистров.

4. блок контроля и защиты, блок прерываний, блок обмена.

* Структура процессора.

Сложение: если знаки отрицательны, они преобразуются в обратный или дополнительный код.

Вычитание: заменяется сложением, у второго слагаемого автоматически знак меняется на противоположный.

Умножение: последовательное соложение и сдвиги частичных произведений вправо.

Деление: последовательное вычитание и сдвиги частичных остатков влево.

9.3. Структура оперативной памяти.

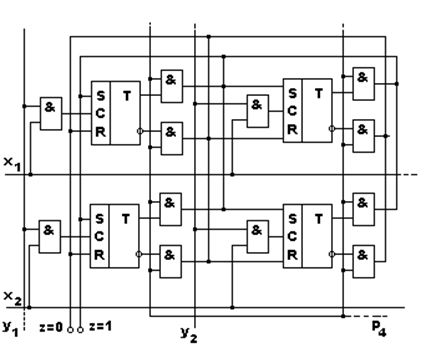

Функциональная схема на RS-триггерах, шины установки 0, записи, чтения, входы, выходы, принцип действия.

Координатные шины хi и yi позволяют выбрать один из элементов подачей питания. В работе запоминающего устройства используют разрядные шины установки триггеров в ноль или единицу и провод разрешения считывания Р4. В режиме записи напряжение подается по одной из шин xi и по одной из шин yi, что подготавливает один из триггеров к приему информации по разрядным шинам. В результате совпадения в одном запоминающем элементе трех сигналов: xi, yi и значения разряда z – происходит запись 1 или 0 в триггер.

В режиме считывания происходит подача питания по шинам xi, yi в выбираемый элемент памяти. На разрядных шинах получают сигналы соответствующего состояния триггера, которое в процессе считывания не изменяется, а следовательно, обеспечивается неразрушающее считывание и нет необходимости в восстановлении информации. Конъюнктор на выходе триггера управляет его подготовкой при совпадении сигналов соответствующих координатных шин xi и yi. Триггер с раздельной установкой в 1 и 0 принимает сигнал по разрядной шине 1 или 0. На выходе триггера – две схемы конъюнкции, управляемые сигналом разрешения считывания и передающие сигналы состояния триггера на разрядные шины запоминающего устройства.

Задание на лабораторную работу

Выполнить тест из каталога …\Met_Doc.9_0\IBM_PU\2_part\7_chap\TEST\… с управляющим модулем pruk3ti.exe, результат предъявить преподавателю.

Информационное обеспечение

\Met_Doc.9_0\IBM_PU\2_posob.doc – файл с текстом данных указаний;

…\7_chap\illust\… - папка иллюстраций, используемых в данной теме;

…\7_chap\TEST\… - папка с тестом;

…\7_chap\1_lect.rtf,

…\7_chap\2_lect.rtf, - файлы с конспектом лекций.

Энциклопедия персонального компьютера. – Компакт-диск электронной библиотеки кафедры САПР.

Литература

1. Каган Б.М., Каневский М.М. Цифровые вычислительные машины и системы. – 1973.

2. Щеголева Л.И., Давыдов А.Ф. Основы вычислительной техники и программирования. – 1981. (Глава 8,9).

Library\MET_DOC\IBM_PU.98\Base_PC\6_chap\liter\Chejgol\...

3. Ефимчик М.К., Шушкевич С.С. Основы радиоэлектроники. - 1986, Глава 9. Основные схемы цифровыхустройств, с. 210-251.

Library\MET_DOC\IBM_PU.98\Base_PC\6_chap\liter\Efimtchik\…

4. Старыгин В.В. Основы автоматики и вычислительной техники. - 1981, Глава 13. Узлы цифровых вычислительных машин, с. 246-271.

Library\MET_DOC\IBM_PU.98\Base_PC\6_chap\liter\Starygin\..

5. Энциклопедия персонального компьютера. – Компакт-диск электронной библиотеки кафедры САПР.

Вопросы для собеседования

1. Цифровые автоматы комбинационного типа: определение, примеры.

2. Сумматор: определение, последовательные и параллельные сумматоры, логические функции, схемная реализация.

3. Одноразрядный сумматор, логические функции, схемная реализация.

4. Полусумматор: определение, логические функции, схемная реализация.

5. Одноразрядный сумматор на двух полусумматорах, схемная реализация.

6. Шифратор: определение, логические функции шифратора, кодирующего двоичные цифры, схемная реализация.

7. Шифратор на элементах Шеффера; схемная реализация.

8. Дешифратор: определение, полный и неполный дешифраторы; таблица истинности для дешифратора десятичных цифр, схемная реализация.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.