* Определение.

Триггером называется цифровой автомат, имеющий два устойчивых состояния и предназначенный для хранения бита информации.

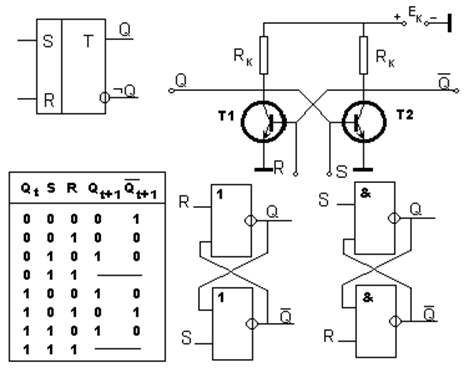

7.1. Асинхронный RS-триггер.

Работа схемы на дискретных

элементах. Если на вход R подать сигнал высокого

уровня, транзистор Т1 будет находиться в открытом состоянии и с выхода Q будет сниматься сигнал низкого уровня (более низкого, чем + Ek). Этот же сигнал будет закрывать транзистор

Т2, и с выхода ![]() получаем сигнал

высокого уровня (примерно +Ek). Появление

сигнала высокого уровня на входе S откроет транзистор

Т2, что закроет транзистор Т1, и на выходе Q будет высокий

уровень напряжения, а на

получаем сигнал

высокого уровня (примерно +Ek). Появление

сигнала высокого уровня на входе S откроет транзистор

Т2, что закроет транзистор Т1, и на выходе Q будет высокий

уровень напряжения, а на ![]() - низкий.

Эти два состояния будут устойчивыми в период отсутствия управляющих сигналов R и S. При подаче сигналов R и S одновременно на два входа в

триггере возникнет неустойчивое состояние.

- низкий.

Эти два состояния будут устойчивыми в период отсутствия управляющих сигналов R и S. При подаче сигналов R и S одновременно на два входа в

триггере возникнет неустойчивое состояние.

Принято считать, что триггер перешел в единичное состояние, если на его выходе Q появился сигнал высокого уровня. Соответственно, за переход в нулевое состояние триггера принято появление на выходе Q сигнала низкого уровня.

Рассмотрим задачу логического проектирования RS-триггера. Его задачей является раздельная установка в состояние 0 и 1. Одновременная подача двух сигналов недопустима и по сути не меняет состояния триггера. Таблица переходов отражает логику работы триггера с учетом его состояния до прихода управляющих сигналов (Qt) и изменения его состояния после действия входных сигналов (Qt+1). Если триггер находился в состоянии нуля и снова принял сигнал установки в нуль, т.е. Rt = 1, когда Qt = 0, то состояние триггера в момент t+1 не изменится. Аналогично будет с сигналом установки единицы, если состояние триггера

Qt = 1.

Запрещенными являются комбинации, вызывающие неопределенное состояние триггера, когда Rt = St =1.

СДНФ: ![]() Пользуясь

методом непосредственных преобразований, получим

Пользуясь

методом непосредственных преобразований, получим ![]() Произведение

Произведение

![]() только при сочетании сигналов

010 имеет единичное значение, т.е. полностью зависит от St,

и поэтому выражение для Qt+1 приводится к

следующему виду:

только при сочетании сигналов

010 имеет единичное значение, т.е. полностью зависит от St,

и поэтому выражение для Qt+1 приводится к

следующему виду: ![]() Преобразуем его:

Преобразуем его:

![]()

![]()

![]()

Аналогично получается функция для

![]() :

:

![]()

![]()

![]()

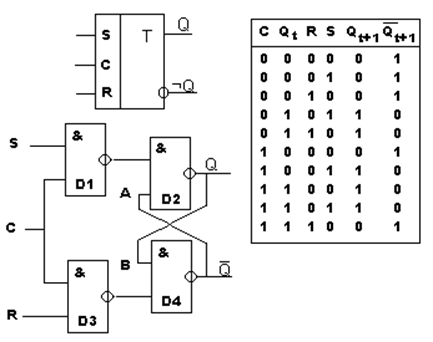

7.2. Синхронный RS-триггер.

Для управления работой синхронного RS-триггера введен дополнительный управляющий (командный) вход С, разрешающий ввод сигналов R и S при наличии синхроимпульса С. Если С = 0, то состояние триггера не меняется, а если С = 1, то его состояние характеризуется приведенной таблицей переходов.

По таблице переходов тактируемого RS-триггера без неопределенных состояний, получим характеристическое уравнение, которое после упрощения имеет вид

![]()

Недостатком этой схемы является то, что помеха по любому входу может одновременно с синхроимпульсом поступать далее в схему. На элементах D2, D4 собран обычный асинхронный RS-триггер, на элементах D1, D3 – дополнительная логика для синхронного управления триггером.

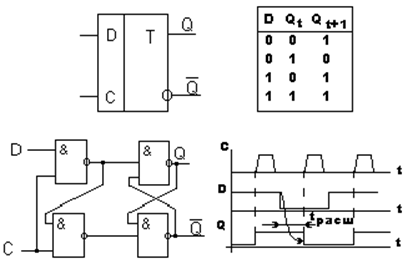

7.3. D-триггер (триггер задержки).

Вход у D-триггера – информационный для установки триггера в 0 или 1. Таблица переходов позволяет составить следующее уравнение:

![]()

Следовательно, сигнал на выходе Qt+1 (в момент времени t+1) повторяет входной сигнал D. Синхронный D-триггер состоит из асинхронного RS-триггера и входной логики. Состояние D-триггера изменяется при поступлении сигналов на входы D и C одновременно. Задержка, а не изменение сигналов 1 и 0, говорит о том, что D-триггер – формирователь сигналов с расширением их на период tрасш. Работа D-триггера иллюстрируется временной диаграммой. Стрелкой показано появление сигнала на выходе Qt+1 через интервал tрасш.

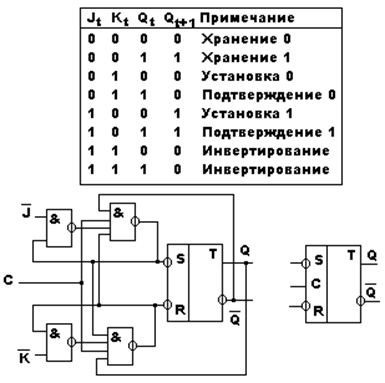

7.4. JK-триггер.

Универсальным по логике работы является JK-триггер. Триггер изменяет свое состояние при совпадении двух единиц на входах J и K. Вход J – для установки 1, а вход К – для установки 0, т.е. аналогично RS-триггеру. Таблица переходов совпадает с таблицей переходов RS-триггера за исключением двух последних строк.

Характеристическое уравнение JK-триггера после минимизации имеет вид

![]() при

при ![]()

Универсальность JK-триггера

позволяет использовать его для построения триггеров любой модификации. Для

получения Т-триггера достаточно объединить входы J и K; для D-триггера принять ![]() , а

, а ![]() .

.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.